FPGA/ASIC Prototyping

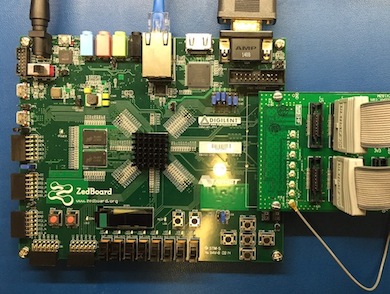

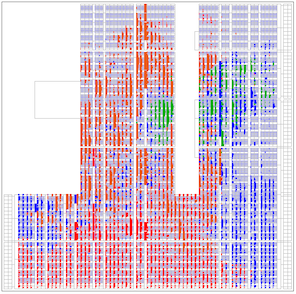

The photo on the left shows our Zedboard setup which includes a Zebax ZX182 FMC card which enables connecting up to 136 channels to an Agilent 1680A logic analyzer for debug and two analog channels to an Agilent MSOX3912A 100MHz mixed-signal oscilloscope for accurately tracking the overall execution time of a microbenchmark. The figure on the right shows the post-place-and-route chip plot for a specific XLOOPS microarchitecture with support for the unordered concurrent loop pattern. The simple pipelined RISC general-purpose processor is shown in green, the four-lane loop-pattern specialization unit is shown in orange, and the 16KB instruction/data caches are shown in blue and red. This prototype uses 32KB of on-FPGA BRAM as main-memory (shown in gray); ongoing work is integrating the prototype with a realistic DRAM main memory system.

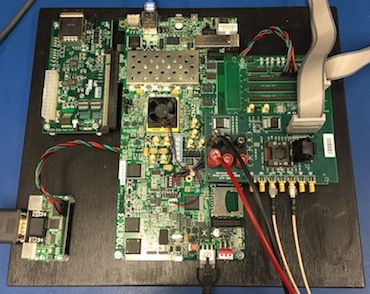

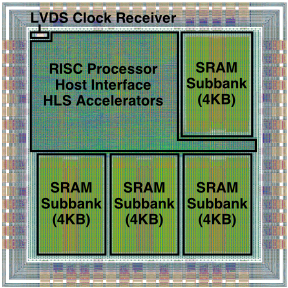

The photo on the left shows our ASIC prototyping platform that is currently under development. We are using a Xilinx ZC706 board augmented with a Xilinx XM105 FMC card for debug and a custom FMC board (ATDB1) designed by our group as part of an NSF CISE Research Infrastructure award. ATDB1 includes an interface to the FPGA on the ZC706 through the FMC connector, a 64-pin QFN test socket, SMA connectors for high-speed clock inputs, banana connectors for source-measurement units, logic analyzer connectors for digital debug, and programmable voltage regulators for generating analog bias voltages. The figure on the right shows the post-place-and-route chip plot for our first ASIC prototype which was taped out in April 2016 on an IBM 130nm process. The 2x2mm 1.3M-transistor chip is designed using our new PyMTL hardware modeling framework and includes a simple pipelined 32-bit RISC processor, custom LVDS clock receiver, 16KB of on-chip SRAM, and application-specific accelerators generated using commercial C-to-RTL high-level synthesis tools. Project was led by Christopher Torng and Moyang Wang with help from Bharath Sudheendra & Nagaraj Murali (physical design), Suren Jayasuriya & Robin Ying (full-custom design), Shreesha Srinath (accelerator design), Mark Buckler (toolflow), and Taylor Prichard (FPGA emulation).