ECE 5745/6745 Complex Digital ASIC Design

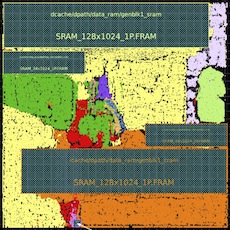

ECE 5745 includes a five-week open-ended design project where small groups of students design, implement, test, and evaluate an interesting technique in computer architecture using functional-, microarchitectural-, register-transfer-, and layout-level modeling. Students use what they have learned in lecture and their experiences working with state-of-the-art computer-aided design (CAD) tools in earlier lab sessions to accurately estimate area, energy, and timing for a variety of different design points. The above images illustrate the layout generated from these CAD tools using the Synopsys 90nm educational standard-cell library for three student projects in 2013. The design on the left is for a processor augmented with a reconfigurable engine for executing multi-instruction "macros". The design in the middle is for a flattened butterfly with one bit of the channels originating from the upper-left-hand router highlighted. The design on the right is for an application-specific accelerator suitable for solving the 0-1 knapsack problem using a branch-and-bound algorithm.

The chip floorplan on the left was the first teaching test chip for ECE 5745 taped out on SkyWater 130nm through the efabless ChipIgnite program. The chip included four projects with 15 students participating: a CRC32 checksum unit implemented using C++ high-level synthesis via Mentor CatapultC, a latency insensitive synthesizable memory implemented in PyMTL3, a 2x2 systolic array multiplier implemented in SystemVerilog, and a greatest common divisor unit implemented in SystemVerilog. Each unit included its own dedicated SPI interface for isolated testing.

For more information about the course see the ECE 5745 webpage.