ECE 4750 Computer Architecture

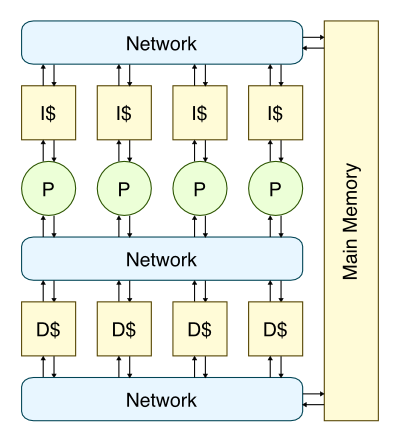

ECE 4750 includes four lab assignments that allow students to incrementally design, implement, test, and evaluate a complete multicore system with an integrated collection of processors, memories, and networks. In the first lab, students implement a fixed-latency and variable-latency iterative multiplier; this lab introduces students to the hardware modeling environment used in the rest of the course. In the second lab, students implement a five-stage pipelined RISC processor and explore two techniques for handling read-after-write dependencies: interlocking and forwarding. Students integrate the iterative latency multiplier from the first lab into their pipelined processor. In the third lab, students implement both a direct-mapped and two-way set-associative blocking cache using a finite-state-machine-based control unit. In the fourth lab, students implement a simple ring interconnection network and then compose this network with the processor and memory implemented in previous labs into the complete quad-core processor shown above. They then implement a serial and parallel sorting application to compare the performance of the serial and multicore processors. For more information about the course see the ECE 4750 webpage.