PyMTL Tutorial:

A Python-Based Framework for

Hardware

Generation, Simulation, and Verification

Co-Located with

the 46th

International Symposium on Computer Architecture

Saturday, June

22nd, 2019 • Phoenix, Arizona

The purpose of this tutorial was to introduce the computer architecture research community to the features and capabilities of the new version of PyMTL, a Python-based hardware generation, simulation, and verification framework. This half-day tutorial was held on Saturday, June 22nd, 2019, co-located with ISCA-46 in Phoenix, AZ. Over forty researchers participated in the tutorial, which included a mix of presentations and hands-on activities.

Why PyMTL? — Computer architecture researchers are increasingly exploring the hardware and software aspects of accelerator-centric architectures, and this has resulted in a trend towards implementing accelerators at the register-transfer level and even fabricating accelerator-centric test chips. However, the conventional wisdom is that designing, implementing, testing, and evaluating RTL accelerators is a complex, time-consuming, and frustrating process. These challenges in the computer architecture research community mirror the challenges faced by commercial, government, and hobbyist hardware designers. These challenges have motivated some design teams to augment or even replace traditional domain-specific hardware description languages (HDLs) with a mix of different high-level hardware generation, simulation, and verification frameworks. PyMTL is a next-generation Python-based framework that unifies hardware generation, simulation, and verification into a single environment. The Python language provides a flexible dynamic type system, object-oriented programming paradigms, powerful reflection and introspection, lightweight syntax, and rich standard libraries. PyMTL builds upon these productivity features to enable a designer to write more succinct descriptions, to avoid crossing any language boundaries for development, testing, and evaluation, and to use the complete expressive power of the host language for verification, debugging, instrumentation, and profiling. The hope is that PyMTL can reduce time-to-paper (or time-to-solution) by improving the productivity of design, implementation, verification, and evaluation.

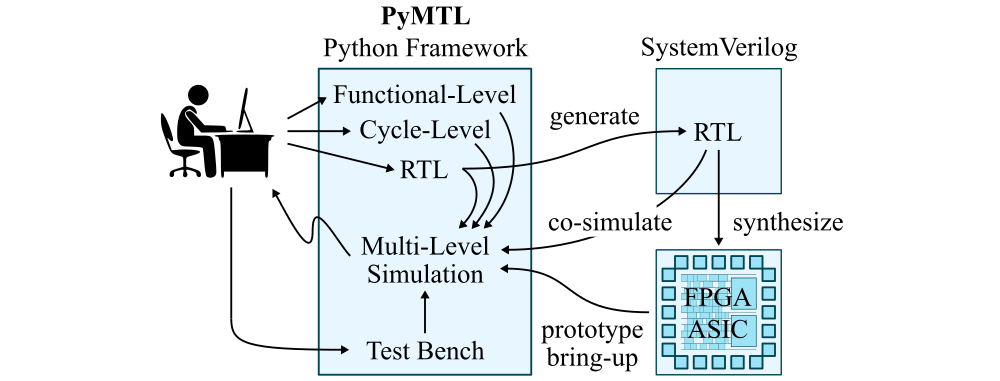

The PyMTL Workflow — A typical workflow using PyMTL is shown above. The designer starts from developing a functional-level (FL) design-under-test (DUT) and test bench completely in Python. Then the DUT is iteratively refined to the cycle level (CL) and register-transfer level (RTL), along with verification and evaluation using Python-based simulation and the same test bench. The designer can then translate a PyMTL RTL model to Verilog and use the same test bench for co-simulation. Note that designers can also co-simulate existing SystemVerilog source code with a PyMTL test bench. The ability to simulate/co-simulate the design in the Python runtime environment drastically reduces the iterative development cycle, eliminates any semantic gap, and makes it feasible to adopt verification methodologies emerging in the open-source software community. Finally, the designer can push the translated DUT through an FPGA/ASIC toolflow and can even reuse the same PyMTL test bench during prototype bringup.

The New Version of PyMTL — This hands-on tutorial introduced participants to the new version of PyMTL. This version of PyMTL maintains some of the best features of the current version including: support for highly paramterized chip generators; a unified framework for functional-, cycle-, and register-transfer level modeling; pure-Python-based simulation; elegant translation of PyMTL RTL to Verilog RTL; and first-class support for co-simulation of PyMTL and Verilog models through Python/Verilator integration. The new version of PyMTL will additionally include: a completely new execution model based on statically scheduled concurrent sequential update blocks; improved simulation performance; first-class support for method-based interfaces; PyMTL passes for analyzing, instrumenting, and transforming PyMTL models; and improved verification methodologies.

Tutorial Objectives

Our objective was to provide attendees with answers to the following questions:

- What kind of research problems can PyMTL help me solve?

- How do I build functional-level, cycle-level, and register-transfer-level models in PyMTL?

- How do I generate Verilog HDL from PyMTL RTL models and push them through an ASIC toolflow?

- How do I create flexible testing harnesses in PyMTL that work across abstraction levels?

- How do I incorporate PyMTL into my existing research flow?

- How do I use existing Verilog IP with PyMTL?

Tutorial Code

The VirtualBox VM used for the tutorial included a complete PyMTL development environment, a set of open-source EDA tools (e.g., Yosys, Graywolf, Qrouter, KLayout), the FreePDK45 physical design kit, and Nangate standard cells. The VirtualBox VM is available for download so that anyone can complete the hands-on activities on their own.

We recommend using VirtualBox v6 or later. You should be able to simply download the OVA file and double click on it to decompress and import the VirtualBox VM. The VirtualBox VM will use about 10GB on your local hard drive. Once the import is complete, you can start the VirtualBox VM by clicking the Start button in VirtualBox. Once fully booted, you will be automatically logged in. If the font is too small, click on Machine > Settings, and change the scale Factor in the Display tab. The activities will require you to work at the command line. Double click the Terminal icon on the desktop, to launch a terminal you can use.

The following links enabled participants to browse the previous version of PyMTL, the new version of PyMTL, and the PyMTL designs used in the tutorial:

- PyMTLv2 Kernel and Standard Library Code

- PyMTLv3 Kernel and Standard Library Code

- PyMTL Tutorial Design Code

Tutorial Schedule

| 12:30 | – | 1:45 | pm | Lunch | |

| 1:45 | – | 2:00 | pm | Virtual Machine Installation and Setup

While attendees are welcome to simply listen during the tutorial,

we strongly encourage attendees to engage in the hands-on

activities throughout the tutorial. Attendees should arrive at

1:45pm so that there is time to install and setup the virtual

machine for the hands-on activities.

|

|

| 2:00 | – | 2:15 | pm | Presentation: PyMTL Overview | slides |

| 2:15 | – | 2:55 | pm | Part 1: PyMTL Basics

In this part, we will focus on the PyMTL basics which serve as the

foundation for productive multi-level modeling and VLSI design. We

will start by learning the basics of modeling fixed-bitwidth types

in Python and writing simple unit tests using py.test. We

will then learn about update blocks, wires, value ports, method

ports, and interfaces.

|

slides |

| 2:55 | – | 3:30 | pm | Part 2: Introduction to Multi-Level Modeling with PyMTL

In this part, we will explore a hardware implementation of a

variant of Fletcher's checksum algorithm. This part will enable

attendees to build off of the fundamentals from the previous part

to understand basic PyMTL syntax, constructs, and semantics

including PyMTL's emphasis on concurrent structural modeling. We

will implement a functional-level (FL) model of the algorithm and

use directed testing to verify its functionality. We will then

implement both a cycle-level (CL) and register-transfer-level (RTL)

model of a checksum hardware unit. We will then translate our RTL

model into Verilog and push it through an open-source EDA toolflow

to generate layout using the open FreePDK45 technology and Nangate

standard cells. We will end by exploring techniques for multi-level

verification with an emphasis on property-based random testing.

|

slides |

| 3:30 | – | 4:00 | pm | Coffee Break | |

| 4:00 | – | 4:45 | pm | Part 3: Modeling Processors in PyMTL

In this part, we will explore FL, CL, and RTL models for a basic

RISC-V processor with support for 10 instructions. This part will

enable attendees to gain additional understanding of multi-level

modeling in the context of a more complicated model. We will add a

new AND instruction at each level of abstraction, and we will write

a new assembly test generated and assembled with Python for

verifying this AND instruction. We will end by using a PyMTL

simulator to evaluate the performance of an assembly implementation

of Fletcher's checksum algorithm.

|

slides |

| 4:45 | – | 5:30 | pm | Part 4: Multi-Level Composition in PyMTL

In this part, we will explore composing the work done in the

previous two parts to create a simple processor+accelerator system.

This part will enable attendees to understand multi-level

composition where models at different levels of abstraction can be

arbitrarily mixed. We will start by exploring how to wrap the

hardware unit from part 1 to provide an register-mapped accelerator

interface. We will then compose this accelerator with the processor

from part 2 to create a multi-level simulator. Both the processor

and accelerator have FL, CL, and RTL implementations, so we will

experiment with all nine possible compositions and we will compare

the performance on a Fletcher checksum benchmark both with and

without the accelerator. We will end by translating an RTL model of

the processor+accelerator system into Verilog and pushing it

through an open-source EDA toolflow to generate layout using the

open FreePDK45 technology and Nangate standard cells.

|

slides |

Tutorial Prerequisites

We expect attendees that wish to engage in the hands-on activities throughout the tutorial to have some experience with Linux-based software and/or hardware development (e.g., working at the Linux command line, using a Linux text editor such as emacs, vim, or gedit). Attendees should bring a laptop and charger for the tutorial. Each attendee will receive a USB flash drive containing: VirtualBox installers for Windows, Mac OS X, Linux; a CentOS-based virtual machine containing all of the code and tools for the tutorial; and PDFs for all of the tutorial slides and handouts. While it is certainly possible to install PyMTL on your own UNIX-like laptops, we encourage attendees to use our virtual machine to simplify the setup. Attendees will need approximately 5GB of free space in order to install and use the VirtualBox virtual machine.

Tutorial Organizers

- Christopher Batten, Cornell University

- Shunning Jiang, Cornell University

- Christopher Torng, Cornell University

- Yanghui Ou, Cornell University

- Peitian Pan, Cornell University

PyMTL Publications

- S. Jiang, B. Ilbeyi, C. Batten. "Mamba: Closing the Performance Gap in Productive Hardware Development Frameworks." 55th ACM/IEEE Design Automation Conf. (DAC-55), June 2018. [link,pdf]

- D. Lockhart, G. Zibrat, C. Batten. "PyMTL: A Unified Framework for Vertically Integrated Computer Architecture Research." 47th ACM/IEEE Int'l Symp. on Microarchitecture (MICRO-47), Dec. 2014. [link,pdf]

- S. Jiang, C. Torng, C. Batten. "An Open-Source Python-Based Hardware Generation, Simulation, and Verification Framework. First Workshop on Open-Source EDA Technology (WOSET'18) held in conjunction with ICCAD-37, Nov. 2018. [link,pdf]

- C. Torng, S. Jiang, K. Al-Hawaj, I. Bukreyev, B. Ilbeyi, T. Ta, L. Cheng, J. Puscar, I. Galton, C. Batten. "A New Era of Silicon Prototyping in Computer Architecture Research." RISC-V Day Workshop held in conjunction with MICRO-51, Oct. 2018. [link,pdf]

- C. Torng, M. Wang, B. Sudheendra, N. Murali, S. Jayasuriya, S. Srinath, T. Pritchard, R. Ying, C. Batten. "Experiences Using a Novel Python-Based Hardware Modeling Framework for Computer Architecture Test Chips." 28th ACM/IEEE Symp. on High-Performance Chips (HOTCHIPS-28) Student Poster Session, Aug. 2016. [link,pdf]

Tutorial Sponsors

Research and development for the PyMTL project is funded in part by NSF CRI Award #1512937, NSF SHF Award #1527065, the Defense Advanced Research Projects Agency through a DARPA POSH Award #FA8650-18-2-7852, and by the Center for Applications Driving Architectures (ADA), one of six centers of JUMP, a Semiconductor Research Corporation program co-sponsored by DARPA.