Cornell University

School of Electrical and Computer Engineering

ECE 6745 Complex Digital ASIC Design

Spring 2026

Prof. Christopher Batten

219 Phillips Hall • Tuesday and Thursday • 1:25–2:40pm

home | syllabus | staff | schedule | readings | handouts | resources

This course aims to provide a strong foundation for students to understand the principle and practice of designing, implementing, testing, and evaluating complex standard-cell ASIC chips using automated state-of-the-art electronic design automation (EDA) tools. This course is at the intersection of computer architecture, digital circuits, and EDA and is suitable for students pursuing careers in both research and industry. For students pursuing research topics in computer architecture, the course will provide deeper insight into critical physical design issues for future computing systems, while for students pursuing research topics in digital circuits, the course will provide system-level insight into future large-scale chip designs. For students pursuing a career in the chip-design industry, the course will provide valuable design experience from architecture to digital circuits.

The course is structured around three projects each of which is 4-5 weeks long and completed in groups of 2-3 students.

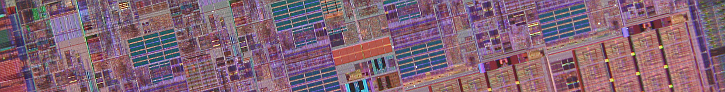

- Project 1: TinyFlow Tape-Out — Students will build their own TinyFlow, a very simple standard-cell-based flow. They will develop four standard cells in TSMC 180nm and the corresponding standard cell behavioral, schematic, layout, extracted schematic, front-end, and back-end views. They will then implement simple algorithms for synthesis (technology mapping via tree covering, static timing analysis) and place-and-route (simulated annealing, 3D maze routing). Finally they will combine this work with open-source Verilog RTL and gate-level simulators and an open-source LVS/DRC tool to create the complete TinyFlow. Even though their TinyFlow will only support a very small combinational subset of Verilog, this project still gives students a unique hands-on opportunity to appreciate every step required in more sophisticated commercial tools. Each group will create a tiny block using their TinyFlow and these blocks will be aggregated into a single unified tape-out on the TSMC 180nm technology node.

- Project 2: Accelerator Tape-Out — Students will leverage what they learned in the first project to transition to using a commercial standard-cell library and commercial electronic design automation tools for simulation, synthesis, place-and-route, static-timing analysis, power analysis, design rule checking (DRC), and layout-vs-schematic checking (LVS). Students will develop a simple accelerator in Verilog RTL and evaluate the potential benefit of using this accelerator in the context of a RISC-V processor. Students will then combine just their accelerator with an SPI interface and use the commercial library and tools to turn this accelerator+SPI into complete chip layout in TSMC 180nm. Students will need to navigate many practical issues associated with a real tape-out including packaging, chip I/O, clock tree synthesis, fixing setup and hold time violations, sign-off timing analysis, DRC and LVS, seal ring insertion, etc. Students will upload their designs for fabrication at TSMC and then test their chips in the lab through a separate 1-credit chip testing class offered in Fall 2026.

- Project 3: System-on-Chip Tape-In — Owing to the small silicon area, the tape-out in the second project will have to be relatively simple. In the final project, students will be able to explore a more complex system-on-chip using everything they have learned in the first two projects. Students will have access to commercial SRAM memory compilers and since this final project will not be taped out, they can use much more area than is feasible in the second project. Students are free to explore any design they wish including advanced processor, memory, and/or network microarchitecture as well as various accelerators.