# EVOLUTIONARY HARDWARE SPECIALIZATION FOR MODERN VECTOR AND MATRIX ARCHITECTURES

A Dissertation

Presented to the Faculty of the Graduate School

of Cornell University

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by Tuan Quang Ta August 2023 © 2023 Tuan Quang Ta ALL RIGHTS RESERVED

## EVOLUTIONARY HARDWARE SPECIALIZATION FOR MODERN VECTOR AND MATRIX ARCHITECTURES

Tuan Quang Ta, Ph.D. Cornell University 2023

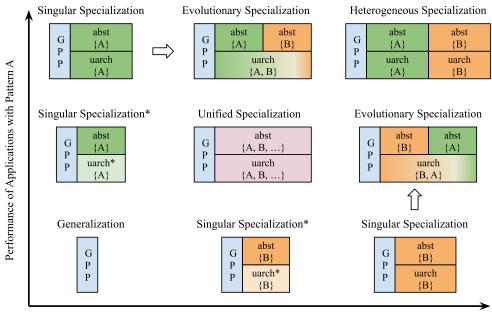

With the slowdown of Moore's Law and the end of Dennard Scaling, computer architects have embraced *specialization* as the main way forward for continuing performance and efficiency growth previously made through traditional technology scaling. Specialization comes in several forms including *application specific specialization, domain specific specialization,* and *parallel pattern specific specialization*. This emergence of hardware specialization has pushed the chip industry towards integrating a *sea of heterogeneous specialized hardware units*, each with its own specialized program abstraction, into a single system on chip (SoC). However, given certain area, power, and budget constraints, there is limited room for the number of specialized hardware units possibly integrated into an SoC. One viable solution is to unify multiple kinds of specialization under the same program abstraction and in the same hardware (e.g., GPGPUs). This unifying approach essentially lowers area costs by trading off the optimality of program abstractions and hardware implementations for individual program patterns.

In this thesis, I explore another specialization approach called *evolutionary specialization* that supports multiple types of specialization in the same hardware. The evolutionary specialization refers to starting from an optimal abstraction and micro-architecture for one program pattern and gradually adding a minimal set of hardware changes to the existing micro-architecture to support additional program patterns without changing their optimal abstractions. The thesis makes a case for the evolutionary specialization through two novel architectures: big.VLITTLE and SparseZipper. The big.VLITTLE architecture evolves a multi-little-core system to efficiently support both single-program multiple-data (SPMD) and single-instruction multiple-data (SIMD) program patterns. The SparseZipper architecture minimally extends a modern matrix architecture specialized for a dense general matrix multiplication (GEMM) pattern to support a sparse GEMM pattern.

#### **BIOGRAPHICAL SKETCH**

Tuan Ta was born on September 24, 1992 to Ta Dac Ngo and Nguyen Thi Thu Van. He is the youngest child with a sister six years older. During his childhood, Tuan showed his interests in science and technology, especially math and programming. He picked up basic programming skills in Pascal and then C languages in his middle school. He joined Hanoi-Amsterdam High School for the Gifted and took advanced math and programming classes.

Tuan was accepted to the Hanoi University of Science and Technology to study computer and information sciences. During his first year at the university, he became interested in pursuing higher education outside Vietnam to satisfy his desire to explore the world. He started applying for colleges in the US and got accepted to the University of Mississippi with a full-tuition scholarship. After the first year of struggling with drastic cultural differences, he adapted to the new environment and started making good academic progress. In his sophomore year, Tuan joined a research group led by Professor Byunghyun Jang. This undergraduate research experience set him up for his later academic career and a strong interest in computer architecture.

Tuan was admitted to the Ph.D. program in the School of Electrical and Computer Engineering at Cornell University in 2017, and he joined Professor Christopher Batten's group. Throughout the next six years, he was fortunate to collaborate with smart and hardworking students in the group to advance state-of-the-art research in the field of computer architecture. He initially worked on a smart sharing architecture led by Dr. Shreesha Srinath, a heterogeneous cache coherence project led by Dr. Moyang Wang, and then EVE project led by Dr. Khalid Al-Hawaj. Tuan gained first-hand experience of taping out a chip in CIFER project led by a research group at Princeton University. He then took the lead in two projects: big.VLITTLE and SparseZipper that constitute the main portion of this dissertation.

In his free time during the Ph.D. journey, Tuan enjoyed playing badminton. During the tough COVID years, he also learned how to play other racket sports including squash, tennis, pickle ball, and ping pong. He was interested in checking out many beautiful hiking trails and waterfalls that the nature in upstate New York offers.

Tuan is very thankful for his Ph.D. experience despite numerous challenges during the journey. The great mentorship from his advisor, invaluable moments with his friends, and most importantly the endless support from his family helped him persist throughout the six years of his Ph.D. journey and learn how to become a good person and researcher. This document is dedicated to my parents and my beloved wife Thuy Nguyen.

#### ACKNOWLEDGEMENTS

This dissertation would not have been possible without the support of many people in my life. I am thankful for all encouragement, advice, and help that I received during my long Ph.D. journey.

First and foremost, I would like to thank my parents for always being on my side whenever I go through difficulties in life and encouraging me to persist and complete my "decade-long" study. Despite being far away from home, I can always feel your support in our daily phone calls. My parents have taught me the importance of hard work in achieving any meaningful goals in life. I thank my wife, Thuy Nguyen, for being with me through happiest and toughest moments during my entire study in the US. My journey in a foreign country would have not been meaningful without you going with me in the past 11 years. I am thankful for our marriage, and I will continue making you feel happy in the future. I would like to thank my sister, Trang Ta, for understanding and supporting my decisions in life.

This dissertation would not have been possible without the guidance of my committee: Professor Christopher Batten, Professor José Martínez, and Professor Adrian Sampson. My great advisor, Professor Christopher Batten, has taught me the importance of low-level details in doing good research, challenged me to stand on my own feet to argue for my research ideas, put me out of my comfort zone by assigning me to lead a team in a tapeout project, and trusted me to finish the final stretch of my Ph.D. journey. More importantly, his honest and constructive criticisms made me become a better researcher. I would like to acknowledge the rest of my committee: Professor José Martínez and Professor Adrian Sampson for your feedback to improve my research and comments challenging me to think differently about my research.

I am deeply thankful for working with my colleagues in BRG group. Shreeshra Srinath convinced me about the future of RISC-V and always challenged me to look for ambitious research ideas. Christopher Torng taught me how to organize my research and inspired me to make it more productive using automation tools and effective note taking. Moyang Wang taught me about work-stealing runtime and not giving up until the last moment before a paper submission deadline. Shunning Jiang taught me how to use PyMTL, and I am thankful for our discussions about the BRG in-order core design. I appreciate my collaborations with Khalid Al-Hawaj in various projects. He told me about common pitfalls in a Ph.D. journey and helped me through important milestones. He was patient with me explaining ideas and willing to provide constructive criticisms to make them better. I truly enjoyed working with him in the second half of my Ph.D. journey. Lin Cheng always has his magic in finding out tricky bugs. Peitian Pan, I enjoyed discussing research ideas with you and thank you for helping with using PyMTL. I would like to acknowledge Yanghui Ou for his generosity and kindness in helping me in various projects. I hope the last part of your Ph.D. will go smoothly. Nick Cebry, I enjoyed working with you in the big.VLITTLE project. Hopefully, your collaborations with me and Khalid help you later in your Ph.D. process. I am thankful for working with Dr. Shady Agwa and his deep VLSI knowledge. I would also like to thank Courtney Golden for helping with the big.VLITTLE project. I hope you will do well in your own Ph.D. journey at MIT. I thank Eric Hall, Xiaoyu Yan, and Eric Tang for helping with various projects in this dissertation.

I would like to thank my collaborators. I appreciate Ang Li and August Ning for hosting me at Princeton University to test out the CIFER chip and helping me evaluate it remotely. I enjoyed our conversations at conferences, and hopefully I can see you in another conference in the near future. I thank the rest of CIFER team for making the chip tapeout happen. I would also like to acknowledge my collaborators at Arm Research: Alex Rico for mentoring me during my internship, José Joao for giving me comments on the big.VLITTLE project, Tiago Muck for sharing a pre-published version of CHI implementation in gem5, and Joshua Randall for mentoring and helping me in the SparseZipper project.

I would like to thank my friends at the Computer Systems Laboratory (CSL). CSL introduced me to a wonderful group of people to share ideas, have meals together, and enjoy life after work. Sachille Atapattu and Helena Caminal, I enjoyed our time together hiking, kayaking, cooking, and having fun. Philip Bedoukian, although we could not schedule our B-exam on the same day, I will miss our weekend meals at Asia cuisine. Khalid Al-Hawaj, Yichi Zhang, Chanhui Deng, and Professor Zhiru Zhang are my badminton "buddies" from CSL.

I also would like to thank my friends outside CSL for great moments outside work during my Ph.D. process. Thank Chethani Athukorala and Sunil Atapattu for being my good friends. I thank the badminton team including Akula Sai Pratyush, Chao-Ming Jian, Ray Yu, Kaushalendra Singh, Yun Liu, Jin, and Jun Lin for great badminton games and early morning training sessions. Playing badminton with you helped me remain sane during my Ph.D. journey.

I would like to thank all people that helped me get to where I am today. I thank Professor Byunghyun Jang for getting me started in doing research and strongly supporting me throughout the whole process. My time in the HEROES group at the University of Mississippi was wonderful. I would like to acknowledge Dr. David Troendle for teaching so many things about hardware, system programming, and operating systems. You are my role model for me to keep learning, working hard, and being creative regardless of age. I would like to thank Dr. Kyoshin Choo for helping me in my first ever research project. I thank my mentors at the National Center for Atmospheric Research for introducing me to scientific programming during my first internship. I thank Bradford Beckmann and Anthony Gutierrez for mentoring me during my time at AMD Research. I would like to thank my English teacher, Nghiem Ngo, for inspiring me to look for opportunities outside Vietnam and guiding me to apply for colleges in the US.

This work was supported in part by NSF PPoSS Award #2118709, NSF SHF Award #2008471, DARPA POSH Award #FA8650-18-2-7852, and the Center for Applications Driving Architectures (ADA), one of six centers of JUMP, a Semiconductor Research Corporation program co-sponsored by DARPA, and equipment, tool, and/or physical IP donations from Intel, Xilinx, Synopsys, Cadence, and ARM. The U.S. Government is authorized to reproduce and distribute reprints for Government purposes notwithstanding any copyright notation theron. Any opinions, findings, and conclusions or recommendations expressed in this publication are those of the author(s) and do not necessarily reflect the views of any funding agency.

|   | Dedi<br>Ack<br>Tabl<br>List<br>List                                                                                                           | ication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                            |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Intr                                                                                                                                          | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                          |

|   | 1.1                                                                                                                                           | Specialization for SPMD and SIMD Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2                                                                                                                                                          |

|   |                                                                                                                                               | 1.1.1     Specialization for SPMD Pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2                                                                                                                                                          |

|   |                                                                                                                                               | 1.1.2       Specialization for SIMD Pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3                                                                                                                                                          |

|   |                                                                                                                                               | 1.1.2     Specialization for Shirls Fatterin       1.1.3     The Need for Both SPMD and SIMD Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4                                                                                                                                                          |

|   | 1.2                                                                                                                                           | Specialization for Dense and Sparse GEMM Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5                                                                                                                                                          |

|   | 1.2                                                                                                                                           | 1.2.1       Specialization for Dense GEMM Pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5                                                                                                                                                          |

|   |                                                                                                                                               | 1.2.1       Specialization for Dense GEMM Pattern         1.2.2       Specialization for Sparse GEMM Pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6                                                                                                                                                          |

|   |                                                                                                                                               | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                            |

|   | 1.0                                                                                                                                           | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8                                                                                                                                                          |

|   | 1.3                                                                                                                                           | Approaches to Supporting Multiple Types of Specialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8                                                                                                                                                          |

|   | 1.4                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12                                                                                                                                                         |

|   | 1.5                                                                                                                                           | Collaboration and Funding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13                                                                                                                                                         |

| 2 | CIF                                                                                                                                           | ER: A Chip Prototype Using Heterogeneous Specialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                                                                                                                         |

|   |                                                                                                                                               | En a chip i fototype Oshig fietel ogeneous opecialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                            |

| 2 |                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                            |

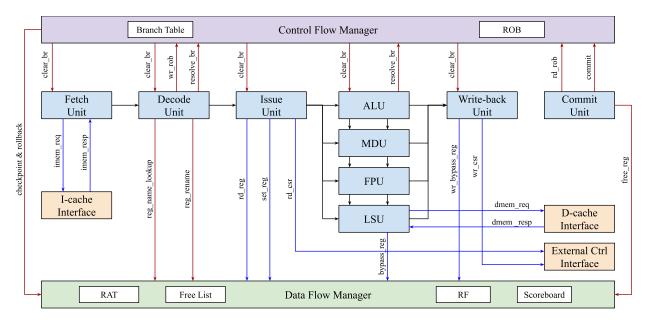

| 2 | 2.1                                                                                                                                           | CIFER Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16                                                                                                                                                         |

| 2 |                                                                                                                                               | CIFER Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16<br>17                                                                                                                                                   |

| 2 |                                                                                                                                               | CIFER Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16<br>17<br>18                                                                                                                                             |

| 2 |                                                                                                                                               | CIFER Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16<br>17<br>18<br>21                                                                                                                                       |

| 2 | 2.1                                                                                                                                           | CIFER Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16<br>17<br>18<br>21<br>22                                                                                                                                 |

| 2 | <ul><li>2.1</li><li>2.2</li></ul>                                                                                                             | CIFER Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16<br>17<br>18<br>21<br>22<br>22                                                                                                                           |

| 2 | <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul>                                                                                                 | CIFER Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16<br>17<br>18<br>21<br>22<br>22<br>23                                                                                                                     |

| 2 | <ul><li>2.1</li><li>2.2</li></ul>                                                                                                             | CIFER Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16<br>17<br>18<br>21<br>22<br>22                                                                                                                           |

|   | <ul><li>2.1</li><li>2.2</li><li>2.3</li><li>2.4</li></ul>                                                                                     | CIFER Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16<br>17<br>18<br>21<br>22<br>22<br>23<br>26                                                                                                               |

| 3 | 2.1<br>2.2<br>2.3<br>2.4<br>Cycl                                                                                                              | CIFER Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <ol> <li>16</li> <li>17</li> <li>18</li> <li>21</li> <li>22</li> <li>22</li> <li>23</li> <li>26</li> <li>28</li> </ol>                                     |

|   | 2.1<br>2.2<br>2.3<br>2.4<br><b>Cycl</b><br>3.1                                                                                                | CIFER Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16<br>17<br>18<br>21<br>22<br>23<br>26<br><b>28</b><br>28                                                                                                  |

|   | 2.1<br>2.2<br>2.3<br>2.4<br>Cycl                                                                                                              | CIFER Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16<br>17<br>18<br>21<br>22<br>23<br>26<br><b>28</b><br>28<br>28<br>29                                                                                      |

|   | 2.1<br>2.2<br>2.3<br>2.4<br><b>Cycl</b><br>3.1                                                                                                | CIFER Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <ol> <li>16</li> <li>17</li> <li>18</li> <li>21</li> <li>22</li> <li>22</li> <li>23</li> <li>26</li> <li>28</li> <li>29</li> <li>30</li> </ol>             |

|   | 2.1<br>2.2<br>2.3<br>2.4<br><b>Cycl</b><br>3.1                                                                                                | CIFER Architecture       2.1.1       Linux-Capable Multicore Tile       2.1.2         2.1.2       TinyCore Tile       2.1.3       Embedded FPGA       2.1.4         2.1.4       Heterogeneous Cache Coherence       2.1.4       Heterogeneous Cache Coherence       2.1.4         Verification Methodology       2.1.4       Heterogeneous Cache Coherence       2.1.4       Heterogeneous Cache Coherence       2.1.4         Verification Methodology       2.1.4       Heterogeneous Cache Coherence       2.1.4       1.4         Verification       2.1.4       Heterogeneous Cache Coherence       2.1.4       1.4       1.4         Verification       2.1.4       Heterogeneous Cache Coherence       2.1.4       1.4       1.4         Introduction       2.1.4       Adding Multi-Core RISC-V Support to gem5       2.1.4       1.4       1.4         3.2.1       Adding Threading System Call Support       2.1.4       1.4       1.4       1.4 | <ol> <li>16</li> <li>17</li> <li>18</li> <li>21</li> <li>22</li> <li>23</li> <li>26</li> <li>28</li> <li>29</li> <li>30</li> <li>32</li> </ol>             |

|   | 2.1<br>2.2<br>2.3<br>2.4<br><b>Cycl</b><br>3.1                                                                                                | CIFER Architecture .       2.1.1 Linux-Capable Multicore Tile .         2.1.2 TinyCore Tile .       2.1.2 TinyCore Tile .         2.1.3 Embedded FPGA .       2.1.3 Embedded FPGA .         2.1.4 Heterogeneous Cache Coherence .       2.1.4 Heterogeneous Cache Coherence .         Verification Methodology .       2.1.4 Evaluation .         Conclusion .       2.1.4 Evaluation .         Re-Level Modeling of Multi-Core RISC-V Systems         Introduction .       2.1.4 Evaluation .         Adding Multi-Core RISC-V Support to gem5 .       2.1.4 Evaluation .         3.2.1 Adding Threading System Call Support .       3.2.2 Adding Synchronization Instruction Support .         Support Functional Validation .       3.2.1 Figure .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ol> <li>16</li> <li>17</li> <li>18</li> <li>21</li> <li>22</li> <li>23</li> <li>26</li> <li>28</li> <li>29</li> <li>30</li> <li>32</li> <li>34</li> </ol> |

|   | <ul> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>Cycl</li> <li>3.1</li> <li>3.2</li> </ul>                                        | CIFER Architecture       2.1.1       Linux-Capable Multicore Tile         2.1.2       TinyCore Tile       2.1.2         2.1.3       Embedded FPGA       2.1.3         2.1.4       Heterogeneous Cache Coherence       2.1.4         Verification Methodology       2.1.4         Evaluation       2.1.4         Conclusion       2.1.4         Re-Level Modeling of Multi-Core RISC-V Systems         Introduction       2.1.4         Adding Multi-Core RISC-V Support to gem5         3.2.1       Adding Threading System Call Support         3.2.2       Adding Synchronization Instruction Support         Functional Validation       2.1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <ol> <li>16</li> <li>17</li> <li>18</li> <li>21</li> <li>22</li> <li>23</li> <li>26</li> <li>28</li> <li>29</li> <li>30</li> <li>32</li> </ol>             |

|   | <ul> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>Cycl</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> </ul>                           | CIFER Architecture       2.1.1       Linux-Capable Multicore Tile         2.1.2       TinyCore Tile       2.1.2         2.1.3       Embedded FPGA       2.1.3         2.1.4       Heterogeneous Cache Coherence       2.1.4         Verification Methodology       2.1.4         Verification Methodology       2.1.4         Evaluation       2.1.4         Re-Level Modeling of Multi-Core RISC-V Systems         Introduction       2.1.4         Adding Multi-Core RISC-V Support to gem5         3.2.1       Adding Threading System Call Support         3.2.2       Adding Synchronization Instruction Support         Functional Validation       2.1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ol> <li>16</li> <li>17</li> <li>18</li> <li>21</li> <li>22</li> <li>23</li> <li>26</li> <li>28</li> <li>29</li> <li>30</li> <li>32</li> <li>34</li> </ol> |

|   | <ul> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>Cycl</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> </ul>              | CIFER Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16<br>17<br>18<br>21<br>22<br>23<br>26<br><b>28</b><br>28<br>29<br>30<br>32<br>32<br>34<br>35                                                              |

|   | <ul> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>Cycl</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> </ul> | CIFER Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16<br>17<br>18<br>21<br>22<br>23<br>26<br><b>28</b><br>28<br>29<br>30<br>32<br>34<br>35<br>37                                                              |

### TABLE OF CONTENTS

| 4 | big.' | LITTLE: Evolutionary Specialization for Modern Vector Architectures   | 44  |

|---|-------|-----------------------------------------------------------------------|-----|

|   | 4.1   | Introduction                                                          | 44  |

|   | 4.2   | The Resurgence of Vector Architectures                                | 46  |

|   |       | 4.2.1 Long-Vector Architectures                                       | 47  |

|   |       | 4.2.2 Packed-SIMD Architectures                                       | 47  |

|   |       | 4.2.3 Next-generation Vector Architectures                            | 48  |

|   | 4.3   | big.VLITTLE Architectures                                             | 49  |

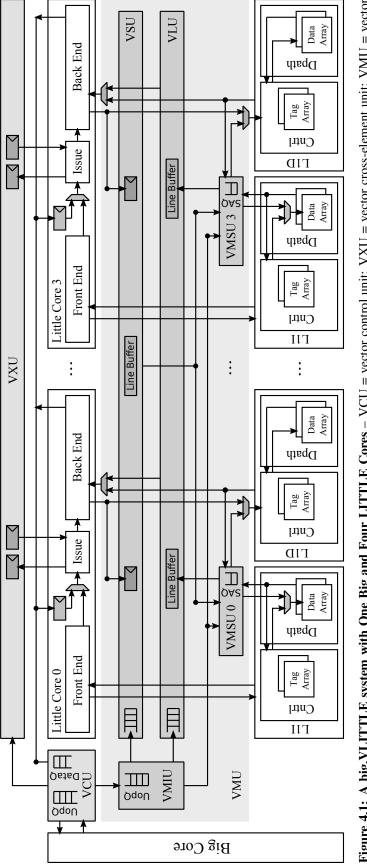

|   |       | 4.3.1 Architectural Overview                                          | 49  |

|   |       | 4.3.2 Vector Control Support                                          | 51  |

|   |       | 4.3.3 Reconfigurable Little Cores                                     | 53  |

|   |       | 4.3.4 Cross-Element Instruction Support                               | 54  |

|   |       | 4.3.5 Reconfigurable Cache Subsystem                                  | 55  |

|   | 4.4   | Evaluation Methodology                                                | 58  |

|   |       | 4.4.1 Simulated Systems                                               | 59  |

|   |       | 4.4.2 Application Benchmarks                                          | 63  |

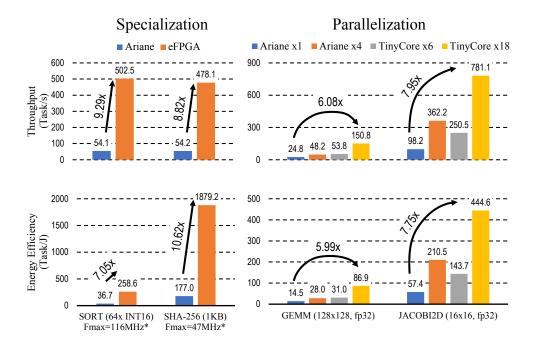

|   | 4.5   | Performance Evaluation                                                | 64  |

|   |       | 4.5.1 Overall Performance                                             | 64  |

|   |       | 4.5.2 Reconfigurable Compute Pipeline                                 | 67  |

|   |       | 4.5.3 Performance Impacts of Data Buffering                           | 68  |

|   | 4.6   | Area Evaluation                                                       | 69  |

|   | 4.7   | Power & Energy Evaluation                                             | 71  |

|   |       | 4.7.1 Qualitative Power and Energy Efficiency Analysis                | 71  |

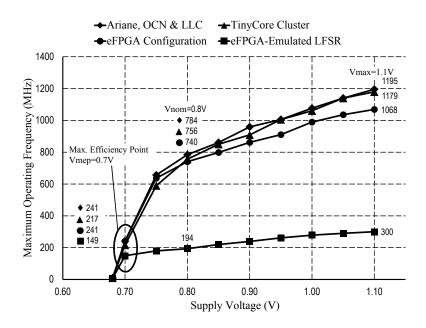

|   |       | 4.7.2 Voltage/Frequency Scaling Design Space Exploration              | 72  |

|   | 4.8   | Related Work                                                          | 75  |

|   | 4.9   | Conclusion                                                            | 77  |

| 5 | Spar  | seZipper: Evolutionary Specialization for Modern Matrix Architectures | 78  |

|   | 5.1   | Introduction                                                          | 78  |

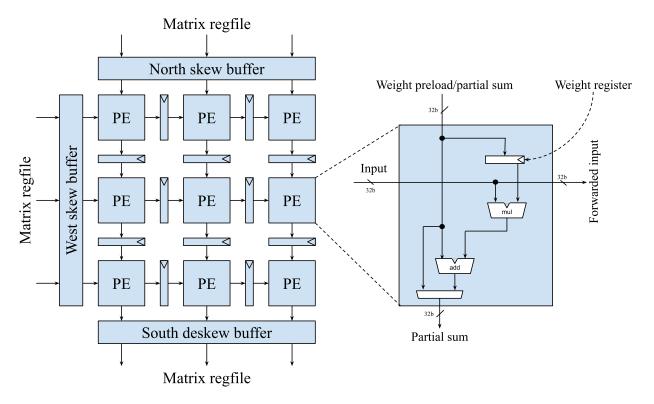

|   | 5.2   | Background: Modern Matrix Architectures                               | 80  |

|   | 5.3   | Background: Sparse General Matrix Multiplication                      |     |

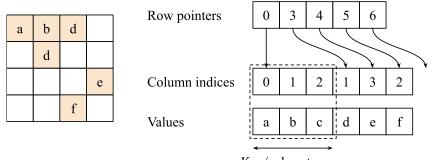

|   |       | 5.3.1 Sparse Matrix Formats                                           |     |

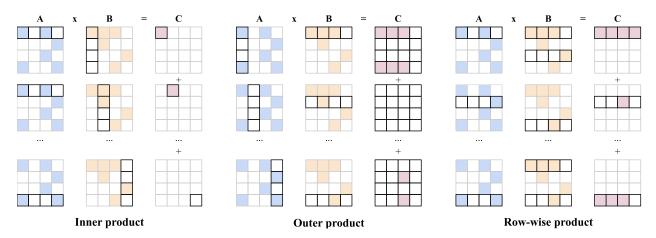

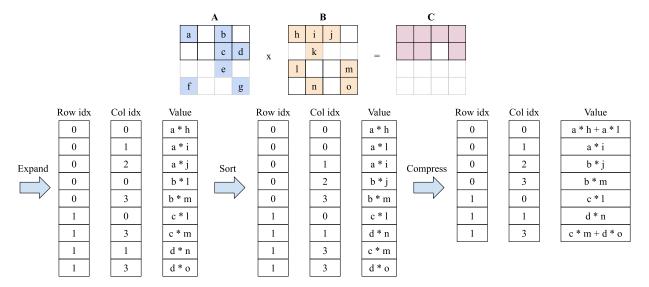

|   |       | 5.3.2 SpGEMM Dataflows                                                | 83  |

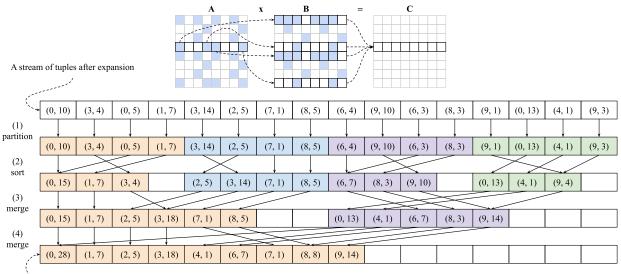

|   |       | 5.3.3 Row-Wise Product Algorithms                                     | 85  |

|   | 5.4   | SparseZipper Instruction Set Extension                                | 87  |

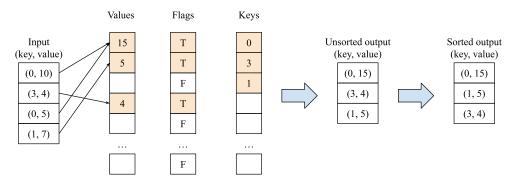

|   |       | 5.4.1 Merge-Based SpGEMM                                              | 87  |

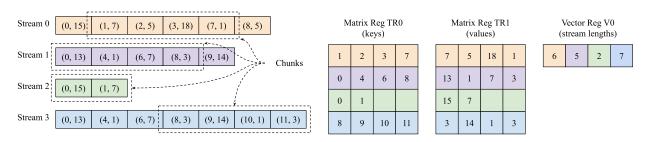

|   |       | 5.4.2 Architectural Register States                                   | 89  |

|   |       | 5.4.3 Instruction Set Specification                                   | 91  |

|   |       | 5.4.4 Code Examples                                                   | 99  |

|   | 5.5   | SparseZipper Micro-Architecture                                       |     |

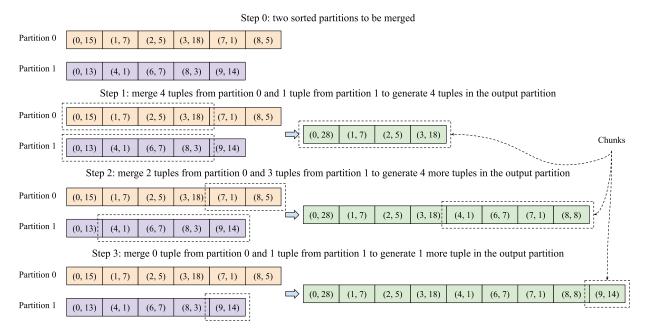

|   |       | 5.5.1 Systolic Execution of Sorting a Pair of Key-Value Lists         |     |

|   |       | 5.5.2 Systolic Execution of Merging a Pair of Sorted Key-Value Lists  |     |

|   |       | 5.5.3 Merging and Sorting Multiple Pairs of Key-Value Lists           |     |

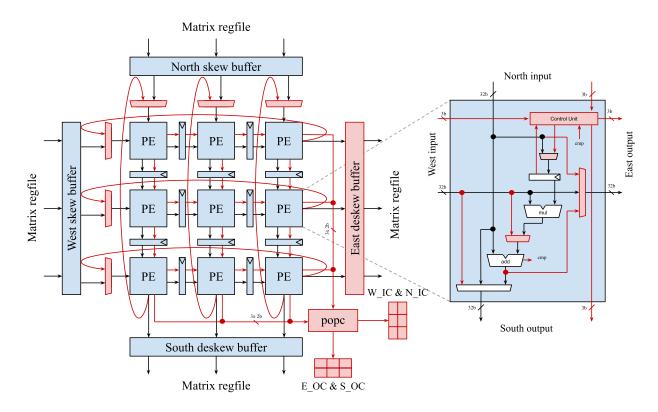

|   |       | 5.5.4 Micro-architectural Extension to the Baseline Systolic Array    |     |

|   | 5.6   | Evaluation Methodology                                                |     |

|   |       | 5.6.1 Simulated Systems                                               | 111 |

|    |        | 5.6.2 SpGEMM Implementations               | 14 |

|----|--------|--------------------------------------------|----|

|    |        | 5.6.3 Matrix Datasets                      | 15 |

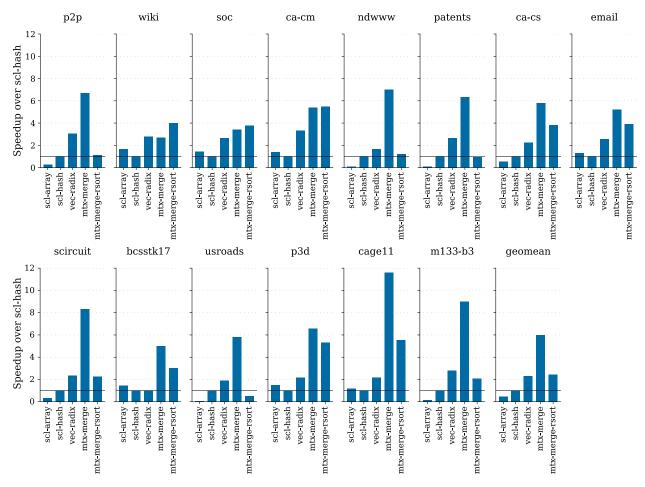

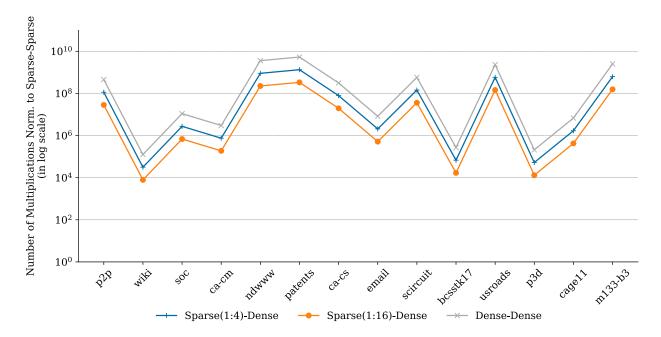

|    | 5.7    | Evaluation                                 | 15 |

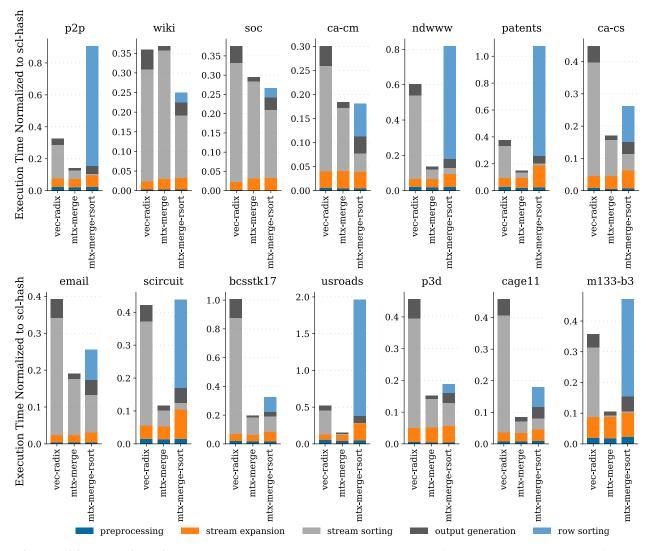

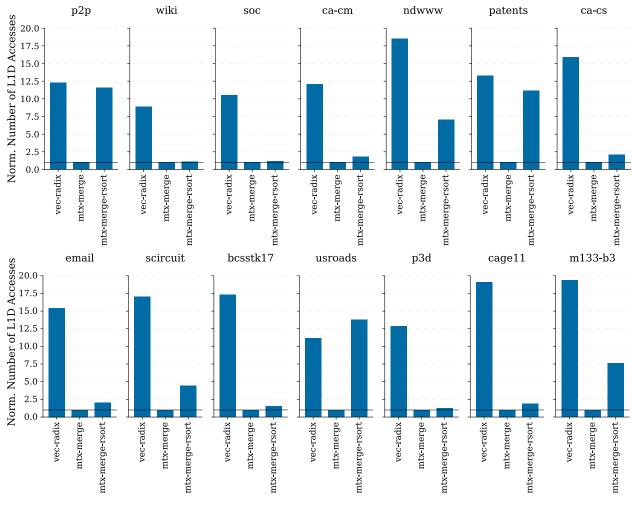

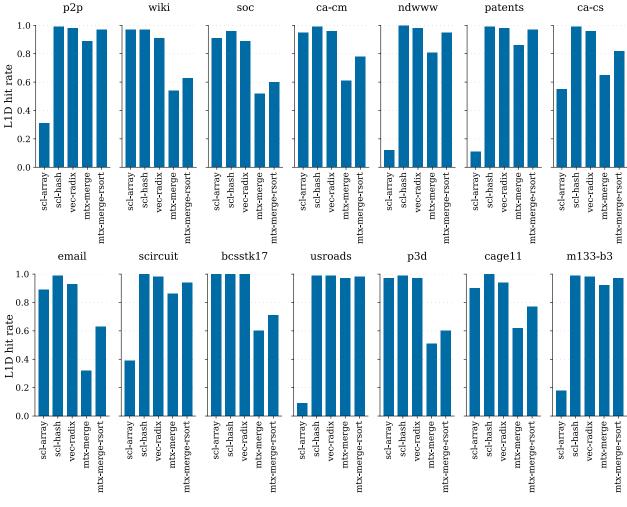

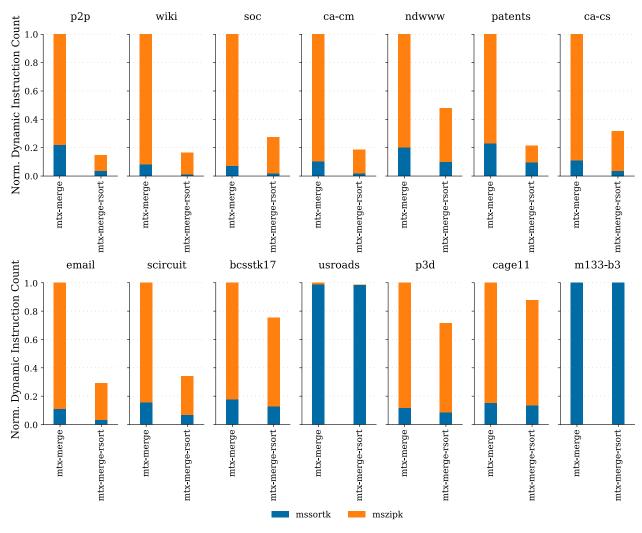

|    |        | 5.7.1 Performance Evaluation               |    |

|    |        | 5.7.2 Area Evaluation                      | 22 |

|    | 5.8    | Related Work                               | 23 |

|    | 5.9    | Conclusion                                 | 27 |

| 6  | Con    | clusion 1                                  | 28 |

|    | 6.1    | Thesis Summary and Contributions           | 28 |

|    | 6.2    | Discussions on Evolutionary Specialization | 30 |

|    | 6.3    | Future Work                                | 32 |

| Bi | bliogi | aphy 1.                                    | 34 |

### LIST OF FIGURES

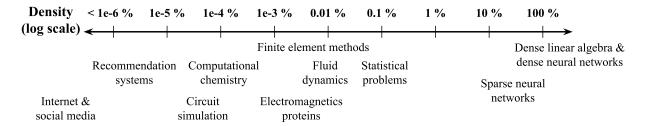

| 1.1<br>1.2                             | Matrix Density Spectrum Across Different Workload Domains                                                                                                |                            |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

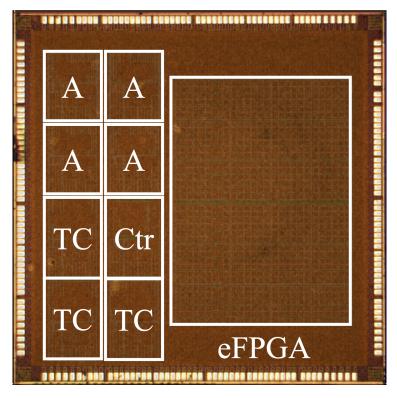

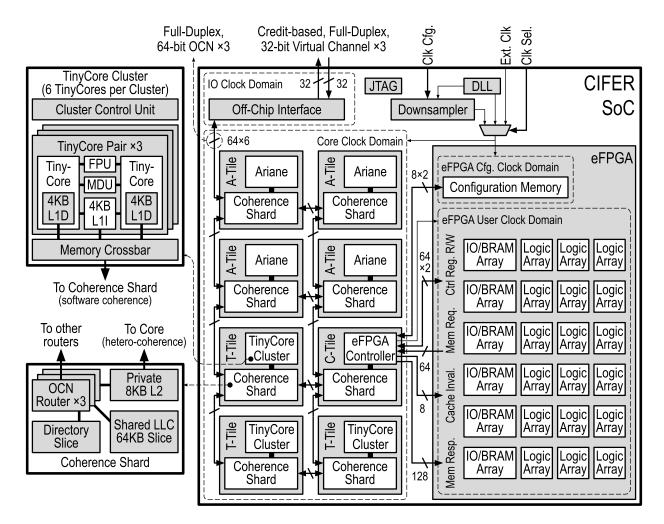

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5        | CIFER System-on-Chip Die Photo                                                                                                                           | 18<br>19<br>24             |

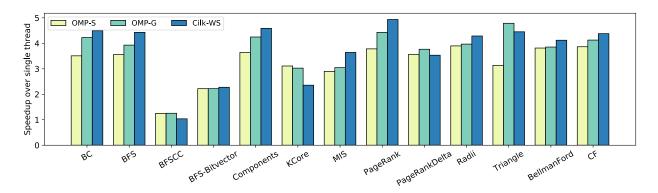

| <ol> <li>3.1</li> <li>3.2</li> </ol>   | Simulated Performance of Different Task Scheduling Mechanisms                                                                                            | 40                         |

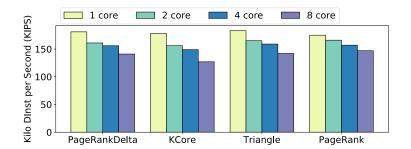

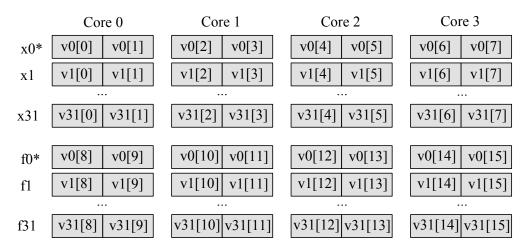

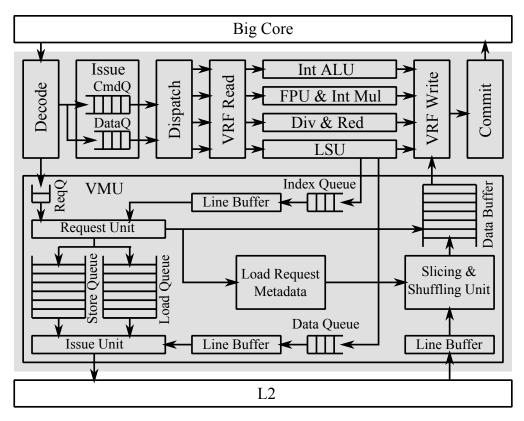

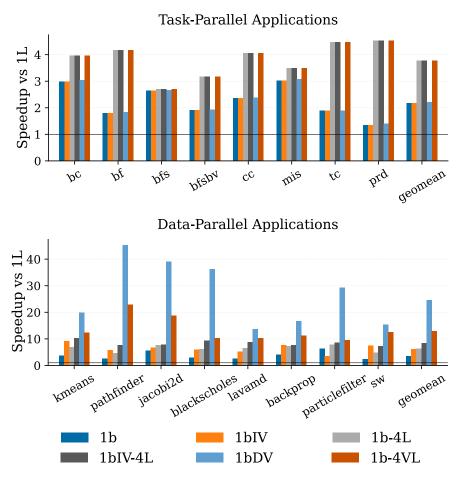

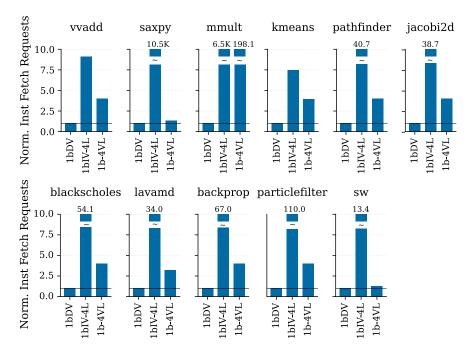

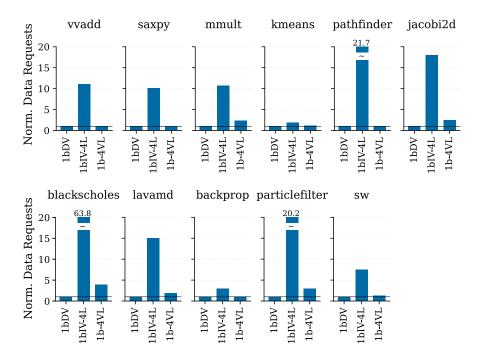

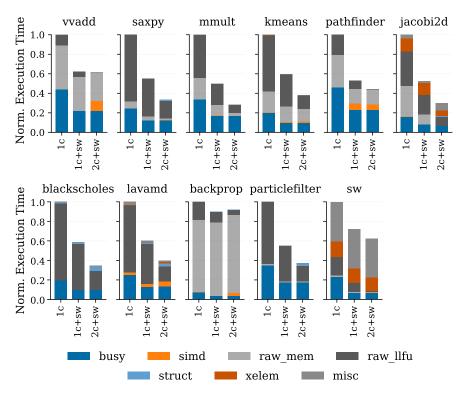

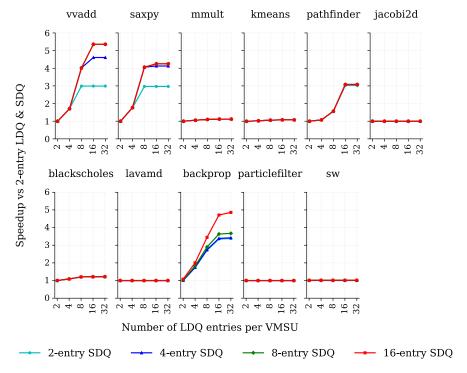

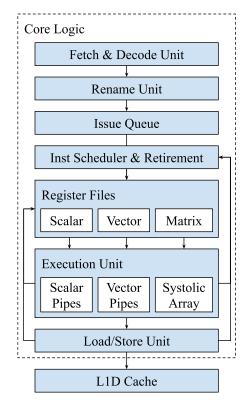

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | big.VLITTLE Micro-Architecture                                                                                                                           | 53<br>59<br>64<br>65<br>65 |

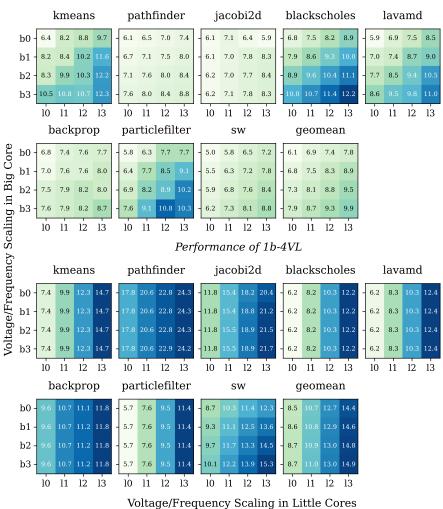

| 4.7<br>4.8                             | big.VLITTLE Execution Breakdown                                                                                                                          |                            |

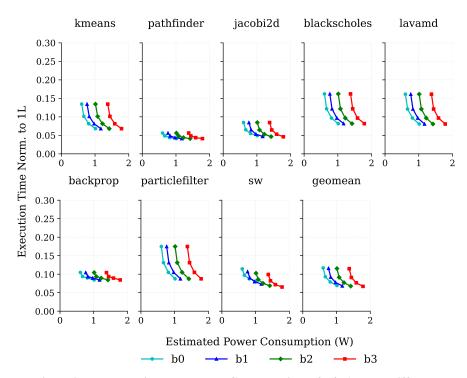

| 4.9                                    | big. VLITTLE Performance at Different Voltage/Frequency Scaling Levels                                                                                   |                            |

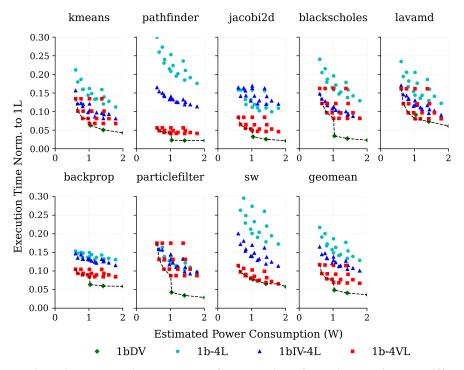

| 4.10<br>4.11                           | Execution Time and Estimated Power Consumption of All Designs at Different<br>Execution Time and Estimated Power Consumption of All Designs at Different |                            |

|                                        | Frequencies                                                                                                                                              | . 74                       |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5        | Baseline Systolic Array for Accelerating Dense GEMM                                                                                                      | 82<br>84<br>86             |

| 5.6                                    | Multiple Steps To Merge Partial Results for a Row in an Output Matrix                                                                                    | 88                         |

| 5.7                                    | Multiple Steps to Merge Two Sorted Partitions of Key/Value Tuples                                                                                        |                            |

| 5.8                                    | Logical Mapping Between Key/Value Streams and Matrix Registers                                                                                           |                            |

| 5.9                                    | Matrix Instructions in the Base Matrix ISA                                                                                                               |                            |

| 5.10                                   | Indexed Memory Instructions in SparseZipper                                                                                                              |                            |

| 5.11<br>5.12                           | Stream Key Sorting Instruction in SparseZipper                                                                                                           |                            |

| 5.12                                   | Stream Key Zipping Instruction in SparseZipper                                                                                                           |                            |

| 5.13                                   | Stream Value Zipping Instruction in SparseZipper                                                                                                         |                            |

| 5.15                                   | Counter Vector Move Instructions in SparseZipper                                                                                                         |                            |

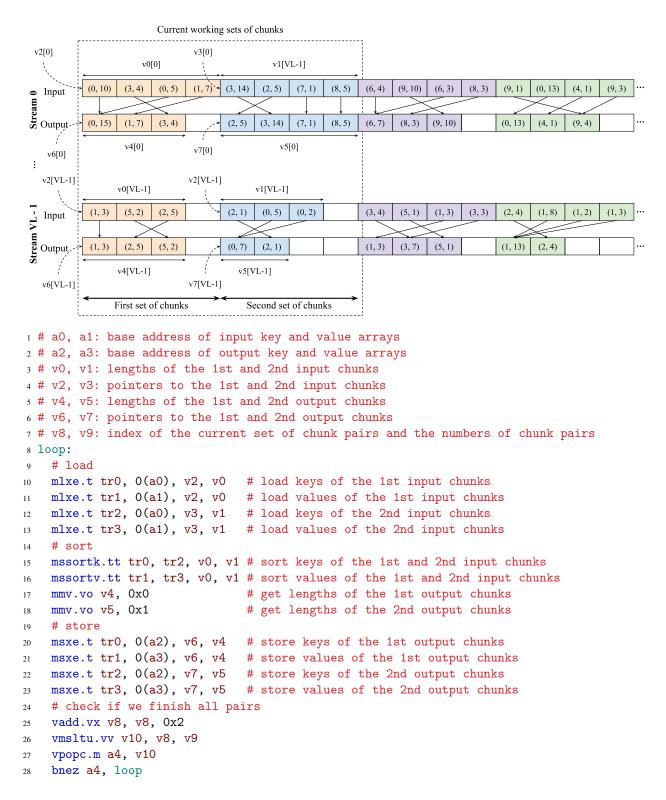

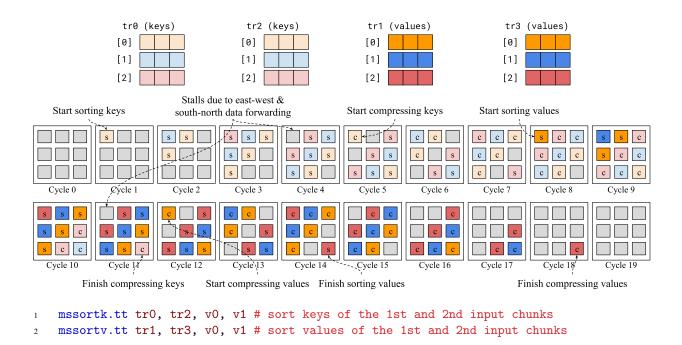

| 5.16                                   | Sorting Chunks of Keys and Values from Multiple Streams in Parallel                                                                                      |                            |

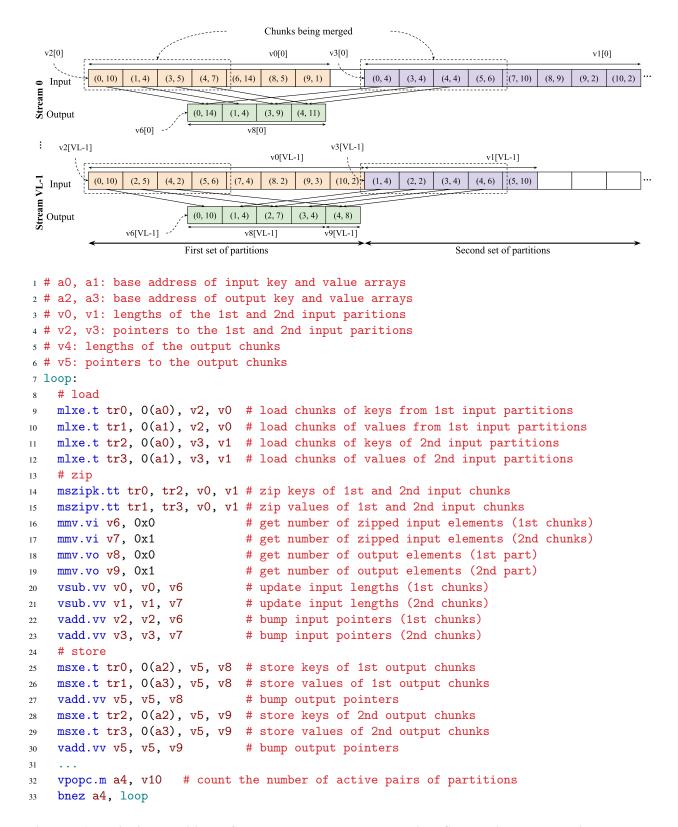

| 5.17                                   | Zipping Partitions of Keys and Values across Multiple Streams in Parallel                                                                                |                            |

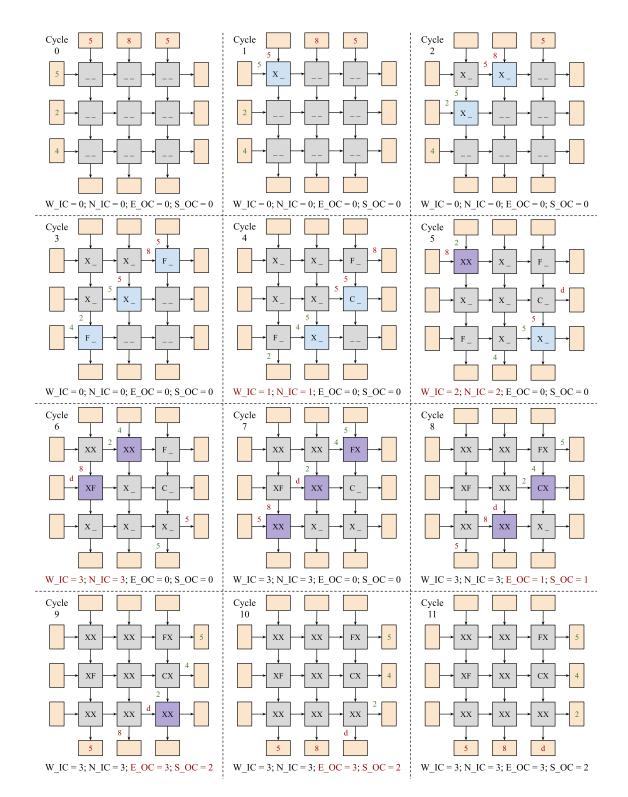

| 5.18 | Cycle-by-Cycle Systolic Execution of mssortk in a 3×3 Systolic Array for Two   |

|------|--------------------------------------------------------------------------------|

|      | Unsorted Lists of Keys                                                         |

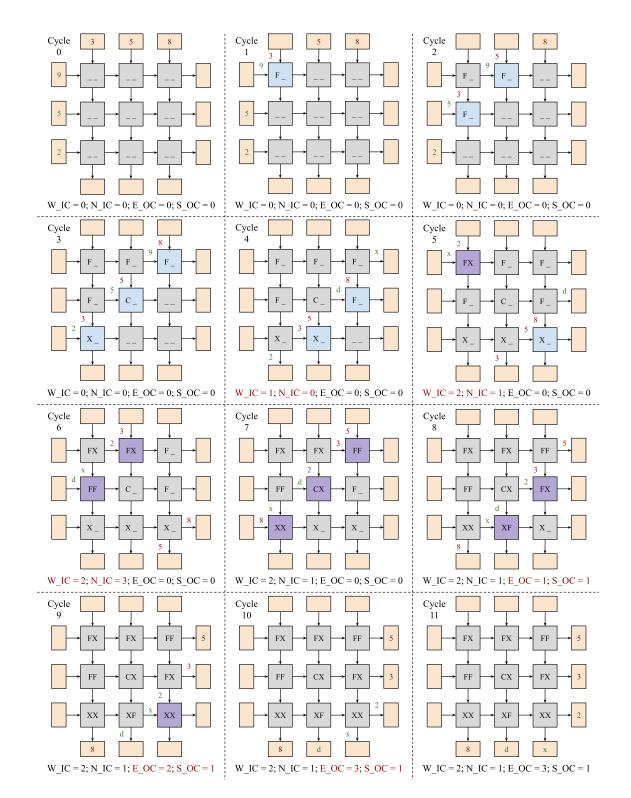

| 5.19 | Cycle-by-Cycle Systolic Execution of mszipk in a 3×3 Systolic Array for Two    |

|      | Sorted Lists of Keys                                                           |