# Workshop on Complexity–Effective Design

Held in conjunction with the 32nd International Symposium on Computer Architecture

> Madison, Wisconsin June 5, 2005

# Workshop Organizers:

Dave Albonesi, Cornell University Pradip Bose, IBM Corporation Prabhakar Kudva, IBM Corporation Diana Marculescu, Carnegie–Mellon University

# WCED Program

# 8:30-9:30AM Session I

- Effects of Pipeline Complexity on SMT/CMP Power-Performance Efficiency *B. Lee and D. Brooks (Harvard University)*

- Early Performance Prediction *P. Kudva, B. Curran, S.K. Karandikar, M. Mayo, S. Carey (IBM), and S.S. Sapatnekar (University of Minnesota)*

- Wire Management for Coherence Traffic in Chip Multiprocessors L. Cheng, N, Muralimanohar, K. Ramani, R. Balasubramonian, and J. Carter (University of Utah)

# 9:30-9:50AM Break 9:50-10:30AM Session II

- Reducing the Power and Complexity of Path-Based Neural Branch Prediction *G.H. Loh (Georgia Institute of Technology) and D.J. Jiménez (Rutgers University)*

- A Break-Even Formulation For Evaluating Branch Predictor Energy Efficiency *M. Co, D.A.B Weikle, and K. Skadron (University of Virginia)*

# 10:30-11:00AM Break 11:00-11:40AM Session III

- Heuristics for Complexity-Effective Verification of a Cache Coherence Protocol Implementation D. Abts (Cray), Y. Chen, and D.J. Lilja (University of Minnesota)

- The Design Complexity of Program Undo Support in a General-Purpose Processor *R. Teodorescu and J. Torrellas (University of Illinois at Urbana-Champaign)*

11:40AM-12:30PM Metrics discussion led by J. Torrellas (University of Illinois at Urbana-Champaign)

# Introduction

The quest for higher performance via deep pipelining (for high clock rate) and speculative, out-of-order execution (for high IPC) has yielded processors with greater performance, but at the expense of much greater design complexity. The costs of higher complexity are many-fold, including increased verification time, higher power dissipation, and reduced scalability with process shrinks/variations. The Workshop on Complexity-Effective Design (WCED) was founded with the intention of bringing together microarchitects, circuit designers, performance modelers, compiler developers, verification experts, and system designers to discuss and explore hardware/software techniques and tools for creating future designs that are more complexity-effective.

A complexity-effective design feature or tool either (a) yields a significant performance and/or power efficiency improvement relative to the increase in hardware/software complexity incurred; or (b) significantly reduces complexity (design time and/or verification time and/or improved scalability) with a tolerable performance/power impact. The papers in this year's WCED program address both of these themes.

We wish to thank Mikko Lipasti, the Workshops Chair, and the other ISCA organizers that allowed us to offer the workshop, the WCED Program Committee (Todd Austin, R. Iris Bahar, David Brooks, Alper Buyuktosunoglu, George Cai, Babak Falsafi, Keith Farkas, Antonio Gonzalez, Peter Hofstee, Gokhan Memik, Chuck Moore, and Subbarao Palacharla), all those who reviewed papers, and all workshop authors and presenters. We welcome any and all feedback that will help us improve WCED in future years.

Dave Albonesi Pradip Bose Prabhakar Kudva Diana Marculescu

WCED Co-Chairs

# Effects of Pipeline Complexity on SMT/CMP Power-Performance Efficiency

Benjamin Lee and David Brooks Harvard University Division of Engineering and Applied Sciences Cambridge, Massachusetts, USA {bclee, dbrooks}@eecs.harvard.edu

#### Abstract

We consider processor core complexity and its implications for the power-performance efficiency of SMT and CMP architectures, exploring fundamental trade-offs between the efficiency of multi-core architectures and the complexity of their cores from a power-performance perspective. Taking pipeline depth and width as proxies for core complexity, we conduct power-performance simulations of several SMT and CMP architectures employing cores of varying complexity. Our analyses identify efficient pipeline dimensions and outline the implications of using a powerperformance efficiency metric for core complexity.

Collectively, our results suggest SMT architectures enable efficient increases in pipeline dimensions and core complexity. Furthermore, reducing pipeline dimensions in CMP cores is inefficient, assuming ideal power-performance scaling from voltage/frequency scaling and circuit re-tuning. Given these conclusions, we formulate guidelines for complexity effective design.

#### 1. Introduction

We present an analysis of processor core complexity, quantified by pipeline depth and width, and its effects on the power-performance efficiency of simultaneous multi-threading (SMT) and chip multi-processing (CMP). We define efficiency in terms of  $BIPS^3/W$ , a voltage invariant power-performance metric that captures the cubic relationship between power and performance. Research in efficient computer architectures has been motivated by significant increases in power dissipation on high-performance systems. Increasing power dissipation also complicates thermal management and current/voltage stability in a system. SMT and CMP architectures are of particular interest as the microprocessor industry moves towards such systems to meet performance targets in mainstream computing [1, 2, 3].

SMT architectures amortize the cost of microarchitectural structures over a greater number of instructions per cycle drawn from multiple threads. Similarly, CMP architectures increase thread-level parallelism by constructing multiple processor cores on a single die. Prior work has examined the power-performance efficiency of such architectures for a particular core design [4, 5] or a particular class of applications [6]. In contrast, we examine SMT/CMP efficiency as a function of core complexity by taking pipeline depth and width as a proxy for complexity.

We specify pipeline depth by the number of FO4 inverter delays per pipeline stage<sup>1</sup> and pipeline width by the maximum number of instructions decoded per cycle. Identifying optimal pipeline parameters for SMT and CMP cores effectively optimizes the balance between instruction-level and thread-level parallelism to maximize efficiency.

Conducting simulations of several SMT and CMP system configurations with varying pipeline parameters (Section 2), we identify power-performance efficient pipeline dimensions and outline the implications of using an efficiency metric for core complexity (Section 3, Section 4). Overall, we draw the following conclusions:

- 1. SMT architectures enable power-performance efficient increases in pipeline dimensions toward deeper, wider pipelines (Section 3.3, Section 4.3).

- Reducing pipeline dimensions in CMP architectures is power-performance inefficient (Section 3.4, Section 4.4) relative to alternatives from hardware tuning.

Collectively, these results support the conventional wisdom that SMT architectures are more effective with deeper, wider pipelines and refute the belief that CMP core complexity should decrease relative to uni-processor complexity. We employ these conclusions to formulate guidelines for complexity effective SMT and CMP design (Section 5).

<sup>1</sup> Fan-out-of-four (FO4) delay is defined as the delay of one inverter driving four copies of an equally sized inverter. When logic and latch overhead per pipeline stage is measured in terms of FO4 delay, deeper pipelines have smaller FO4 delays.

#### 2. Experimental Methodology

#### 2.1. Performance Modeling

We employ Turandot, a cycle-based microprocessor performance simulator [7, 8], to obtain data for varying pipeline designs in out-of-order superscalar processors. We evaluate the performance of a design in terms of its achieved instruction throughput measured in billions of instructions per second (BIPS). We compute throughput for *n* threads with Equation (1), where  $Inst_i$  is the number of instructions committed by thread *i*,  $max(Cy_i)$  is the number of cycles required to complete the execution of all threads, and *f* is the clock frequency. We also evaluate performance in terms of effective delay or inverse throughput ( $BIPS^{-1}$ ).

$$BIPS = \frac{\sum_{i=1}^{n} Inst_i}{max(Cy_i)} \times \frac{f}{10^6} \tag{1}$$

#### 2.2. Power Modeling

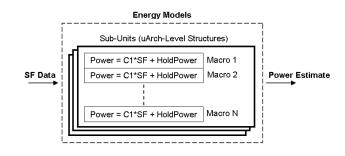

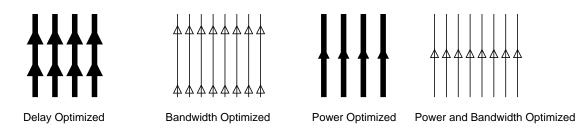

We employ PowerTimer, a Turandot based microarchitectural simulator with power modeling extensions, to examine the power implications of varying pipeline designs [9, 10]. The PowerTimer energy models are based on circuit-level power analyses performed on microarchitectural structures in a modern, high-performance PowerPC [11]. Each structure or subunit is comprised of multiple individually analyzed macros. The circuit-level power analyses determine each structure's power dissipation as the sum of hold power and switching power where switching power is a function of the structure's input switching factor. The unconstrained hold and switching power for each macro are combined to generate linear equations for each macro's power. A linear combination of power equations for the macros within a particular subunit produces the subunit's unconstrained power model (Figure 1). PowerTimer uses microarchitectural activity information from Turandot to scale down each subunit's unconstrained hold and switching power under a variety of clock gating assumptions on a per-cycle basis to get the final estimate of power.

Power dissipated by a processor consists of dynamic and leakage components,  $P = P_{dynamic} + P_{leakage}$ . The dynamic component may be expressed as

$$P_{dynamic} = CV^2 f(\alpha + \beta) \times CGF \tag{2}$$

where  $\alpha$  is the true switching factor required for logic functionality,  $\beta$  is the glitching factor that accounts for spurious transitions resulting from differing delays between

Figure 1. PowerTimer Energy Models.

logic paths. Thus,  $(\alpha + \beta)$  is the average number of actual transitions. The clock gating factor, CGF, is the fraction of cycles during which microarchitectural structures are not clock gated. The remaining variables are the effective switching capacitance (C), the supply voltage (V), and the clock frequency (f).

#### 2.3. Power-Performance Efficiency

We use  $\frac{BIPS^3}{W}$  as our power-performance efficiency metric for comparing different pipeline designs. This metric is derived from the cubic relationship between power dissipation and the supply voltage, given a fixed logic/circuit design. Since  $P_{dynamic} \approx CV^2 f \alpha \times CGF$  and V is roughly proportional to f,  $P_{dynamic} \approx CV^3 \alpha \times CGF$ . Thus, power is roughly proportional to  $V^3$ . This suggests  $P \times D^3$ , where P is power and D is delay, is an appropriate voltage invariant power-performance metric for server-class microprocessors [9]. Lastly, note that  $\frac{BIPS^3}{W} \equiv (P \times D^3)^{-1}$ .

#### 2.4. Microarchitectural Modeling

The baseline configuration is a single-threaded pipeline with 19 FO4 delays per stage capable of decoding four nonbranch instructions per cycle (Table 1). We also analyze several SMT and CMP architectures (Table 2) with extended versions of Turandot and PowerTimer[5]. The SMT cores are modeled by increasing the sizes of shared and critical resources (*e.g.* register file and issue queues) by 50 percent and implementing round-robin thread scheduling. CMP architectures are simulated as separate cores, tracking conflicts in the shared L2 cache and cache bus. Inter-thread synchronization is not currently supported.

We refer to a particular design point as [*arch,depth,width*], where *arch* is an architecture from Table 2 and *depth*, *width* refer to the pipeline dimensions. Depth is quantified in terms of FO4 delays per pipeline stage and width is quantified in terms of the number of non-branch instructions decoded per cycle. For example, the baseline is denoted as [ST,19,4].

| Processor Core       |                                        |  |  |

|----------------------|----------------------------------------|--|--|

| Decode Rate          | 4 non-branch instructions per cycle    |  |  |

| Dispatch Rate        | 9 instructions per cycle               |  |  |

| Reservation Stations | FXU(40),FPU(10),LSU(36),BR(12)         |  |  |

| Functional Units     | 2 FXU, 2 FPU, 2 LSU, 2 BR              |  |  |

| Physical Registers   | 80 GPR, 72 FPR                         |  |  |

| Branch Predictor     | 16k 1-bit entry BHT                    |  |  |

| Memory Hierarchy     |                                        |  |  |

| L1 DCache Size       | 32KB, 2-way, 128B blocks, 1-cy latency |  |  |

| L1 ICache Size       | 32KB, 1-way, 128B blocks, 1-cy latency |  |  |

| L2 Cache Size        | 2MB, 4-way, 128B blocks, 9-cy latency  |  |  |

| Memory               | 77-cy latency                          |  |  |

| Pipeline Dimensions  |                                        |  |  |

| Pipeline Depth       | 19 FO4 delays per stage                |  |  |

| Pipeline Width       | 4-decode                               |  |  |

Table 1. Baseline Microarchitectural Parameters.

| Architecture | Description                                           |

|--------------|-------------------------------------------------------|

| ST           | Single-threaded baseline (Table 1)                    |

| SMT1c1t      | SMT-expanded core running 1 thread                    |

| SMT1c2t      | SMT-expanded core running 2 threads                   |

| CMP2c1t      | CMP with 2 SMT-expanded cores, each running 1 thread  |

| CMP2c2t      | CMP with 2 SMT-expanded cores, each running 2 threads |

Table 2. SMT, CMP Architectures.

#### 2.5. Benchmarks

We report experimental results from a suite of 21 traces from the SPEC2000 benchmarks in Table 3. The traces were generated with the tracing facility *Aria* [8] using the full reference input set. However, sampling reduced the total trace length to 100 million instructions per benchmark program. The sampled traces were validated against the full traces before finalizing the traces [12].

We present power and performance data as an average of the SPEC2000 benchmarks. The single-threaded core configurations (*i.e.*, ST and SMT1c1t) were run with every benchmark in the suite. The multi-threaded core configurations (*i.e.*, SMT1c2t and CMP\*c\*t) were run with multiple copies of the same benchmark for every benchmark in the suite. For example, we simulated CMP2c2t running four copies of *ammp*. Identifying an interesting subset of heterogeneous benchmarks for parallel execution is future work.

#### 3. Pipeline Depth Analysis

#### 3.1. Depth: Performance Scaling

Models for architectures with varying pipeline depths are derived from the reference 19 FO4 design by treating the total number of logic levels as constant independent of the number of pipeline stages. This is an abstraction for the purpose of our analyses; increasing the pipeline depth could require logic design changes. The baseline latencies (Table 4) are scaled to account for pipeline changes according to

$$Latency_{target} = \left\lfloor Latency_{base} \times \frac{FO4_{base}}{FO4_{target}} + 0.5 \right\rfloor \quad (3)$$

| SPEC2000 Benchmarks |        |        |         |

|---------------------|--------|--------|---------|

| ammp                | applu  | apsi   | art     |

| bzip2               | crafty | equake | facerec |

| gap                 | gcc    | gzip   | lucas   |

| mcf                 | mesa   | mgrid  | perl    |

| sixtrack            | swim   | twolf  | vpr     |

| wupwise             |        |        |         |

Table 3. SPEC2000 Benchmark Suite.

| Fetch            |                  | Decode              |    |

|------------------|------------------|---------------------|----|

| NFA Predictor    | 1                | Multiple Decode 2   |    |

| L2 I-Cache       | 11               | Millicode Decode    | 2  |

| L3 I-Load        | 8                | Expand String       | 2  |

| I-TLB Miss       | 10               | Mispredict Cycles 3 |    |

| L2 I-TLB Miss    | 50               | Register Read 1     |    |

| Execution        | Execution Memory |                     |    |

| Fix Execute      | 1                | L1 D-Load           | 3  |

| Float Execute    | 4                | L2 D-Load           | 9  |

| Branch Execute   | 1                | L3 D-Load           | 77 |

| Float Divide     | 12               | Float Load          | 2  |

| Integer Multiply | 7                | D-TLB Miss          | 7  |

| Integer Divide   | 35               | L2 D-TLB Miss       | 50 |

| Retire Delay     | 2                | StoreQ Forward      | 4  |

Table 4. [ST,19,4] Latencies (cy).

All latencies have a minimum of one cycle. This is consistent with prior work in pipeline depth simulation and analysis for a single-threaded core [14].

#### 3.2. Depth: Power Scaling

Each factor in Equation (2) scales with pipeline depth. The clock frequency f increases linearly with depth as the delay for each pipeline stage decreases. The clock gating factor CGF decreases by a workload dependent factor as pipeline depth increases due to the increased number of cycles in which the shorter pipeline stages are stalled. As the true switching factor  $\alpha$  is independent of the pipeline depth and the glitching factor  $\beta$  decreases with pipeline depth due to shorter distances between latches, switching power dissipation decreases with pipeline depth. The latch count, and consequently hold power dissipation, increases linearly with pipeline depth. We take leakage power as 30 percent of dynamic power dissipation. We refer the reader to prior work for a detailed treatment of these scaling models.

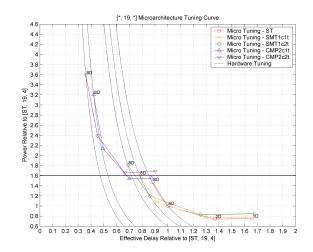

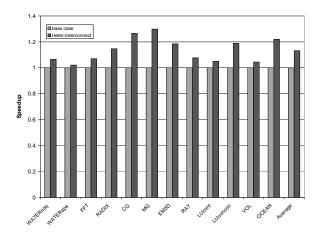

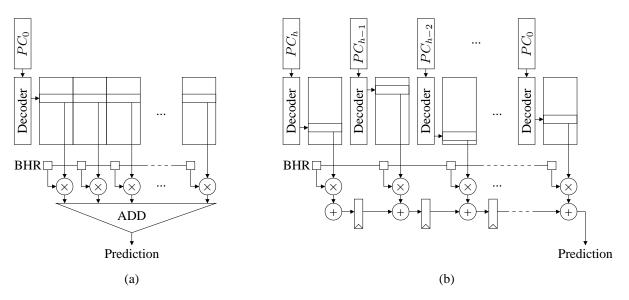

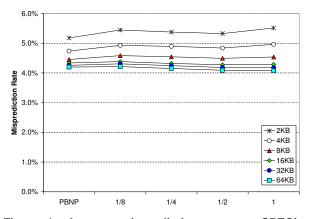

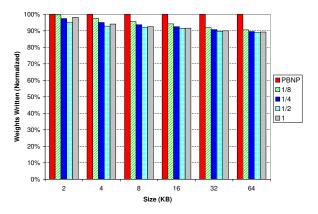

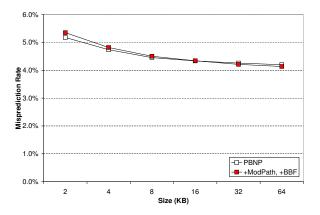

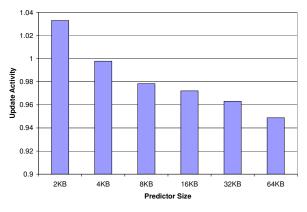

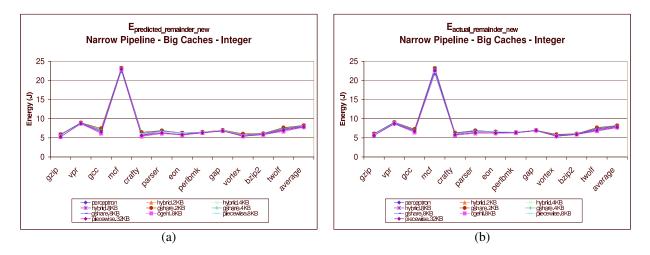

#### 3.3. Depth: Power-Performance Evaluation

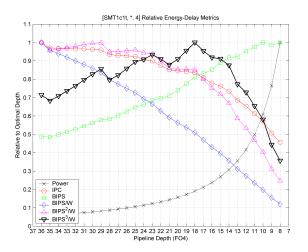

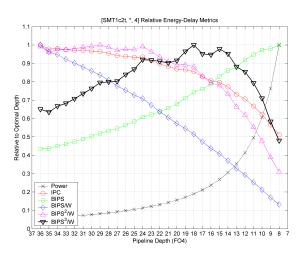

Figure 2 presents the power and performance trends as the pipeline depth increases for [SMT1c1t,\*,4] as an average of the 21 benchmarks in our suite (Table 3).<sup>2</sup> Note that pipeline depth is quantified in FO4 delays per stage and smaller FO4 delays are equivalent to deeper pipelines.

The performance maximizing pipeline depth is the 10 FO4 design point, where performance is measured in BIPS.

<sup>2 [</sup>ST,\*,4] and [SMT1c1t,\*,4] have similar trends despite differences in resource sizing. The CMP architectures, [CMP2c\*t,\*,4], effectively double the power and throughput of their SMT counterparts and are not evident in relative trends.

Figure 2. [SMT1c1t,\*,4] Power-Performance Metrics.

Figure 3. [SMT1c2t,\*,4] Power-Performance Metrics.

Since power increases superlinearly and performance increases sublinearly with pipeline depth, the performance to power ratio  $\frac{BIPS}{W}$  decreases with depth. In contrast, the 18 FO4 design point is power-performance efficient, maximizing the  $\frac{BIPS^3}{W}$  metric. Note  $\frac{BIPS^3}{W}$  decreases significantly as the number of pipeline stages increases beyond this design point. In particular, the performance maximizing 10 FO4 design point is 40 percent less efficient than the power-performance optimal 18 FO4 design point.

Figure 3 performs a similar power-performance analysis for the same architecture simultaneously executing two threads, [SMT1c2t,\*,4]. Relative to the [SMT1c1t,\*,4] results from Figure 2, we find executing a second thread mitigates the efficiency penalties associated with deeper pipelines. Although SMT1c1t and SMT1c2t share the same optimal pipeline depth of 18 FO4 delays per stage, deeper SMT1c2t pipelines up to the 14 FO4 design point achieve  $\frac{BIPS^3}{W}$  within 5 percent of the optimal. In contrast, increasing SMT1c1t pipeline depth to 14 FO4 delays per stage reduces  $\frac{BIPS^3}{W}$  by more than 10 percent. If performance were the only objective and the 8 FO4 design point were chosen, the 52 percent loss in efficiency for SMT1c2t is significantly smaller than the 64 percent loss for SMT1c1t.

Overall, these results are consistent with the conventional wisdom that SMT architectures perform better in deeper pipelines. The larger number of pipeline stages allows interleaving multiple simultaneous threads at a finer granularity than those afforded by shallower pipelines. Although SMT enables power-performance efficient increases in pipeline depth, voltage/frequency scaling and circuit retuning may provide many of the same benefits for significantly less engineering effort.

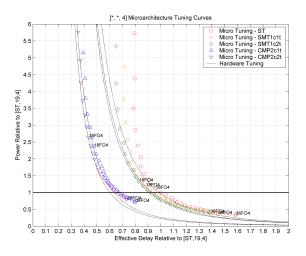

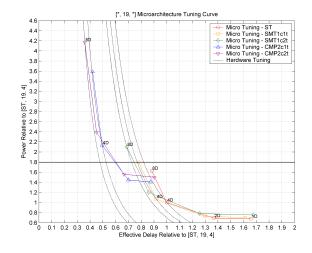

#### 3.4. Depth: Complexity Implications

Figure 4 depicts *microarchitectural tuning curves* for each architecture[14]. The average effective delay (or inverse throughput<sup>3</sup>) of the traces in our benchmark suite is plotted on the x-axis in units relative to the baseline [ST,19,4]. The average power dissipation is similarly plotted on the y-axis. The scatter plots indicate the location of each design point in this power-performance space, capturing trends in power-performance trade-offs at each point for a fixed supply voltage. The deeper pipelines are positioned in the high-power, low-delay region of the tuning space.

The downward sloping plots are hardware tuning curves representing the power-performance trade-offs achievable from varying the supply voltage and tuning the circuits to meet the frequency target. These curves are an abstraction of the techniques employed and design decisions made at various stages in the microprocessor design (e.g. voltage/frequency scaling, transistor sizing, and circuit styles). As the delay budget tightens, greater gate-level parallelism and transistor sizes are needed and more power is dissipated. Hardware intensity,  $\eta$ , quantifies these power and performance trade-offs by specifying the percentage change in energy required to achieve a 1 percent improvement in the critical path delay by restructing the logic and re-tuning the circuits for a given power supply [13]. Mathematically,  $\eta = -\frac{\% E}{\% D}$ . Assuming a typical hardware intensity of two, these curves represent a 1 percent reduction in effective delay by changing the power supply and tuning the hardware, at a cost of 3 percent in power. This is consistent with the cubic relationship between power and performance.

The efficient 18 FO4 design point from Section 3.3 is also the point on the microarchitectural tuning curve where a 1 percent performance gain from increasing the pipeline

<sup>3</sup> Zyuban et al. originally tracked delay on this axis, but inverse throughput  $(BIPS^{-1})$  is a more accurate description of this metric when considering multiple thread contexts.

Figure 4. [\*,\*,4] Micro Tuning Curves.

depth requires a 3 percent increase in power dissipation. Graphically, this implies the point of tangency between the microarchitectural and hardware tuning curves is the efficient design point that delivers a given level of performance while minimizing power.

Let the power budget be the relative power dissipation of the original design [ST,19,4]. Alternative designs that meet this power budget include [SMT1c1t,20,4], [SMT1c2t,21,4], [CMP2c1t,30,4] and [CMP2c2t,31,4]. Note that each of these designs incorporate fewer pipeline stages while reducing effective delay. In particular, choosing [CMP2c2t,31,4] over [ST,19,4] reduces the number of pipeline stages by approximately two-thirds and decreases effective delay by approximately 35 percent.

[CMP2c2t,31,4] is inefficient because it is possible to achieve a greater reduction in delay for the same power dissipated, as illustrated in Figure 4. First, increase the pipeline depth to the 18 FO4 design point, the power-performance optimal for this architecture. This corresponds to moving up the CMP2c2t tuning curve from [CMP2c2t,31,4] to [CMP2c2t,18,4]. Second, tune the hardware until the power budget is met. This corresponds to moving down the hardware tuning curve until relative power dissipation is one. At this new, efficient design point, the power budget is met and effective delay is reduced by approximately 40 percent relative to [ST,19,4] and 8 percent relative to [CMP2c2t,31,4]. Thus, reducing core complexity in multi-core architectures are not power-performance efficient since hardware tuning more complex cores yields greater performance for the same power budget.

| 00                    |                                                                                                                           |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2D                    | 1D                                                                                                                        |  |  |  |

| Functional Units      |                                                                                                                           |  |  |  |

| 1                     | 1                                                                                                                         |  |  |  |

| 1                     | 1                                                                                                                         |  |  |  |

| 1                     | 1                                                                                                                         |  |  |  |

| 1                     | 1                                                                                                                         |  |  |  |

| 1                     | 1                                                                                                                         |  |  |  |

| Pipeline Stage Widths |                                                                                                                           |  |  |  |

| 4                     | 2                                                                                                                         |  |  |  |

| 2                     | 1                                                                                                                         |  |  |  |

| 2                     | 1                                                                                                                         |  |  |  |

| 2                     | 1                                                                                                                         |  |  |  |

| 2                     | 1                                                                                                                         |  |  |  |

|                       | 1           1           1           1           1           1           1           2           2           2           2 |  |  |  |

Table 5. [ST,19,\*] Width Resource Scaling.

| Structure                  | Energy Growth Factor |  |

|----------------------------|----------------------|--|

| Register Rename            | 1.1                  |  |

| Instruction Issue          | 1.9                  |  |

| Memory Unit                | 1.5                  |  |

| Multi-ported Register File | 1.8                  |  |

| Data Bypass                | 1.6                  |  |

| Functional Units           | 1.0                  |  |

Table 6. Energy Growth Parameters.

# 4. Pipeline Width Analysis

#### 4.1. Width: Performance Scaling

Performance data for architectures with varying pipeline widths are obtained from the reference 4-decode (4D) design by a linear scaling of the number of functional units and the number of non-branch instructions fetched, decoded, renamed, dispatched, and retired per cycle (Table 5). All pipelines have at least one instance of each functional unit. As pipeline width decreases, the number of instances of each functional unit is quickly minimized to one. Thus, the decode width becomes the constraining parameter for instruction throughput for the narrower pipelines we consider (*i.e.* 2D and 1D).

#### 4.2. Width: Power Scaling

A relatively optimistic power scaling technique assumes unconstrained hold and switching power increases linearly with the number of functional units, access ports, and any other parameter that must change as width varies. We expect linear power scaling to effectively estimate changes in power dissipation for functional units since we employ a clustered architecture. Superlinear power scaling effectively reduces to an approximate linear scaling for clustered structures[15, 16, 17]. Furthermore, cache port scaling by replicating a 1-read, 1-write port cache to obtain a 2-read, 1-write port cache for the Power-4 architecture, modeled by [ST,19,4], also suggests linear power scaling is applicable for this microarchitectural structure [18, 19].

In certain cases, however, linear power scaling is an optimistic first-order approximation and, for example, does not capture non-linear relationships between power and the number of register file access ports since it does not account for the additional circuitry required in a multi-ported SRAM cell. For this reason, we formulate a relatively pessimistic estimate of power dissipation trends as pipeline width varies by applying superlinear power scaling with exponents (Table 6) drawn from Zyuban's work in estimating energy growth parameters [15]. These parameters form a pessimistic power estimate since the values are experimentally derived from non-clustered architectures and tend to overestimate energy growth for clustered architectures.

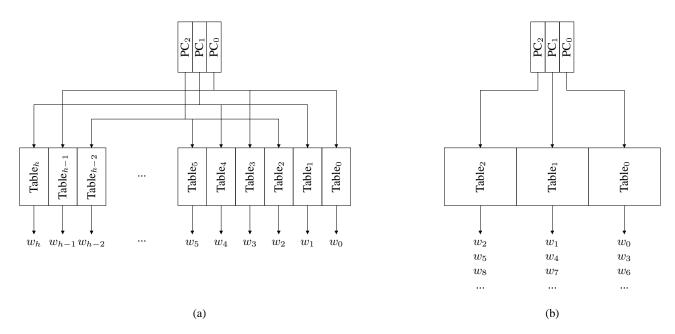

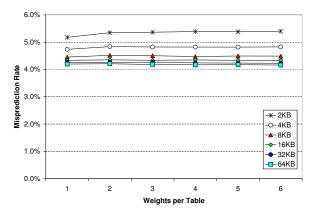

#### 4.3. Width: Power-Performance Evaluation

As in the pipeline analysis, Figures 5–6 depict microarchitectural tuning curves with linear and superlinear power scaling, respectively. These figures demonstrate the effects of tuning pipeline width for each architecture given a fixed pipeline depth. Note that pipeline width is quantified by the number of non-branch instructions decoded per cycle and faster decode rates correspond to wider pipelines.

Hardware tuning curves are drawn through powerperformance efficient design points. Under linear power scaling, a pipeline width of 8D is found to maximize  $\frac{BIPS^3}{W}$  for all architectures except the ST baseline; the efficient ST width is 4D. As in the depth analysis, the optimality of these design points can be demonstrated by considering an alternative design point and showing it cannot achieve lower delay for the same power budget.

Comparing the architectures executing one thread per core (i.e. ST, SMT1c1t, CMP2c1t) and those executing multiple simultaneous threads per core (i.e. SMT1c2t, CMP2c2t) with linear power scaling, we find executing a second thread motivates increasing pipeline width to improve efficiency. In particular, we find the 4D and 8D design points offer comparable efficiency when executing one thread, but choosing the wider 8D pipeline for architectures executing multiple threads can reduce effective delay by approximately 6 to 8 percent after hardware tuning to meet power constraints imposed by their respective original 4D design points. This observation may be drawn from Figure 5 by noting that microarchitectural tuning curves for single-threaded workloads track the hardware tuning curves more closely than their multi-threaded counterparts around the 4D and 8D design points.

As expected, superlinear power scaling decreases the power-performance optimal width to 4D for architectures executing a single thread per core and reduces the benefits of using the wider 8D design for architectures executing multiple threads per core. The hardware tuning curves in Figure 6 track the microarchitectural tuning curves more closely from 4D to 8D compared to those in Figure 5. This implies smaller efficiency penalties for choosing the 4D design over the 8D design.

Figure 5. [\*,19,\*] Micro Tuning Curves - Linear.

#### Figure 6. [\*,19,\*] Micro Tuning Curves - Superlinear.

Overall, these results are consistent with the conventional wisdom that SMT architectures perform better in wider pipelines. Conceptually, the larger number of instructions capable of entering a wider pipeline is better exploited when multiple thread contexts are executing simultaneously.

#### 4.4. Width: Complexity Implications

Since no other design point improves performance while meeting the power constraints imposed by [ST,19,4] with linear power scaling in Figure 5, we instead consider a power budget of 1.7 defined by the relative power dissipation of [SMT1c1t,19,8]. Alternative designs that meet this power budget are [SMT1c2t,19,4 < w < 8] and [CMP2c1t,19,2 < w < 4].<sup>4</sup> Note each of these designs employ cores with narrower pipelines while reducing delay.

As in the pipeline analysis, these alternative designs with less complex cores may not be power-performance efficient. [CMP2c1t,19,2 < w < 4] is inefficient since it is possible to achieve higher performance for the same power dissipated by increasing the pipeline width to 4D or 8D and tuning the hardware to meet power constraints. This corresponds to moving up the CMP2c1t tuning curve from [CMP2c1t,19,2 < w < 4] to [CMP2c1t,19,4] or [CMP2c1t,19,8], then moving down the hardware tuning curve until the relative power dissipation is 1.7. At this new, efficient design point, the power constraints are satisfied and delay is reduced by approximately 33 percent relative to [SMT1c1t,19,8], compared to an approximately 12 percent reduction achieved from [CMP2c1t,19,2 < w < 4].

With the relatively pessimistic superlinear power scaling in Figure 6, however, the efficiency differences between the 8D and 4D designs are negligible for both SMT and CMP architectures. In these cases, the 4D design is preferrable since it is likely much less complex than the 8D design point.

Note the analysis thus far has emphasized the relative efficiency of the 8D and 4D design points. In no case, however, does the data support moving to cores narrower than the baseline 4D design. The [CMP2c2t,19,8] design point reduces effective delay by 45 percent over the baseline [ST,19,4] after hardware tuning with linear power scaling. In contrast, the [CMP2c2t,19,2] design point only achieved a 30 percent reduction in delay without hardware tuning. Tuning the hardware for the 2D design would only further reduce performance gains. Thus, these analyses suggest reducing core complexity in multi-core architectures by employing narrower pipelines are not power-performance efficient. As with pipeline depth, hardware tuning more complex cores with wider pipelines to meet power budgets may be more efficient.

### 5. Complexity Effective Design

The preceding analyses suggest limited opportunities for efficiently reducing core complexity in CMP architectures. In particular, we draw the following conclusions:

- 1. Employing cores with shallower or narrower pipelines is power-performance inefficient since hardware tuning an efficient design achieves higher performance for the same power dissipation.

- In the cases where multiple design points are efficient, designers are able to choose a complexity effective design among these efficient alternatives.

3. Given a need to reduce complexity, the efficiency penalties for shallower pipelines are less than those for narrower pipelines.

The analyses from Section 3 and Section 4 find simply reducing pipeline depth or width is inefficient. Superior alternatives, from the perspective of power and performance, employ an efficient core in a multi-core architecture and tune the hardware to meet power constraints. Thus, designers should not rely on trends toward a larger number of less complex cores to meet power or performance targets, because such trends are likely to be inefficient. Overall, this conclusion implies microprocessor core design continues to play a significant role in CMP architectural development.

Multiple efficient design points exist in both depth and width analyses. In particular, designs ranging from 14 to 24 FO4 track the 3 percent, 1 percent power-performance trade-off of the hardware tuning curves, suggesting these designs are approximately equivalent from an efficiency perspective. Similarly, the 4D and 8D designs offer approximately the same efficiency. Choosing less complex designs from these efficient choices, enables designers to manage complexity among efficient alternatives.

The analyses in this paper seeks to maximize performance for a given power budget or minimize power for a given performance target. In the case where complexity constraints must also be met at the expense of power-performance efficiency, decreasing pipeline depth incurs less of an efficiency penalty relative to penalties incurred from decreasing pipeline width. For example, [CMP2c2t,36,4] incurs a 12 percent performance penalty relative to the hardware tuned [CMP2c2t,18,4]. In contrast, [CMP2c2t,19,2] incurs a 25 percent performance penalty relative to the hardware tuned [CMP2c2t,19,4]. Thus, designers seeking to reduce complexity should focus on pipeline depth to minimize the impact on efficiency.

Although we only consider two cores per chip, the complexity, power, and area of interconnect between cores in a CMP architecture becomes increasingly relevant as the number of cores increase [16, 28]. This suggests a fundamental trade-off between core and interconnect complexity. Employing many low complexity cores necessarily implies a more complex interconnect network. Conversely, as core complexity increases, fewer cores per chip are needed to achieve the same performance targets and a less complex interconnect network is required. Thus, complexity is effectively transferred from the interconnect to the CMP cores. Understanding this complexity trade-off is future work.

This work also neglects area effects which may become increasingly significant as the number of cores increase. Reducing core complexity while increasing the number of cores per chip may produce a net increase in throughput per

<sup>4</sup> We employ this interval notation due to limited granularity in our design exploration space.

unit area, a metric not considered in this paper. Accounting for these effects is future work.

# 6. Related Work

The experimental work in this paper combines prior research in optimizing pipeline depths and powerperformance analyses for SMT and CMP architectures.

#### 6.1. Optimizing Pipeline Depth

Zyuban, *et al.*, [14] found 18 FO4 delays to be the powerperformance optimal pipeline design point for a singlethreaded microprocessor. The authors also introduced the microarchitectural tuning curves for graphically analyzing a design's relative position in the power-performance space.

Most prior work in optimizing pipeline depth focused exclusively on improving performance. Kunkel, *et al.*, [20] demonstrated that vector code performance is optimized on deeper pipelines while scalar codes perform better on shallower pipelines. Dubey, *et al.*, [21] developed a more general analytical pipeline model to show that the optimal pipeline depth decreases with increasing overhead from partitioning logic between pipeline stages.

More recent research includes finding optimal pipeline designs from simulation. In particular, Hartstein, *et al.*, [22] performed detailed simulations of a four-way superscalar, out-of-order microprocessor with a memory execute pipeline to identify a 10.7 FO4 performance optimal pipeline design for the SPEC2000 benchmarks. Similarly, Hrishkesh, *et al.*, [23] performed simulations for an Alpha 21264-like machine to identify 8 FO4 as a performance optimal design running the SPEC2000 benchmarks.

#### 6.2. SMT, CMP Power-Performance Analyses

Li, *et al.*, [5] performed a comparative performance, power, and temperature analysis on SMT and CMP architectures. The authors found CMP architectures to be more power-performance efficient for CPU bound benchmarks and SMT architectures to be more efficient for memory bound benchmarks. The latter conclusion follows from the fact that SMT architectures are able to have larger L2 caches given a fixed area budget.

Other related work has examined the power-performance efficiency of SMT architectures. Li, *et al.*, [4] studied the efficiency of a POWER4-like architecture while Seng, *et al.*, [24] studied power optimizations for a multi-threaded Alpha processor. Sasanka, *et al.*, [6] and Kaxiras, *et al.*, [25] compare the relative efficiencies of SMT and CMP architectures for multimedia and signal processing workloads, respectively. Similarly, work by Kumar, *et al.*, [26] with heterogeneous CMP cores demonstrates these architectures produce a net increase in efficiency.

Prior studies have also considered hybrids of SMT and CMP designs (*e.g.* two CMP cores, each supporting twoway SMT), concluding that hybrid organizations with N thread contexts are generally inferior to pure CMP architectures with N full cores [6, 26, 27]. This conclusion is also supported in our work (SMT1c2t versus CMP2c1t).

The complexity, power dissipation, and area of interconnect between cores in a CMP architecture become increasing relevant as the number of cores increase [16, 28]. These considerations do not significantly impact the work presented in this paper since we consider CMP architectures with only two cores.

### 7. Conclusions and Future Directions

SMT architectures offer opportunities to efficiently increase pipeline dimensions and, consequently, core complexity. In contrast, reducing pipeline dimensions in CMP cores is potentially power-performance inefficient, assuming ideal power-performance scaling from hardware tuning.

We will continue to develop power scaling techniques for pipeline analysis. Preliminary work in dividing microarchitectural structures into primitive building blocks and performing circuit-level power analyses on these blocks may improve existing analytical power models. We expect this hierarchical modeling scheme will enable faster and more accurate characterization of power scaling trends.

We also intend to consider heterogeneous trace pairs for simultaneous execution in our continuing work. Pairing CPU bound traces with memory bound traces might better utilize architectural resources and demonstrate higher power-performance efficiency.

We take power and performance to be the primary metrics in this study, but area and interconnect effects will become significant as we continue our work in CMP architectures for a larger number of cores. Accounting for these other design parameters and metrics is future work.

We intend to integrate the pipeline depth and width analyses for a more comprehensive understanding of the design space. This is a first step towards developing statistical regression models that will enable architectural designers and researchers to interpolate the power-performance effects of varying a pipeline design parameter without a large number of simulations.

#### References

- R. Kalla, B. Sinharoy, J. Tendler. Power5: IBM's Next Generation Power Microprocessor. In *Proc. 15th Hot Chips Symposium*, Aug 2003.

- [2] D.T. Mar, F. Bins, D.L. Hill, G. Hinton, D.A. Koufaty, J.A. Miller, M. Upton. Hyper-Threading Technology Architecture and Microarchitecture. *Intel Technology Journal*, 6(1), Feb 2002.

- [3] K. Krewell. UltraSPARC IV Mirrors Predecessor: Sun Builds Dual-Core Chip in 130nm. *Microprocessor Report*, Nov 2003.

- [4] Y. Li, D. Brooks, Z. Hu, K. Skadron, P. Bose. Understanding the Energy Efficiency of Simultaneous Multithreading. In *Proc. ISLPED*, Aug 2004.

- [5] Y. Li, D. Brooks, Z. Hu, K. Skadron. Performance, Energy, and Thermal Considerations for SMT and CMP Architectures. In *Proc. HPCA*, Feb 2005.

- [6] R. Sasanka, S.V. Adve, Y.K. Chen, E. Debes. The Energy Efficiency of CMP vs SMT for Multimedia Workloads. In *Proc. ICCD*, Sep 2000.

- [7] M. Moudgill, P. Bose, J. Moreno. Validation of Turandot, a Fast Processor Model for Microarchitecture Exploration. In Proc. IEEE International Performance, Computing, and Communications Conference, Feb 1999.

- [8] M. Moudgill, J. Wellman, J. Moreno. Environment for PowerPC Microarchitecture Exploration. *IEEE Micro*, May/Jun 1999.

- [9] D. Brooks, P. Bose, S. Schuster, H. Jacobson, P. Kudva, A. Buyuktosunoglu, J. Wellman, V. Zyuban, M. Gupta, P. Cook. Power-Aware Microarchitecture: Design and Modeling Challenges for Next-Generation Microprocessors. *IEEE Micro*, Nov/Dec 2000.

- [10] D. Brooks, P. Bose, V. Srinivasan, M. Gschwind, P. Emma, M. Rosenfield. Microarchitecture-Level Power-Performance Analysis: The PowerTimer Approach. *IBM J. Research and Development*, vol. 47, nos. 5/6, 2003.

- [11] J.S. Neely, H.H Chen, S.G. Walker, J. Venuto, T. Bucelot. CPAM: A Common Power Analysis Methodology for High-Performance VLSI Design. In Proc. Ninth Topical Meeting Electrical Performance of Electronic Packaging, 2000.

- [12] V. Iyengar, L.H. Trevillyan, P. Bose. Representative Traces for Processor Models with Infinite Cache. In *Proc. HPCA-2*, Feb 1996.

- [13] V. Zyuban, P. Strenski. Balancing Hardware Intensity in Microprocessor Pipelines. *IBM J. Research and Development*, vol. 47, nos. 5/6, 2003.

- [14] V. Zyuban, D. Brooks, V. Srinivasan, M. Gschwind, P. Bose, P. Strenski, P. Emma. Integrated Analysis of Power and Performance for Pipelined Microprocessors. *IEEE Transactions* on Computers, Aug 2004.

- [15] V. Zyuban. Inherently Lower-Power High-Perfommance Superscalar Architectures. Ph.D. Thesis, University of Notre Dame, Mar 2000.

- [16] K. Ramani, N. Muralimanohar, R. Balasubramonian. Microarchitectural Techniques to Reduce Interconnect Power in Clustered Processors. 5th Workshop on Complexity-Effective Design (WCED), in conjunction with ISCA-31, Jun 2004.

- [17] P. Chaparro, J. Gonzlez and A. Gonzlez. Thermal-Aware Clustered Microarchitectures. *Proc. of the IEEE International Conference on Computer Design*, Oct 2004.

- [18] J.M. Tendler, J.S. Dodson, J.S. Fields, Jr., H. Le, and B. Sinharoy. POWER4 System Microarchitecture. *IBM J. of Research and Development*, vol. 46, no. 1, 2002.

- [19] J.D. Warnock, J.M. Keaty, J. Petrovick, J.G. Clabes, C.J. Kircher, B.L. Krauter, P.J. Restle, B.A. Zoric, and C.J. Anderson. newblock The Circuit and Physical Design of the POWER4 Microprocessor. newblock *IBM J. of Research and Development*, vol. 46, no. 1, 2002.

- [20] S.R. Kunkel, J.E. Smith. Optimal Pipelining in Supercomputers. In Proc. ISCA-13, Jun 1986.

- [21] P. Dubey, M. Flynn. Optimal Pipelining. In J. Parallel and Distributed Computing, 1990.

- [22] A. Hartstein, T.R. Puzak. The Optimum Pipeline Depth for a Microprocessor. In *Proc. ISCA-29*, May 2002.

- [23] M.S. Hrishikesh, K. Farkas, N.P. Jouppi, D.C. Burger, S.W. Keckler, P. Sivakumar. The Optimal Logic Depth per Pipeline Stage is 6 to 8 FO4 Inverter Delays. In *Proc. ISCA-*29, May 2002.

- [24] J. Seng, D. Tullsen, G. Cai. Power-Sensitive Multi-threaded Architecture. In *Proc. ICCD 2000*, 2000.

- [25] S. Kaxiras, G. Narlikar, A.D. Berenbaum, Z. Hu. Comparing Power Consumption of SMT DSPs and CMP DSPS for Mobile Phone Workloads. In *International Conference on Compilers, Architectures, and Synthesis for Embedded Systems*, Nov 2001.

- [26] R. Kumar, K.I. Farkas, N.P. Jouppi, P. Ranganathan, D.M. Tullsen. Single-ISA Heterogeneous Multi-core Architectures: The Potential for Processor Power Reduction. In *Proc. ISCA-31*, Jun 2004.

- [27] J. Burns, J.L. Gaudiot. Area and System Clock Effects on SMT/CMP Processors. In *Proc. PACT 2001*, Sep 2001.

- [28] R. Kumar, V. Zyuban, D. Tullsen. Interconnections in Multi-Core Architectures: Understanding Mechanisms, Overheads and Scaling. In *Proc. ISCA-32*, Jun 2005.

# **Early Performance Prediction**

P. Kudva IBM T.J.Watson Research Center Yorktown Heights, NY

M. Mayo IBM Server and Technology Group Poughkeepsie, NY B. Curran IBM Server and Technology Group Poughkeepsie, NY

S. Carey IBM Server and Technology Group Poughkeepsie, NY S. K. Karandikar IBM Austin Research Lab Austin, TX

S. S. Sapatnekar University of Minnesota Minneapolis, MN

### ABSTRACT

Critical paths and delays of high performance circuits can be accurately identified only in later stages of the design cycle. If the specified clock period is not achievable, changes at the RTL-level may be necessary, leading to re-synthesis and re-validation of the entire design. This, in turn, can cause schedule overruns in the time to market and hence competitiveness of the design. Designers therefore need performance predictors that can identify potential problem areas early in the design flow. In this work, we identify the main characteristics of a design that affect the clock period, and propose models for estimating it at early stages of the design process. Techniques similar to the ones presented in this paper have been evaluated and incorporated into a microprocessor design methodology.

#### 1. INTRODUCTION

Microprocessor designs are complex enough to require a few years from specification to tape-out. Market pressures dictate tight schedules, and overruns in these schedules can be costly not only in monetary terms, but also in the competitiveness of the design. A frequent cause of schedule breakdowns is due to final implementation parameters such as area, power and clock period (and hence frequency) not meeting the original specifications.

In order to evaluate the performance of a design in the early stages of the flow, designers typically use system and microarchitectural models. These can be enhanced to include physical information, such as the effects of long wires between microarchitectural blocks [1, 2]. However, these improvements do not capture the effects of the logic functionality of the design. Arguably, the complexity of the logic being implemented has a big effect on the performance of the design – very complex architectures increase design complexity, thereby adding to cycle time pressures, power consumption as well as verification and validation challenges. Additionally, changes to complex microarchitecture require significant redesign effort, and can cause schedule slips.

It is therefore imperative to have a methodology to evaluate the hardware complexity of early microarchitectures, to allow for adequate exploration of the system space. Further, as the microarchitecture is implemented in an HDL, these early estimations should become more accurate. Determining complexity from microarchitectural models themselves is an objective of ongoing and future research. In this paper, we focus on early RTL models derived in the process of converting microarchitectural models to RTL specifications. In the early stages of this step, RTL specifications are crude and incomplete. Additionally, technology rules for gates/wires may not be available, and have to be extrapolated from past technologies. As implementation progresses, the RTL is further refined and more technology specific information is available. Such incomplete specifications cannot be synthesized, and it is therefore difficult to use well known synthesis-based early estimation techniques [3–5,7] to estimate design complexity. Estimating the performance of such incomplete designs is still necessary to provide early feedback to microarchitects.

In this scenario, if designers were to be provided a metric for estimating design performance *early* in the design flow, they would be able to better identify potential problem areas, and would be able to use this information to guide their design process. In this work, we address the *clock period* of the design, which is possibly the most visible parameter of the final product.

In order to avoid costly iterations of the design cycle, we propose models that allow a designer to quickly determine which signal paths are critical, and focus his or her efforts on these areas. Feedback is also provided to microarchitects regarding extremely challenging paths in order to consider changes. Since this information is made available early in the design process, we hope to avoid expensive redesign, resynthesis and revalidation. The models provide information that both the logic designers and microarchitects can use to make intelligent choices between different available implementations. Additionally, we can also identify paths that are non-critical; these can then be targeted for aggressive pipeline rebalancing, area or power optimization.

We have analyzed a number of macros in the various units of a latest-generation microprocessor. In the following sections we present the results of this analysis, and propose a number of models that can be used at different stages of the design flow to estimate the delay of an implementation. As the design is successively refined, more data becomes available, and our proposed models can use this data to provide more accurate data. We have tried to abstract out technology dependent parameters from our models, so that they can be used for different technology generations. Rather than absolute accuracy, our goal is to be able to predict which parts of the circuit could prove to be problematic, and therefore need more attention from designers.

We first put our contributions in context by describing the typical microprocessor design flow. We then present the data accumulated and our analysis of this data, followed by various predictive models. We conclude with a discussion of additional approaches and future research directions

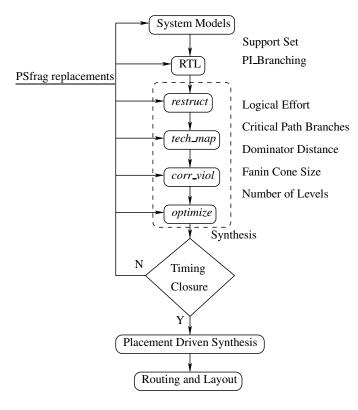

#### 2. DESIGN FLOW

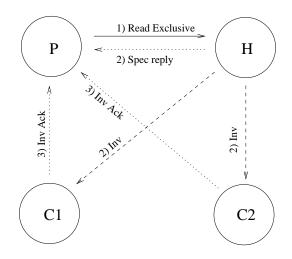

Figure 1 shows a typical, albeit simplified design flow of a high performance, complex microprocessor. At the initial stages, only system models are available. These define stages in the pipeline, the flow of data and interactions between these stages, along with

Figure 1: Typical Design Flow

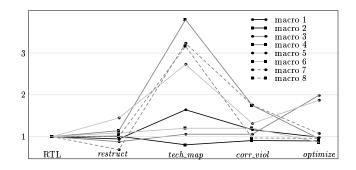

cycle accurate models. Logic designers use these models to implement control logic in a HDL. This is the stage where the design starts assuming a concrete form. Signals are initially defined in terms of boolean equations, and as RTL is developed and synthesized, we obtain a logic gate level netlist. At each stage of synthesis, the design is successively refined. Initial technology independent optimizations such as kernel factoring, literal minimization, etc. (performed at the step labelled restruct), are followed by technology mapping (tech\_map), where the design is mapped to a specific technology library. This is followed by a number of technology dependent transformations for correcting violations (corr\_viol) and further design optimizations (optimize), which use gate and wire sizing, buffer insertion, etc. Not surprisingly, the delay of the design can vary wildly during synthesis. As an example of how much the design changes, Figure 2 presents the delays of critical paths in a number of industrial circuits at different points during synthesis, normalized to the delay at the RTL stage. Not only do the values of critical path delays change, but the actual critical paths themselves can vary quite widely from pre-RTL to the final circuit. In some cases, the final delays after synthesis are close to the initial delays, while in others they are twice as large. As is obvious, these delay values fluctuate in a wide range during the synthesis transforms, being smaller than the initial values in some cases, and larger in others.

Figure 1 also shows a few parameters that are defined and analyzed in the following section. We point out here that these parameters are available at different stages of the design flow; initially only structural parameters such as the support set and PI\_Branching (which will be defined shortly) can be calculated, while parameters such as logical effort, size of fanin cone, etc. are determined as the design is implemented and synthesized.

Once a mapped, optimized circuit is obtained, its delay can be

Figure 2: Delay Variation During Synthesis

accurately measured. If the implemented circuit meets the original specifications, the design continues to the next stages of placement, layout and routing, and can go on to silicon fabrication. However, if the delay of the circuit at this stage does not meet the original specification, the designer has to return to preceding stages in the design process and attempt to fix these violations. Depending on how much difference there is in the implementation versus the specification, changes have to be made at different stages of the design flow. All changes require re-synthesis, which can be expensive. In addition, validation, which usually runs concurrent with synthesis, and which has its own cost, has to be repeated. Even small changes, if made at the RTL (or earlier) stages can be expensive, if they affect a large portion of the design. Thus, any loops in the design flow caused by timing closure issues can cause schedule slips, which in turn affect the time that a design can be brought to market.

Prediction, at an early stage, need not be very accurate – even separating the circuit into high, medium and low delay critical portions provides more information than currently available. There is greater freedom to make changes in the design at early stages, and the effect of changes made early in the design flow is greater. Hence, the earlier a designer has an estimate of the performance of the design, the greater the benefit of any predictor. We develop models that can estimate delays as the designer is starting to implement RTL. The accuracy of these models is limited due to the limited design properties available at this stage. As the design matures, our predictors provide successively accurate delay models.

#### 3. PARAMETERS AFFECTING DELAY

#### 3.1 Preliminaries

A combinational path is a path without any latches. The clock period of a design is defined by the length(delay) of the longest combinational path. This critical path may be from primary inputs or latches to primary outputs or latches. We only consider paths between latches, since a path containing a primary input (output) of a macro may be part of a larger combinational path that crosses macro boundaries.

Referring once again to Figure 1, different design properties are available at different stages. The first stage in the design development is the RTL description of the circuit. At this point, the only information available for each primary output is the size of its support set. After *restruct*, which applies technology independent optimizations to the circuit, coarse information on the number of levels and branching is available, but these can change significantly in the following steps. The following step, labelled *tech\_map* is the technology mapping step, where cells are mapped to actual library elements. At this stage, we can take all the data available into consideration. However, we note once again that this is subject to further refinement by following optimizations. The last step in the physical synthesis process is *optimize*, where optimizations such as gate sizing are applied. At this point, the entire spectrum of data is available, since this is at a point very close to the final circuit.

This availability of design properties is also presented in Figure 1. Parameters such as support set and PI branching are available early in the design process. These have some bearing on the delay of a design. Parameters that have a much larger effect on the delay, such as logical effort and branching, on the other hand, are available only after the design is completed. However, a designer can make an educated guess as to the values of these parameters early in the design cycle, and we can potentially use these **Diffugs opherements** building predictors. Note that even after a design has been finalized and is passed on the the next steps, placement and routing can introduce long wires into the design. At today's circuit geometries, wire delays are of the same order as device delays and cannot be ignored. Long wires have to be buffered, and this can significantly change the number of levels.

#### **3.2** Discussion of Parameters

We now present the design properties under consideration and hypothesize as to their effect on actual delay. Section 4 describes how this data is used in building prediction models that characteristic in microprocessor design methodologies.

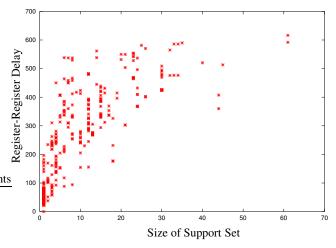

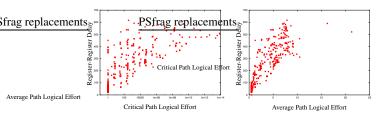

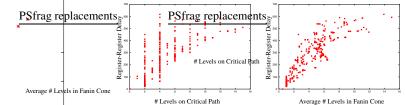

1. **Support Set** (Figure 3): The support set is the number of PLBranching primary inputs driving the fanin cone of a primary output. It is an invariant that does not change during synthesis. A larger support set implies more complicated logic, and hence greater delay. Even if the logic is simple, combining a large support set requires that the signals pass through more levels of logic, hence increasing the delay. The logarithm of the support set can give us a lower bound on the number of levels of logic in the design, and we hypothesize that the delay of the design depends directly on this value.

Figure 3 is a plot of the delay (after synthesis) versus the support set of a number of combinational logic paths. As indicated by the upper right region, outputs with large support sets have large delays. For outputs with small support sets (the points to the left of the plot), we observe a larger variation in delay. This effect is due to the synthesis process – since these paths are not critical, delay is traded off for area. However, a clearly defined lower bound on the delay, as a function of the size of the support set can be observed. This indicates that a design with a large support set will have large delays, but when the size of the support set is smaller, other parameters have a greater influence on the delay. Thus, a good delay estimator will have to include a combination of different parameters.

2. PI\_Branching (Figure 4): We count the number of primary outputs driven by each primary input, and then for a primary output, we calculate the accumulation (the sum or the product) of the number of primary outputs driven by all inputs in the support set of this primary output. This parameter is called the PI\_Branching of an output. This parameter indicates how "self-contained" the fan-in cone of an output is. A low value corresponds to an independent cone of logic, while a larger value implies divided loyalties – the logic is driving multiple outputs. A primary input driving more than one primary output will have divergent paths *somewhere* in the circuit. This divergence implies that a larger electrical

Figure 3: Delay Vs. Size of Support Set

Figure 4: Delay Vs. PL\_Branching

load that has to be driven, which directly leads to a larger delay. PI\_Branching captures this effect at the output of a cone of logic.

In Figure 4, the first plot presents the delay versus *product* and the second figure plots the delay versus the *sum* of the number of primary outputs driven by each input in the support set. These plots seems to indicate that there is a weak correlation between the delay and PI\_Branching, but our models show a surprisingly strong effect on the estimating function, as shown in the following section.

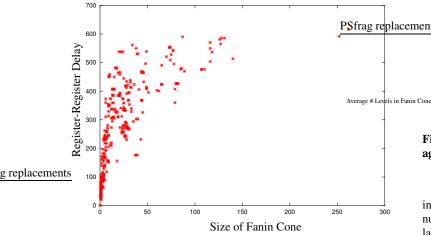

3. Size of Fan-in Cone (Figure 5): The size of the fanin-in cone is the number of gates in the fan-in cone of the primary output under consideration. This naturally changes as synthesis proceeds, and can only be determined at later stages of the design. Intuitively, the more logic driving a given output, the slower it will be. This can be seen by the plot.

Note that this parameter has to be used with care, since the same functionality can be implemented with either one complex gate or a number of simple gates. The choice of which solution is selected depends on a number of factors, but the effect on the size of the fan-in cone can be at odds with the effect on delay.

4. **Branching** (Figure 6): We calculate the accumulated product of the fanouts of each gate on the path under consideration. In general, the larger the branching, the greater the load that has to be driven, which increases the delay of that path. We present the branching on the critical path as well as the average branching over all paths, normalized by the path length.

Figure 5: Delay Vs.Size of Fan-in Cone

Figure 6: Delay Vs. Path Branching(Critical Path and Average)

- 5. Logical Effort (Figure 7): Logical effort measures the com-Number of Levels (Figure 8): This is simply the number of levels of logic that a signal traverses from input to output. Intuitively, delay is directly proportionally to this value. However, this depends on the load being driven: it <u>can be shown</u>

- 6. Number of Levels (Figure 8): This is simply the number of of levels converges after technology mapping and buffering, and can be reliably used only may the aginal teffort x PL Branching ]

#### **MODELS FOR DELAY PREDICTION** 4.

Figure 7: Delay Vs. Path Logical Effort (Critical Path and Average)

#### Figure 8: Delay Vs. Number of Levels (Critical Path and Average)

A direct correlation between delay and the parameters presented in the previous section seems logical - the larger the support set, number of levels and fan-in cone size, the greater the expected delay. However, this is not true for smaller values of these parameters. As mentioned before, this can be due to a number of different factors, such as synthesis optimizing for area or power (and therefore increasing delay) in non-critical portions of the design. Sometimes the discrepancies are due to the nature of the parameters themselves - the logical effort of a long chain of buffers is low, but the delay of such a chain can be large.

The above data therefore provides us with a lower bound on the delay; given a value of support set, say, we can be relatively sure of the minimum achievable delay. The data presented in the previous section shows this general trend to varying degrees. With this data in hand, we now attempt to determine which parameters can be used to predict delay, how these parameters can be combined, and reason why the parameters play the role that they do.

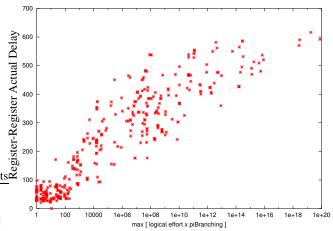

Figure 9: Delay Vs. max (Logical Effort × PI\_Branching)

Consider the previous example of a long chain of buffers, which have a low value of logical effort, but high delay. The single parameter of logical effort, by itself, does not predict the large delay. However, a parameter such as the number of levels would indicate that the delay of such a chain will be high. Thus, while we cannot estimate delay as a function of a single parameter, combinations of different parameters can potentially serve as better delay estimators. The reasoning is that each parameter captures one aspect of the design, and the correct combination of these will be able to capture the overall nature of the design.

As another example of the correlation between a combination of the above parameters and delay, refer to Figure 9. For every cone of logic, we obtain the maximum value of the product of the logi-

Figure 10: Estimated Vs. Actual Delay (Functions 1-3)

cal effort and the PI\_Branching, analogous to the product of logical effort and electrical effort when calculating the gain of individual gates in the method of logical effort [6]. The improvement as compared to previous data is immediately apparent – the lower bound seen before is maintained, while a rough upper bound can be discerned.

An interesting point to note is that all the parameters that we have presented are dimensionless. In order to determine the best models for predicting delay, we are therefore free to determine the delay dependency - be it a linear, quadratic, exponential or some other function of a selected parameter. In the rest of this section, we hypothesize on the relation between delay and different parameters, and test these hypotheses by comparing the difference in actual and estimated delay.

The parameters are used in the order they are available to the designer, as shown in Figure 1. We start with the support set and PI\_Branching, and then expand the models to include the remaining parameters.

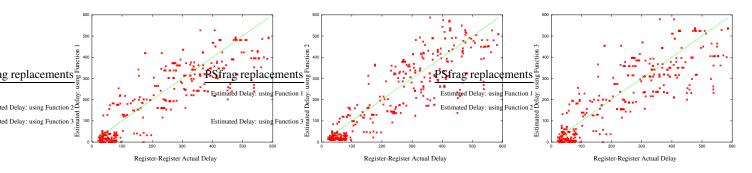

#### **Function 1**

At the initial stages of the design, the only parameters available are the support set (*ss*) and PI\_Branching. Our first attempt is based on the assumption that delay is possibly a linear function of the log of two parameters, i.e. *delay*  $\alpha$  log *ss* + log *PI\_Branching*. The intuition behind this assumption is as follows. We have observed in the previous section that the support set gives a reasonable lower bound on the delay (Figure 3). However, for logic that has small support sets but higher delay, this parameter by itself is insufficient. The second parameter available to us at this stage is PI\_Branching, which is included to account for these circuits. However, this model had significantly large errors, which can be reduced by introducing a combination of support set and PI\_Branching:

$$delay = k_1 \cdot \log ss + k_2 \cdot \log PI\_Branching + k_3 \cdot \log ss \times \log PI\_Branching$$

(1)

We then perform regression analysis using Equation 1 and available data in order to determine the the values of coefficients  $k_1, k_2$  and  $k_3$  so that the difference between the actual delay and the function in Equation 1 is minimized. The values of these coefficients also indicate the relative importance of the corresponding term.

The average error is 23%, with a standard deviation of 57 *ps*. Figure 10(a) plots the estimated delay using this function versus the actual delay. As mentioned previously, these coefficients are specific to the technology that this circuit will

be implemented in. However, they do indicate the relative importance of each parameter, and therefore such a weighted function of support set and PI\_Branching can be used in other technology generations as well.

#### Function 2

We next add quadratic functions of support set and PI\_Branching,

$$delay = k_1 \cdot \log ss + k_2 \cdot \log PI\_Branching + k_3 \cdot (\log ss)^2 + k_4 \cdot (\log PI\_Branching)^2 + k_5 \cdot \log ss \times \log PI\_Branching$$

(2)

obtaining an average error of 25% with a standard deviation of 58 *ps*. Figure 10(b) plots the estimated delay using this function Vs the actual delay.

As in the previous model, the relative weights of the *ss* and PI\_Branching parameters are similar multiples of the combined *ss* and PI\_Branching parameter. The coefficients of the quadratic versions of these parameters are attenuated, in fact these do not contribute to accurate delay estimation at all, only increasing the error. This indicates that the quadratic terms are not needed when estimating delay.

#### Function 3

In this model, we include the average logical effort of the cone of logic under consideration. Though the exact value is not available at early stages, designers can make an educated guess based on the complexity of the logic to be implemented.

$$delay = k_1 \cdot \log ss + k_2 \cdot \log PI\_Branching + k_3 \cdot (\log ss)^2 + k_4 \cdot (\log PI\_Branching)^2 + k_5 \cdot \log ss \times \log PI\_Branching + k_6 \cdot leAvg + k_7 \cdot \log ss \times leAvg + k_8 \cdot \log PI\_Branching \times leAvg$$

(3)

The estimated delay using this function, plotted against the actual delay in Figure 10(c) has an average error of 26% and a standard deviation of 56 ps. Note that the regressions also

indicate the relative effect of each term on the delay, by proportionately increasing / decreasing the coefficients. This can guide us towards better models. For example, the dominant term in this model is the average logical effort. We will possibly get better results by removing the quadratic terms, this is currently under investigation.

#### Function 4

Finally, we use the product of PI\_Branching and logical effort. The intuition for the delay dependence on these parameters in this model is as follows. The first term,  $\log ss$ , accounts for the inherent delay of an implementation – no matter what the actual logic being implemented, all the signals in the support set have to be combined at the output. The second term – PI\_Branching × LE is analogous to an *RC* delay – the logical effort estimates the complexity of the logic, while PI\_Branching accounts for the different loads being driven by that logic. This is the simplest and most accurate model:

$delay = k_1 \times \log ss$  $+ k_2 \times \log (\max (PI\_Branching \times LE))$ (4)

This has an the best average error and standard deviation among all the functions, of 20% and 47 ps respectively.

We build our models based on the assumption that the above parameters capture information that can be used to predict the delay of a cone of logic. Combinations of parameters obviously provide a better estimate than parameters taken singly. Unfortunately, there are an exponentially large number of ways in which these parameters can be combined to generate delay estimates. The functions presented above are a first cut, and only examine a fraction of all possibilities.

#### 5. APPLICATION METHODOLOGY

The estimators presented in this paper were evaluated within a microprocessor design methodology in a number of different scenarios. Firstly, based on the maturity of the design, the appropriate function is selected. At early stages of the design process, since only limited data is available, Function 1 can be used to estimate delay. During intermediate stages, one of the other functions are selected. As the designer gets a better estimate of the complexity of the design being implemented, Function 4, which uses parameters that were unknown before, can be used to estimate the delay of different portions of the circuit. Thus, as the design progresses, more parameters are determined, which are subsequently used in increasingly accurate estimating functions.

As a high level design is evaluated, the architectural performance models are also converted into early VHDL representations for analysis purposes. At this stage, the VHDL models are not intended for synthesis but for quick estimation to evaluate complexity of the designs. Cycle time delays are estimated for different parts of the processor pipeline datapath and controller and a determination is made regarding whether the high level design is able to meet cycle time. If the early estimations show that architectural assumptions were impractical from a logic design point of view, this information is fed back to the architect for a change in the high level architectural design.

If on the other hand, the timing is challenging but not impractical, then the logic design for that partition is identified and additional resources would be assigned to them. In addition, they are meant to guide the logic designer in writing the VHDL description that will improve the timing critical sections. Note, once again, that these models are not intended to estimate the actual delays, rather they help the designer divide the circuit into parts that have high delay, and hence are critical, and the remainder, which are not, thus helping them focus their attention where required. At each stage, optimizations can be applied only when required, and the target of these optimizations (delay, area, power) can be determined based on how critical that circuit is. Aggressive optimizers take more time to run, and the above models can be used to determine the required degree of optimization.

Our estimators are also used to determine the effect of floorplanning changes, which are made all throughout the design process. In early stages of the design cycle, it is necessary to know the effect of floorplan changes on the timing of the design. On the other hand, at these stages, the RTL descriptions are not complete or only partially available. When critical paths cross partition/macro boundaries, it is necessary to evaluate whether the floorplan can meet the timing requirement. Fast estimation of timing during the floorplanning process is essential. Estimates for each partition are recalculated throughout as the design floorplan begins to converge as well as when the contents of the partitions begin to stabilize. The timing estimates for the macros are combined with timing estimation at the chip level including interconnect estimation to derive the overall cycle time, thus allowing the designers to monitor the cycle time as the floorplan changes and the design evolves.

The results of such early analysis methodology is fed back as well as forward to microarchitects, logic designers, physical designers and floorplanners. These estimates prove invaluable in making early changes to the design point from all these different design considerations.

#### 6. CONCLUSION AND FUTURE WORK

In this paper, we present a methodology at predicting cycle time of a proposed design *early* in a microprocessor design flow. Though the error in the predicted values may seem significant in absolute terms, it is important to note that these predictions are based on extremely coarse data and provide more information to designers than currently available. Also, we have a high level of fidelity with actual delays, which, at early stages of the design is more important than accuracy. An extended version of the work presented in this paper has been implemented in a microprocessor design methodology. In the methodology, the estimates are used both to provide feedback to the architects in selecting optimal high level designs as well as to the logic designers, floorplanners and physical designers to aid them in meeting challenging cycle time objectives.

The estimation approach presented in this paper continues to be refined to be able to capture methodology issues much earlier in the design process [8]. Methods for generating estimates even earlier in the design flow can be implemented by directly taking into account microarchitectural parameters (pipeline depth, branch prediction algorithm complexity, renaming algorithms etc) along with logic design parameters (wiring, cycle time, area, power). These models are currently being evaluated as part of current and future directions for this research.

#### 7. REFERENCES

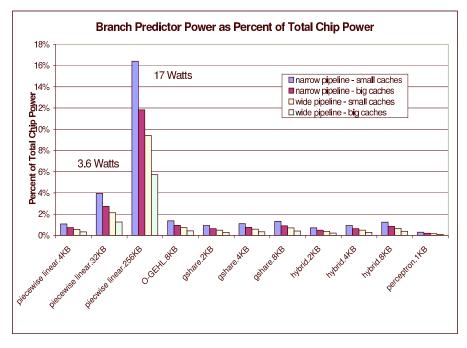

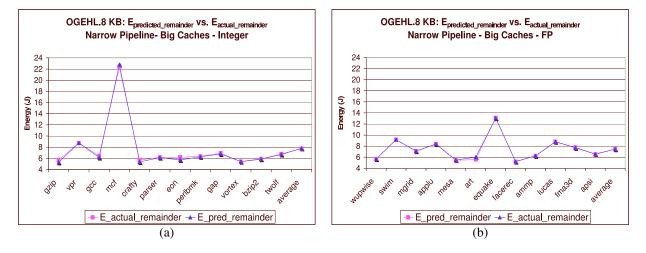

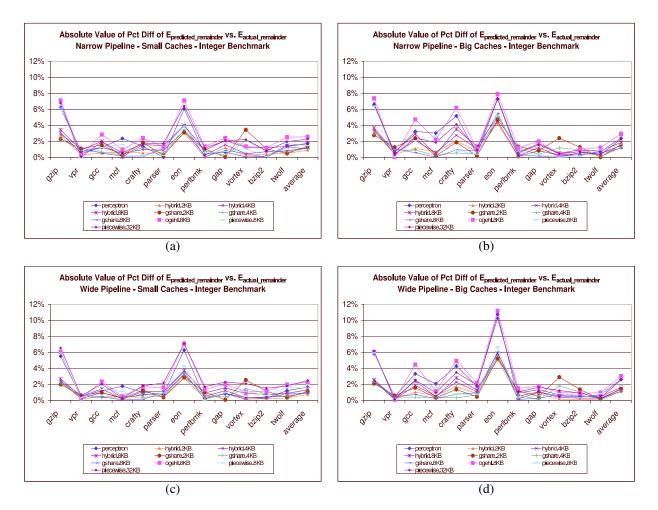

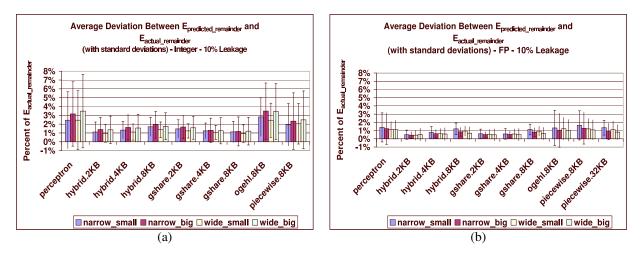

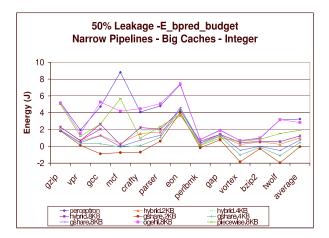

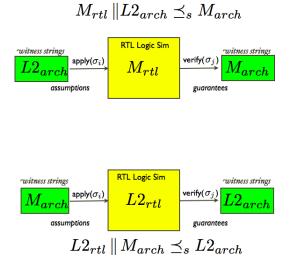

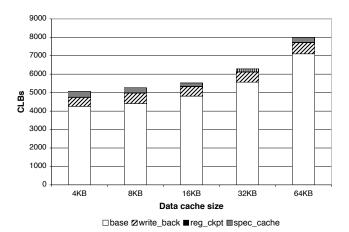

- CONG, J., JAGANNATHAN, A., REINMAN, G., AND ROMESIS, M. Microarchitecture evaluation with physical planning. In *Proc. ACM/IEEE Design Automation Conference* (2003), pp. 32–36.