# ECE 6775 High-Level Digital Design Automation Fall 2023

# **More Scheduling**

#### **Announcements**

- Lab 1 graded

- Only 2 integer bits needed for the fixed-point design

- Lab 2 due tomorrow

- Lab 3 will be released soon

- Virtual lecture next Tuesday

# **Agenda**

- ILP for time-constrained scheduling

- Heuristic algorithms for constrained scheduling

- List scheduling

- SDC-based scheduling

# **Exercise: Formulating ILP**

- Minimize the number of classrooms that the school must allocate for the following courses

- Steps to formulate the ILP

- (1) Create variables

- (2) Each course to be scheduled to exactly one of the preferred slots

- (3) Determine the number of rooms required (by creating new derived variables)

- (4) Set up the objective function

| Course | Preferred<br>Slots |  |

|--------|--------------------|--|

| А      | (1) (2)            |  |

| В      | (1) (3)            |  |

| С      | (2) (3)            |  |

| D      | (2)                |  |

- (1) 8:00 10:00am

- (2) 10:00am 12:00pm

- (3) 12:00 2:00pm

1 x<sub>i,s</sub>: course i uses slot s

②

$$X_{A,1} + X_{A,2} = 1$$

③  $r_1 = X_{A,1} + X_{B,1}$

$X_{B,1} + X_{B,3} = 1$   $r_2 = X_{A,2} + X_{C,2} + X_{D,2}$

$X_{C,2} + X_{C,3} = 1$   $r_3 = X_{B,3} + X_{C,3}$

$x_{C,3} = 1$

4 Objective: min max {r1, r2, r3}

Linearize min R

$$R \ge r_1$$

,  $R \ge r_2$ ,  $R \ge r_3$

# **Time-Constrained Scheduling (TCS)**

- Dual problem of resource-constrained scheduling

- Overall latency is given as a constraint (deadline)

- Minimize the total cost in terms of area (or resource usage), power, etc.

- NP-hard problem

- ILP formulation is exact but is not a polynomial-time solution

- Force-directed scheduling is a well-known heuristic for TCS (see De Micheli chapter 5.4.4)

# **Example: ILP Formulation for TCS**

ILP for time-constrained scheduling

minimize c<sup>T</sup>y

$$\begin{aligned} x_{1,1} + x_{2,1} + x_{6,1} + x_{8,1} &\leq y_1 \\ x_{3,2} + x_{6,2} + x_{7,2} + x_{8,2} &\leq y_1 \\ x_{7,3} + x_{8,3} &\leq y_1 \\ x_{5,4} + x_{9,4} + x_{11,4} &\leq y_2 \end{aligned}$$

What does the y vector represent?

# Recap: Constrained Scheduling in HLS

- Constrained scheduling

- General case NP-hard

- Resource-constrained scheduling (RCS)

- Minimize latency given constraints on area or resources

- Time-constrained scheduling (TCS)

- Minimize resources subject to bound on latency

- Exact methods

- Integer linear programming (ILP)

- Hu's algorithm for a very restricted problem

- Heuristics

- List scheduling

- Force-directed list scheduling

- SDC-based scheduling

. . .

# **List Scheduling**

- A widely-used heuristic algorithm for RCS

- Schedule one control step (cycle) at a time

- Maintain a list of "ready" operations considering dependence

- Assign priorities to operations; most "critical" operations (with the highest priorities) go first

- Often refers to a family of algorithms

- Typically classified by the way priority function is calculated

- Static priority: Priorities are calculated once before scheduling

- Dynamic priority calculation: Priorities are updated during scheduling

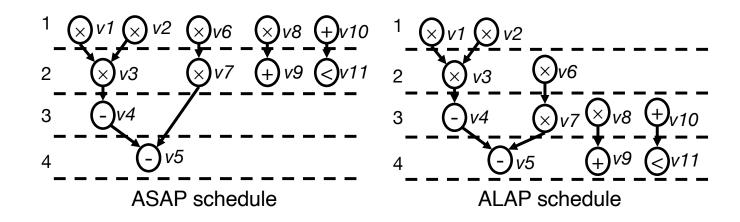

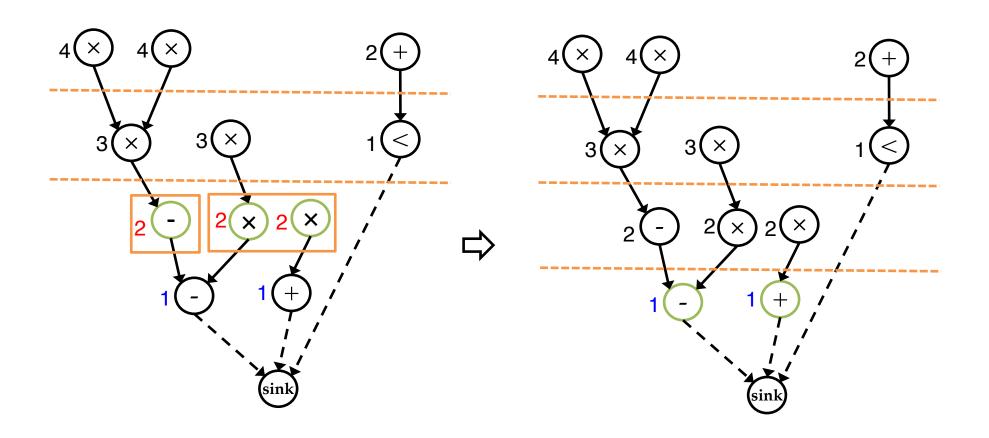

# **Static Priority Example: Node Height**

Nodes are labelled with distance to sink (height)

Ready operations are colored in green

- Assumptions:

- All operations have unit delay

- 2 MULTs, 1 AddSub, and 1 CMP available

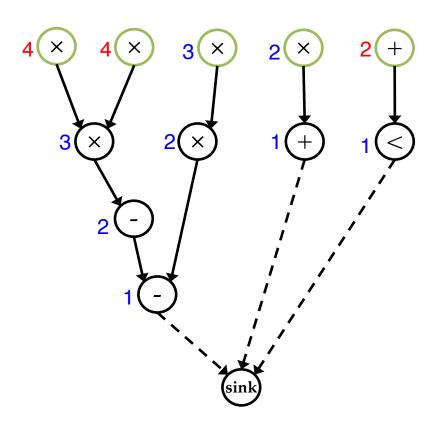

# **Ready Nodes with Highest Priorities Picked First**

- Assumptions:

- All operations have unit delay

- 2 MULTs, 1 AddSub, and 1 CMP available

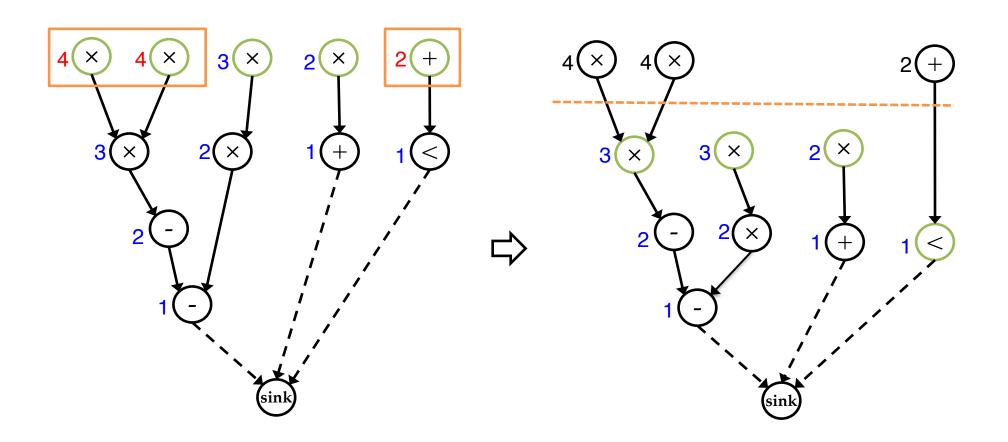

# **Update Ready Nodes and Repeat for Each Step**

- Assumptions:

- All operations have unit delay

- 2 MULTs, 1 AddSub, and 1 CMP available

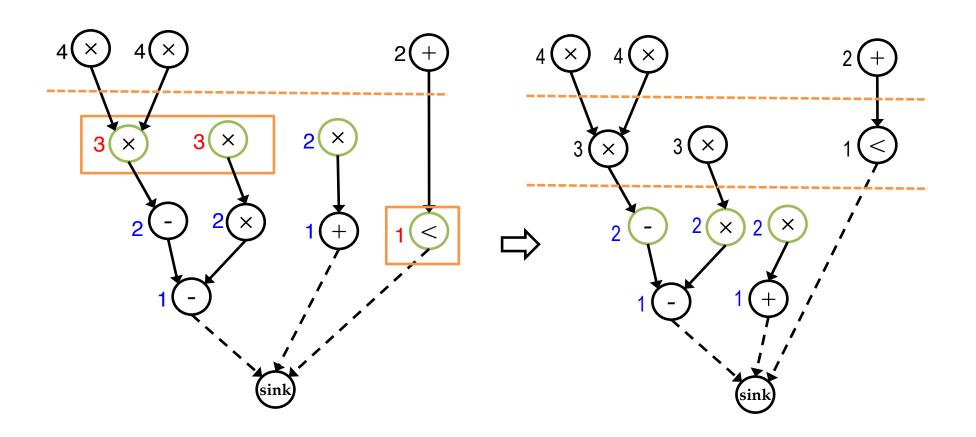

# **Update Ready Nodes and Repeat for Each Step**

- Assumptions:

- All operations have unit delay

- 2 MULTs, 1 AddSub, and 1 CMP available

# Repeat Until All Nodes Scheduled

- Assumptions:

- All operations have unit delay

- 2 MULTs, 1 AddSub, and 1 CMP available

# A Special Case

- With the following (very) restrictive conditions:

- All operations have unit delay (i.e., single cycle)

- All operations (and resources) are of the same type

- Graph is a forest

- List scheduling with static height-based priorities guarantees optimality

- This is known as Hu's algorithm

- T. C. Hu, Parallel sequencing and assembly line problems.

Operations Research, 9(6), 841-848, 1961

- Guarantees

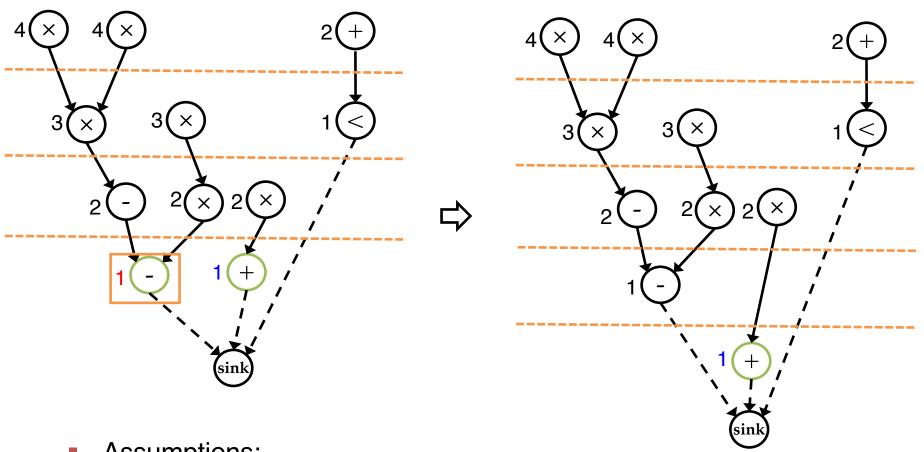

# HLS Scheduling: Tension between Scalability and Quality

# **More Realistic Scheduling Problems**

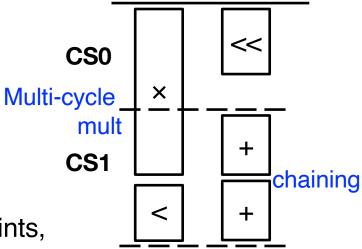

- Operation chaining

- More compact schedule

- Multi-cycle operations

- Nonpipelined or pipelined

- Higher frequency

- Mutually exclusive operations

- Scheduled in the same step, but with mutually exclusive execution conditions

- Higher resource utilization

- Other timing constraints

- Frequency constraints, latency constraints, relative time constraints

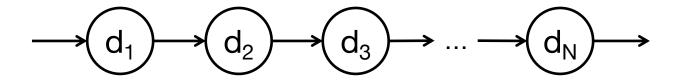

# **A Simple Operation Chaining Problem**

**Given:** A chain of n operations. Without any registers, the cycle time equals the total combinational delay, which is  $D = sum(d_i)$ .

**Question:** How to place TWO registers on the chain to achieve the minimum cycle time?

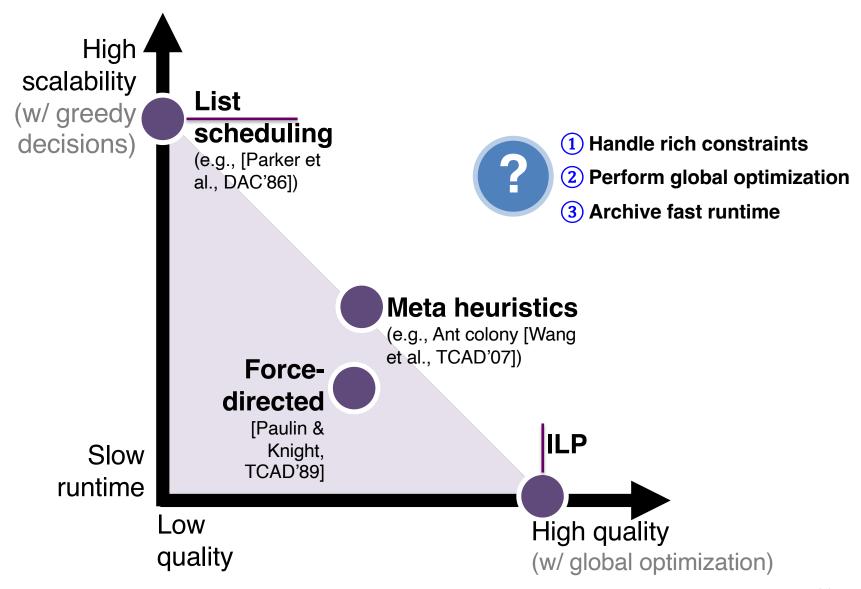

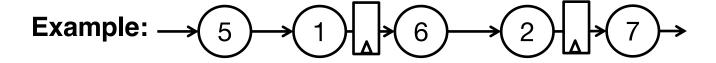

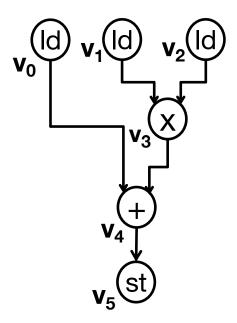

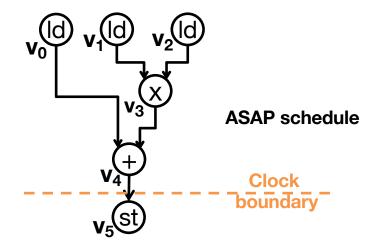

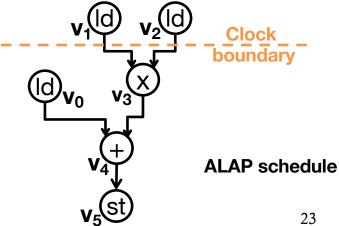

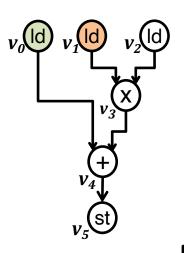

# **SDC-Based Scheduling**

SDC = System of difference constraints

$\mathbf{s}_i$ : schedule variable for operation i

Dependence constraints

$$| > < V_0 , V_4 > : S_0 - S_4 \le 0$$

Timing constraints

- Target cycle time: 5ns

- Delay estimates

- Mul (x): 3ns

- Add (+): 1ns

- Load/Store (ld/st): 1ns

Cycle time constraints

$$v_1 \rightarrow v_5 : s_1 - s_5 \le -1$$

$$\rightarrow$$

$v_2 \rightarrow v_5 : s_2 - s_5 \le -1$

To meet the cycle time,  $v_2$  and  $v_5$  should have a minimum separation of one cycle

# **Exercise: Latency Constraint in SDC**

How to enforce that operations  $\mathbf{v_3}$  and  $\mathbf{v_4}$  are not chained and at most two cycles apart?

#### **Difference Constraints**

- A difference constraint is a formula in the form of  $x y \le b$  or x y < b for numeric variables x and y, and constant b

- With scheduling variables, we use integer difference constraints to model a variety of scheduling constraints

- x and y must have integral values

- Thus *b* only needs to be an integer => form x-y < b is redundant

#### **SDC Constraint Matrix**

- The constraint matrix of SDC(X, C) is a totally unimodular matrix (TUM):

- Every nonsingular square submatrix has a determinant of -1/+1.

$$\left( \begin{array}{c} 1 \ 0 \ 0 \ 0 \ -1 \ 0 \ 0 \\ 0 \ 1 \ 0 \ -1 \ 0 \ 0 \\ 0 \ 0 \ 1 \ -1 \ 0 \ 0 \\ 0 \ 0 \ 0 \ 1 \ -1 \ 0 \\ 0 \ 0 \ 0 \ 0 \ -1 \\ 0 \ 1 \ 0 \ 0 \ 0 \ -1 \\ 0 \ 1 \ 0 \ 0 \ 0 \ -1 \\ \end{array} \right) \ \leq \ \left( \begin{array}{c} 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ -1 \\ -1 \end{array} \right)$$

$$A \qquad \qquad X \qquad \qquad b$$

- Theorem (Hoffman & Kruskal, 1956): If A is totally unimodular and b is a vector of integers, every extreme point of polyhedron {x : Ax ≤ b} is integral.

- Solving linear programming (LP) relaxation leads to integral solutions

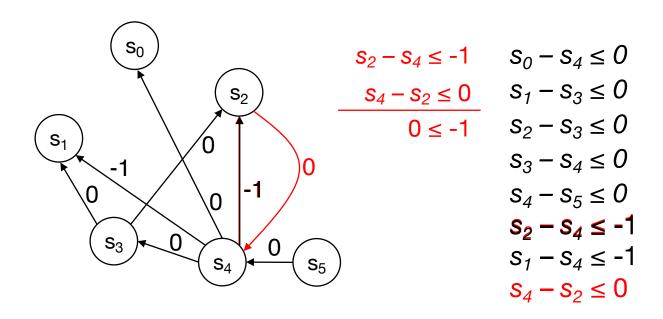

# **SDC Constraint Graph**

- Difference constraints can be conveniently represented using constraint graph

- Each vertex represents a variable, and each weighted edge corresponds to a different constraint

- Detect infeasibility by the presence of negative cycle (by solving single-source shortest path)

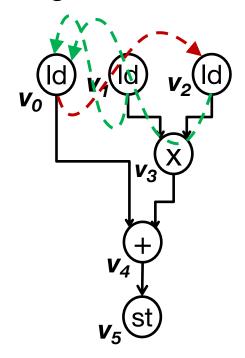

#### **Handling Resource Constraints (NP-Hard in General)**

Resource constraints cannot be represented exactly in integer difference form

- Resource constraint

- Two read ports

- Resource constraints

- → Heuristic partial orderings

$$v_0 \rightarrow v_2 : s_0 - s_2 \le -1$$

3 cycle latency

OR

$$v_1 \rightarrow v_0 : s_1 - s_0 \le -1$$

$v_2 \rightarrow v_0 : s_2 - s_0 \le -1$  2 cycle latency

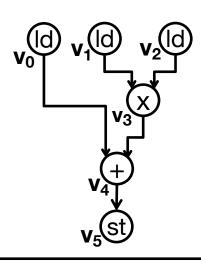

# **Linear Objectives**

ASAP: min  $\sum_{i \in V} s_i$

ALAP:  $\max \sum_{i \in V} s_i$

Minimum latency: min  $\max_{i \in V} \{s_i\}$

Minimum average case latency (control-intensive design)

Many other ...

$\min s_0 + ... + s_5$

- Target cycle time: 5ns

- Delay estimates

- Mul (x): 3ns

- Add (+): 1ns

- Load/Store (ld/st): 1ns

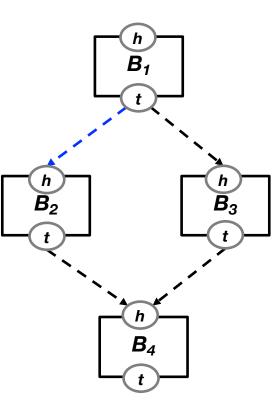

# **Control Flow Graphs**

- Control dependencies can also be honored

- If bb<sub>2</sub> is control dependent on bb<sub>1</sub>, the operation nodes of bb<sub>2</sub> are not allowed to be scheduled before those of bb<sub>1</sub>

- Polarize each basic block bb<sub>i</sub>

with two scheduling variables (head and tail)

•

$$\forall v \in bb_i$$

,  $s_h(bb_i) - s_h(v) \leq 0$

•

$$\forall v \in bb_i$$

,  $s_t(v) - s_t(bb_i) \leq 0$

- If  $e_c(bb_i, bb_i) \in E_c$  and  $e_c$  is not a back edge

•

$$s_t(bb_i) - s_h(bb_i) \le 0$$

$$s_t(B_1) - s_h(B_2) \le 0$$

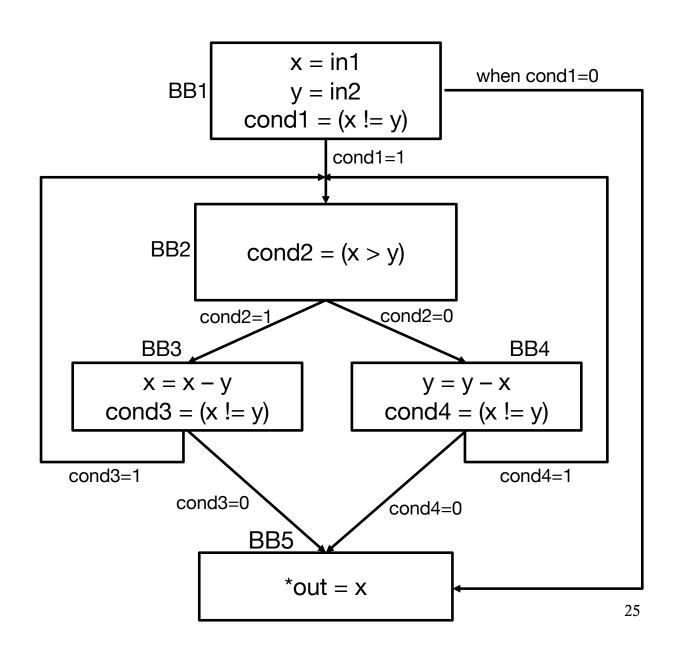

# **Example: Greatest Common Divisor (GCD)**

```

x = in1;

y = in2;

while (x != y) {

if ( x > y )

x = x - y;

else y = y - x;

}

*out = x;

```

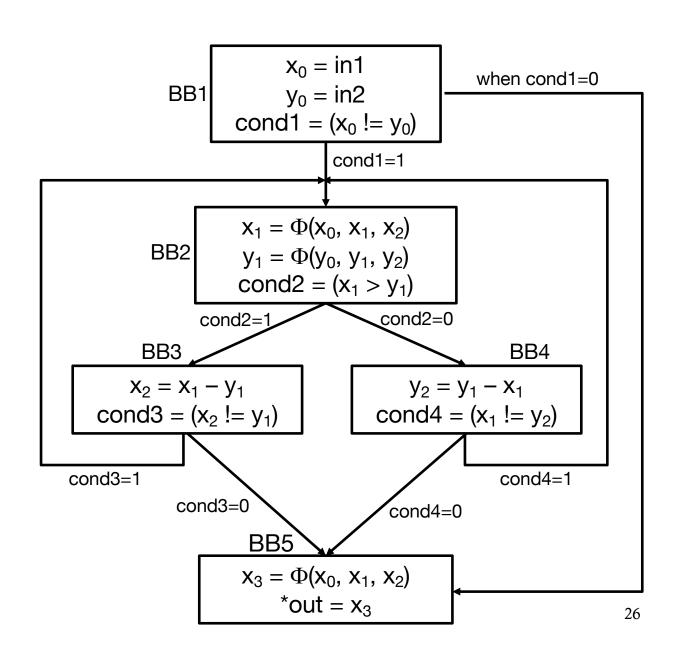

#### **GCD** in SSA form

```

x = in1;

y = in2;

while (x != y) {

if (x > y)

x = x - y;

else y = y - x;

}

*out = x;

```

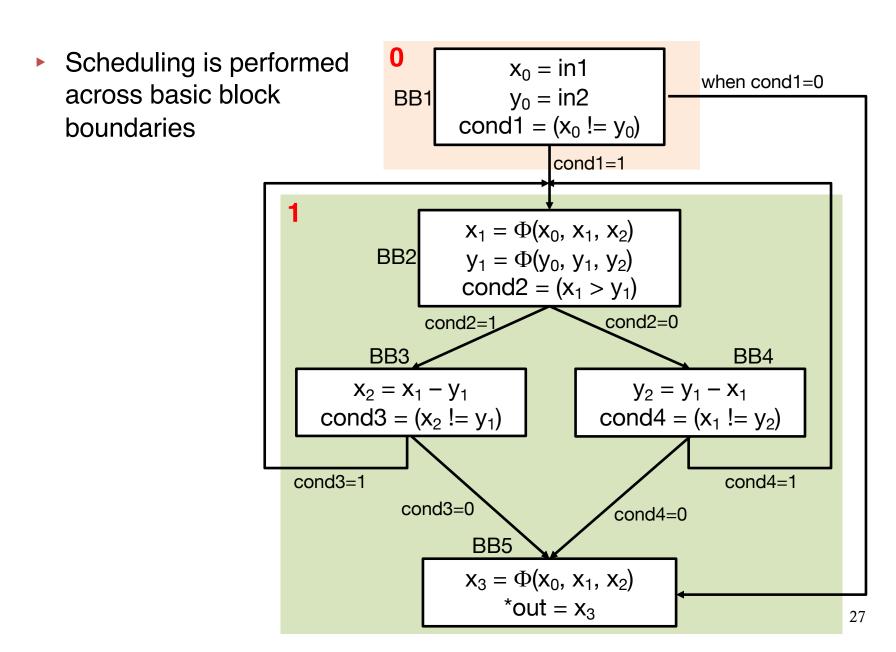

# Interpreting the LP Solution of SDC Scheduling

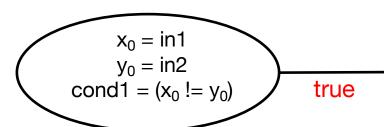

# **Operations and Predicates**

$$x_0 = in1$$

$y_0 = in2$

$cond1 = (x_0 != y_0)$

1  $x_1 = \Phi(x_0, x_1, x_2)$   $y_1 = \Phi(y_0, y_1, y_2)$   $cond2 = (x_1 > y_1)$   $x_2 = x_1 - y_1$   $cond3 = (x_2 != y_1)$   $y_2 = y_1 - x_1$   $cond4 = (x_1 != y_2)$   $x_3 = \Phi(x_0, x_1, x_2)$ \*out = x<sub>3</sub>

Add predicates for conditionally executed operations in each state

```

x_0 = \text{in1}

y_0 = \text{in2}

\text{cond1} = (x_0 != y_0)

```

```

If (cond1) {

x_1 = \Phi (x_0, x_1, x_2)

y_1 = \Phi (y_0, y_1, y_2)

cond2 = (x_1 > y_1)

if (cond2) {

x_2 = x_1 - y_1

cond3 = (x_2 != y_1)

} else {

y_2 = y_1 - x_1

cond4 = (x_1 != y_2)

}

if (!cond1 || (!cond3 && !cond4)) {

x_3 = \Phi (x_0, x_1, x_2)

*out = x_3

```

# **Deriving State Transition Graph (STG)**

Predicates for operations and state transitions can be derived from original control flow and dominance analysis

```

(cond1) {

x_1 = \Phi(x_0, x_1, x_2)

y_1 = \Phi (y_0, y_1, y_2)

cond2 = (x_1 > y_1)

if (cond2) {

X_2 = X_1 - Y_1

cond3 = (x_2 != y_1)

} else {

y_2 = y_1 - x_1

cond4 = (x_1 != y_2)

if (!cond1 || (!cond3 && !cond4))

x_3 = \Phi(x_0, x_1, x_2)

*out = x_3

```

!cond1 && (cond3 || cond4)

# \*Exact Encoding of Resource Constraints

#### Two read ports only!

Load operations must be serialized,

(**NP-Hard** in general)

|         | Port1 Port2 DSP       |                       |                       |

|---------|-----------------------|-----------------------|-----------------------|

| cycle=1 | <b>v</b> <sub>0</sub> | <b>V</b> <sub>2</sub> |                       |

| cycle=2 | V <sub>1</sub>        |                       | <b>V</b> <sub>3</sub> |

| cycle=3 |                       | <b>V</b> <sub>5</sub> | V <sub>4</sub>        |

OR

| PORT PORZ DSP  |                       |                       |  |  |

|----------------|-----------------------|-----------------------|--|--|

| V <sub>1</sub> | <b>v</b> <sub>2</sub> | <b>V</b> <sub>3</sub> |  |  |

| V <sub>0</sub> | V <sub>5</sub>        | V <sub>4</sub>        |  |  |

D = 44 D = 40 D C D

$$\bigcirc$$

$$s_0 - s_1 \neq 0$$

$$s_0 - s_1 \leq -1$$

$$\underset{\mathsf{OR}}{\mathsf{OR}}$$

$$s_1 - s_0 \le -1$$

#### Resource sharing variable $R_{0,1}$ $v_0$ and $v_1$ share the same port?

Ordering variable  $\mathbf{0}_{\mathbf{0}\to\mathbf{1}}$  v<sub>0</sub> scheduled before v<sub>1</sub>?

$v_1$  scheduled before  $v_0$ ?

**Note:**  $R_{0,1} \rightarrow (O_{0\rightarrow 1} \vee O_{1\rightarrow 0})$  reads " $R_{0,1}$  implies  $O_{0\rightarrow 1}$  or  $O_{1\rightarrow 0}$ "

Difficult to exactly encode resource constraints in the strict SDC form

**Using Boolean formulas instead**

# \*SDS: Exact and Practically Scalable Scheduling with SDC and SAT

**Partial Difference** orderings constraints  $S_0 - S_4 \leq 0$  $R_{01} \to (0_{0 \to 1} \lor 0_{1 \to 0})$  $s_1 - s_3 \le 0$  $\neg (0_{0 \rightarrow 1} \land 0_{1 \rightarrow 0})$  $s_2 - s_3 \le 0$ SAT SDC  $R_{02} \rightarrow (O_{0\rightarrow 2} \lor O_{2\rightarrow 0})$  $S_3 - S_4 \le 0$ **Timing** Resource  $\neg (0_{0\rightarrow 2} \land 0_{2\rightarrow 0})$  $s_4 - s_5 \le 0$ **Constraints Constraints**  $R_{12} \to (O_{1 \to 2} \lor O_{2 \to 1})$  $s_2 - s_5 \le -1$  $\neg (0_{1\rightarrow 2} \land 0_{2\rightarrow 1})$  $S_1 - S_5 \le -1$ **Infeasibility** Conflict clauses **Conflict based Graph based** feasibility checking search Polynomial time ~1M variables Conflict-driven learning >1M clauses

# **Scheduling Summary**

- ► ILP

- Exact, but exponential worst-case runtime

- Hu's algorithm

- Optimal and polynomial

- Only works in very restricted cases

- List scheduling

- Extension to Hu's for general cases

- Greedy (fast) but suboptimal

- SDC-based scheduling

- A versatile heuristic based on LP formulation with different constraints

- Amenable to global optimization

### **Next Lecture**

- Resource sharing

- Pipelining concepts

# **Acknowledgements**

- These slides contain/adapt materials developed by

- Ryan Kastner (UCSD)