# ECE 6745 Complex Digital ASIC Design Tutorial 4: PyMTL3 Hardware Modeling Framework

School of Electrical and Computer Engineering Cornell University

revision: 2025-01-27-21-27

# Contents

| 1 | Intro     | Introduction                                                         |    |  |  |  |

|---|-----------|----------------------------------------------------------------------|----|--|--|--|

| 2 | PyM       | PyMTL3 for Functional-, Cycle-, and Register-Transfer-Level Modeling |    |  |  |  |

|   | 2.1       | Comparison of FL, CL, and RTL Modeling                               | 4  |  |  |  |

|   | 2.2       | Synthesizable vs. Non-Synthesizable RTL Modeling                     | 4  |  |  |  |

| 3 | PyM       | PyMTL3 Basics: Data Types and Operators                              |    |  |  |  |

|   | 3.1       | Bits Data Type                                                       | 5  |  |  |  |

|   | 3.2       | Bits Operators                                                       | 7  |  |  |  |

|   | 3.3       | BitStruct Data Type                                                  | 11 |  |  |  |

| 4 | Regi      | Registered Incrementer                                               |    |  |  |  |

|   | 4.1       | Modeling a Registered Incrementer                                    | 12 |  |  |  |

|   | 4.2       | Ad-Hoc Testing Using PyMTL3                                          | 14 |  |  |  |

|   | 4.3       | Visualizing a Model with Line Traces                                 | 16 |  |  |  |

|   | 4.4       | Visualizing a Model with Text-Based Waveform                         | 17 |  |  |  |

|   | 4.5       | Visualizing a Model with VCD Waveforms                               | 17 |  |  |  |

|   | 4.6       | Verifying a Model with Unit Testing                                  | 20 |  |  |  |

|   | 4.7       | Verifying a Model with Test Vectors                                  | 24 |  |  |  |

|   | 4.8       | Verifying a Model with Random Testing                                | 27 |  |  |  |

|   | 4.9       | Reusing a Model with Structural Composition                          | 28 |  |  |  |

|   | 4.10      | Parameterizing a Component with "Static" Elaboration                 | 31 |  |  |  |

|   | 4.11      | Packaging a Collection of Models                                     | 35 |  |  |  |

| 5 | Sort Unit |                                                                      |    |  |  |  |

|   | 5.1       | FL Model of Sort Unit                                                | 37 |  |  |  |

|   | 5.2       | CL Model of Sort Unit                                                | 39 |  |  |  |

|   | 5.3       | Flat RTL Model of Sort Unit                                          | 42 |  |  |  |

|   | 5.4  | Structural RTL Model of Sort Unit             | 45 |  |  |  |  |  |

|---|------|-----------------------------------------------|----|--|--|--|--|--|

|   | 5.5  | Evaluating Sort Unit using a Simulator        | 47 |  |  |  |  |  |

|   | 5.6  | Translating RTL Model of Sort Unit to Verilog | 49 |  |  |  |  |  |

|   |      |                                               |    |  |  |  |  |  |

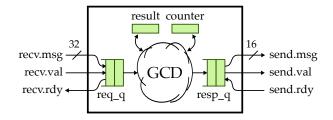

| 6 | Grea | reatest Common Divisor Unit                   |    |  |  |  |  |  |

|   | 6.1  | FL Model of GCD Unit                          | 53 |  |  |  |  |  |

|   | 6.2  | CL Model of GCD Unit                          | 58 |  |  |  |  |  |

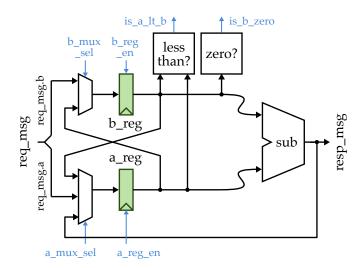

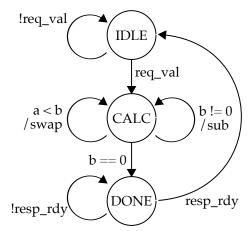

|   | 6.3  | RTL Model of GCD Unit                         | 62 |  |  |  |  |  |

|   | 6.4  | Exploring the GCD Implementation              | 65 |  |  |  |  |  |

|   |      |                                               |    |  |  |  |  |  |

## 1. Introduction

In the lab assignments for this course, we will be using Verilog for register-transfer-level modeling and the PyMTL3 hardware modeling framework for writing functional-level models, test benches, and simulator harnesses. The previous tutorial on the Verilog hardware description language already provided a good introduction to using PyMTL3 which should be suitable for the lab assignments. However, the design projects will likely require students to write their own functional-level models, test benches, and simulator harnesses from scratch. This tutorial provides much more detail about the PyMTL3 framework by essentially reproducing what you learned in the previous tutorial but using PyMTL3. As in the previous tutorial, we will be using several open-source packages and tools: the pytest framework for powerful test-driven Python development; Verilator (verilator) for converting Verilog models into C++ source code; and Surfer/GTKWave for viewing waveforms. The PyMTL3 framework is itself open source and available on GitHub here:

• https://github.com/pymtl/pymtl3

We are using the pymtl4.0-dev branch:

• https://github.com/pymtl/pymtl3/tree/pymtl4.0-dev

You should feel free to browse the source code for PyMTL3 on GitHub if you want to see more how various aspects of the framework are implemented. These tools are installed and available on the ecelinux machines. This tutorial assumes that students have completed the Linux and Git tutorials, and also that students have a basic understanding of Python.

If you need to refresh your understanding of Python, we highly recommend working through the book by Allen Downey titled "Think Python: How to Think Like a Computer Scientist" (O'Reilly, 2014). We also recommend reading a recent research paper on PyMTL3 by Shunning Jiang et al. titled "PyMTL3: A Python Framework for Open-Source Hardware Modeling, Generation, Simulation, and Verification" and published in IEEE Micro. Both of these resources are available on the course website.

Before you begin, make sure that you have **logged into the** ecelinux **servers** using VS Code as described in the remote access tutorial. To follow along with the tutorial, type the commands without the % character (for the bash prompt) or the >>> characters (for the python interpreter prompt). In addition to working through the commands in the tutorial, you should also try the more open-ended tasks marked with the **★** symbol.

Before you begin, make sure that you have **sourced the setup-ece6745.sh script**, and then clone the tutorial repository from GitHub.

```

% source setup-ece6745.sh

% mkdir -p ${HOME}/ece6745

% cd ${HOME}/ece6745

% git clone git@github.com:cornell-ece6745/ece6745-tut4-pymtl.git tut4

% cd tut4/sim

% TUTROOT=${PWD}

```

**NOTE:** It should be possible to experiment with this tutorial even if you are not enrolled in the course and/or do not have access to the course computing resources. All of the code for the tutorial is located on GitHub. You will not use the setup-ece6745.sh script, and your specific environment may be different from what is assumed in this tutorial.

## 2. PyMTL3 for Functional-, Cycle-, and Register-Transfer-Level Modeling

Computer architects can model systems at various levels of abstraction including at the: functionallevel (FL), cycle-level (CL), and register-transfer-level (RTL). In this section, we provide a brief overview of these different levels of modeling and also provide more detail on the difference between synthesizable and non-synthesizable RTL modeling.

## 2.1. Comparison of FL, CL, and RTL Modeling

Each level of modeling has its own unique advantages and disadvantages, so the most effective designers uses a mix of these modeling levels as appropriate. This tutorial will use various examples to illustrate how to incrementally refine a design through FL, CL, and RTL models. Although it is useful for students to understand CL modeling (and indeed most computer architects focus primarily on CL modeling), the actual lab assignments will focus on FL and RTL modeling.

**Functional-Level** – FL models implement the *functionality* but not the timing of the hardware target. FL models are useful for exploring algorithms, performing fast emulation of hardware targets, and creating golden models for verification of CL and RTL models. FL models can also be used for building sophisticated test harnesses. FL models are usually the easiest to construct, but also the least accurate with respect to the target hardware.

**Cycle-Level** – CL models capture the *cycle-approximate behavior* of a hardware target. CL models will often augment the functional behavior with an additional timing model to track the performance of the hardware target in cycles. CL models are usually specifically designed to enable rapid design-space exploration of cycle-level performance across a range of microarchitectural design parameters. CL models attempt to strike a balance between accuracy, performance, and flexibility.

**Register-Transfer-Level** – RTL models are *cycle-accurate, resource-accurate,* and *bit-accurate* representations of hardware. RTL models are built for the purpose of verification and synthesis of specific hardware implementations. RTL models can be used to drive EDA toolflows for estimating area, energy, and timing. RTL models are usually the most tedious to construct, but also the most accurate with respect to the target hardware.

In this tutorial, FL, CL, and RTL models all use port-based interfaces, concurrent blocks, and structural composition. Note that PyMTL3 supports more advanced polymorphic interface connection which directly connects interfaces at different levels by automatically inserting adapters. Both the port-based approach and the polymorphic approach enable PyMTL3 to support mixed-level modeling, i.e., combining FL, CL, and RTL models of various subsystems into a single unified system model.

## 2.2. Synthesizable vs. Non-Synthesizable RTL Modeling

Keep in mind that PyMTL3 is embedded within Python, which is a fully general-purpose language. Given this, it is very easy to write PyMTL3 code that does not actually model any kind of realistic hardware. When using PyMTL3 for RTL modeling we need to be very careful to use only the subset of PyMTL3 which can be translated to Verilog. However, in this course students' design work will primarily be in Verilog, and we will primarily be using PyMTL3 for writing functional-level modeling, test benches, and simulator harnesses. Students can use any Python construct they like in their functional-level models, test benches, and simulator harnesses.

## 3. PyMTL3 Basics: Data Types and Operators

We will begin by writing some very basic code to explore PyMTL3 data types and operators. We will not be modeling actual hardware yet; we are just experimenting with the framework. Start by launching the Python interpreter and importing the PyMTL3 framework into the global namespace.

```

% mkdir -p ${TUTROOT}/build

% cd ${TUTROOT}/build

% python

>>> from pymt13 import *

```

#### 3.1. Bits Data Type

To understand any new modeling framework we usually start by exploring the primitive data types for representing values in a model. PyMTL3 uses the Bits class to represent fixed-bitwidth values. Note that in many hardware description languages (HDLs) each bit can take on one of four values (i.e., 0, 1, X, Z), where X is used to represent unknown values and Z is used to represent highimpedence values. In PyMTL3 each bit can only take on one of two values (i.e., 0, 1). We say that these other HDLs support *four-state values* while PyMTL3 supports *two-state values*. Both approaches have advantages and disadvantages. Two-state values produces faster simulations and avoid many of the pitfalls of using X values; but some hardware constructs are a bit more verbose to describe when only two-state values are available. Using two-state values also raises issues with properly handling reset logic, although there are well-known techniques to address these issues. Figure 1 shows an example session in the Python interpreter that illustrates how to instantiate and manipulate Bits objects. Type the commands into the Python interpreter and observe the output.

PyMTL3 already offers common Bits types from Bits1-255. A BitsN constructor takes one argument specifying the initial value. Remember that in Python, a *variable* is just a *name* that refers to a value or object. So on line 2, we create a new variable with the name a that refers to a new Bits16 object and an initial value of 37. Also recall that values and objects belong to different types, and that the type of a variable is the type of the value or object it refers to. As shown on line 4, the type of a is Bits16. We might also say that a holds an *in*stance of type Bits16. Lines 9–11 show what happens if we assign a new integer value to the name a. It does not update the Bits object but instead simply updates the name a to now refer to a plain integer value 47. Lines 13-15 shows an alternative (and possibly more succinct) way of using bN types to create constants. Line 17–24 shows how to create wider Bits types by using mk\_bits(N). mk\_bits can also be used to create Bits types that must be derived from some statically unknown bitwidth.

Lines 26–30 show how to use standard Python syntax to specify numeric literals in binary or hexadecimal form. Lines 32-38 demonstrate that negative initial values are also possible. These negative values are stored using two's complement. The Bits constructor includes dynamic range checking and will throw an exception if the given literal value cannot be stored using the given number of bits. Lines 40-45 illustrate one example where 300 is too large to be stored in just eight bits. Lines 47–49 illustrate the optional Bits constructor trunc\_int argument that will truncate initial values which are too large to store in the given number of bits. Lines 51–58 shows how to extract number of bits and the unsigned/signed integer value from a Bits object.

★ To-Do On Your Own: Experiment with creating Bits objects of different bitwidths and various initial values. Experiment with the trunc argument to truncate large initial values.

```

1 # BitsN takes an initial value

2 >>> a = Bits16( 37 )

_3 \implies type(a)

4 <class 'pymtl3.datatypes.bits_import.Bits16'>

5 >>> a

6 Bits16(0x0025)

7 >>> str(a)

s '0025'

9 >>> a = 47

10 >>> type(a), a

11 (<class 'int'>, 47)

12

13 # bN recommended for creating constants

14 >>> b16(37)

15 Bits16(0x0025)

16

17 # Creating wider Bits types

18 >>> Bits260

19 ...

20 NameError: name 'Bits260' is not defined

_{21} >>> N = 260

22 >>> BitsN = mk_bits(260)

23 >>> BitsN( 37 )

24 Bits260(0x000000...0000025)

25

26 # Using binary and hexadecimal literals

27 >>> Bits8( 0b10101100 )

28 Bits8(Oxac)

29 >>> Bits32( 0xabcd0123 )

30 Bits32(0xabcd0123)

31

32 # Negative values stored in two's complement

33 >>> Bits8( -1 )

34 Bits8(0xff)

35 >>> Bits8( -2 )

36 Bits8(Oxfe)

37 >>> Bits8( -128 )

38 Bits8(0x80)

39

40 # Initial values that cannot be stored with

41 # given bitwidth throw an exception

42 >>> Bits8( 300 )

43 . . .

44 ValueError: Value 0x12c is too wide for Bits8!

45 (Bits8 only accepts -0x80 <= value <= 0xff)

46

47 # Truncating initial values

>>> Bits8( Oxdeadbeef, trunc_int=True )

48

49 Bits8(Oxef)

50

51 # Getting number of bits and value

52 >>> a = Bits8( 128 )

53 >>> a.nbits

54 8

55 >>> a.uint()

56 128

57 >>> a.int()

```

```

58 -128

```

Figure 1: Creating Bits Objects

Figure 2 shows another example session in the Python interpreter that illustrates how to slice and copy Bits objects. Type these commands into the Python interpreter and observe the output.

Bits objects are sequences of bits, so we can use standard Python syntax to specify bit slices for reading or writing fields within a Bits object. Note that Python slices always start with the index of the first bit in the slice and end with one past the last bit in the slice. For example, the slice a[28:32] on line 4 produces a new four-bit Bits object with the most-significant four bits from a.

Line 20 illustrates how to create two different names that refer to the same Bits object. Since there is only a single Bits object, if we modify that object using the name a (line 25), then later accesses to that object using either name will reflect this change (line 27 and 29). In other words, simply assigning a to b on line 20, *does not copy the object*. To copy the object, we must create a new Bits object as shown on line 33.

★ To-Do On Your Own: Create two new Bits objects: one with a bitwidth of 32 and the other with a bitwidth of eight. Assign the smaller Bits object to the middle of the larger Bits object using slices. Continue to experiment with creating Bits objects of different bitwidths and then using slices to read and write various fields within these Bits objects.

```

1 # Python slices for reading fields

2 >>> a = Bits32( 0xabcd0123 )

3 >>> a[28:32]

4 Bits4(0xa)

5 >>> a[4:24]

6 Bits20(0xcd012)

7

8 # Python slices for writing fields

9 >>> a = Bits32( 0xabcd0123 )

10 >>> a[28:32] = 0xf

11 >>> a

12 Bits32(0xfbcd0123)

13 >>> a[4:24] = 0x210cd

14 >>> a

15 Bits32(0xfb210cd3)

16

# Creating two names that refer to

17

18 # the same Bits object

19 >>> a = Bits32( 0xabcd0123 )

20 >>> b = a

21 >>> a

22 Bits32(0xabcd0123)

<sub>23</sub> >>> b

24 Bits32(0xabcd0123)

25 >>> a[24:32] = 0x67

26 >>> a

27 Bits32(0x67cd0123)

<sub>28</sub> >>> b

29 Bits32(0x67cd0123)

30

31 # Copying a Bits object

32 >>> a = Bits32( 0xabcd0123 )

33 >>> b = Bits32( a )

34 >>> a

35 Bits32(0xabcd0123)

36 >>> b

37 Bits32(0xabcd0123)

38 >>> a[24:32] = 0x67

39 >>> a

40 Bits32(0x67cd0123)

41 >>> b

42 Bits32(0xabcd0123)

```

Figure 2: Slicing and Copying Bits Objects

#### 3.2. Bits Operators

Table 1 shows the Bits operators that we will be primarily using in this course. Note that Python supports additional operators including / for division, % for modulus, and other generic Python object manipulation functions. These operators are not translatable, so students should avoid using these operators in their RTL models.

| Log         | gical Operators                          | Reducti                                                                           | on Operators | R                      | <b>Relational Operators</b>                                |  |  |

|-------------|------------------------------------------|-----------------------------------------------------------------------------------|--------------|------------------------|------------------------------------------------------------|--|--|

| &<br> <br>~ | bitwise AND<br>bitwise OR<br>bitwise XOR | reduce_and reduce via AND<br>reduce_or reduce via OR<br>reduce_xor reduce via XOR |              | ==<br>!=<br>>          | equal<br>not equal<br>greater than                         |  |  |

| Arith       | bitwise NOT                              | Shift Operators >> shift right                                                    |              | >=<br><<br><=          | greater than or equals<br>less than<br>less than or equals |  |  |

| +           | addition<br>subtraction                  | >> shift<br><< shift                                                              | 0            |                        | Other Functions                                            |  |  |

| *           | multiplication                           |                                                                                   |              | sext<br>zext<br>concat | sign-extension<br>zero-extension<br>concatenate            |  |  |

**Table 1:** Bits **Operators** – Obviously there are many other operations that can be used with Bits objects, but these are guaranteed to be translatable.

Figure 3 shows an example session in the Python interpreter that illustrates how to use basic logical and reduction operators with Bits objects. Type these commands into the Python interpreter and observe the output. Note that the reduction operators produce single-bit Bits objects.

Lines 15–20 illustrate support for implicit operand conversion. When operators are applied to a mix of Bits objects and standard integer values, PyMTL3 attempts to implicitly convert the standard integer values into Bits objects. However, as lines 22-27 suggests, performing binary arithmetics between two Bits objects with different bitwidths will result in type mismatch. The solution is to use sext, zext or trunc to match the bitwidth of the two operands, as shown later in Figure 5

★ *To-Do On Your Own:* Write a Python function that implements a full adder. It should take three one-bit Bits objects as operands and return a Python tuple containing two one-bit Bits objects corresponding to the carry out and sum bits.

Write a Python function that returns true if two Bits objects are equal using just the bitwise XOR operators and the reduction operators.

```

1 # Logical operators

2 >>> a = Bits4( 0b1010 )

3 >>> b = Bits4( 0b1100 )

4 >>> a & b

5 Bits4(0x8) # 0b1000

6 >>> a | b

7 Bits4(0xe) # 0b1110

8 >>> a ^ b

Bits4(0x6) # 0b0110

9

10 >>> a ^ ~b

11 Bits4(0x9) # 0b1001

12 >>> ~a

Bits4(0x5) # 0b0101

13

14

15 # Implicit operand conversion

16 >>> a = Bits4( 0b1010 )

17 >>> a & Ob1100

18 Bits4(0x8) # 0b1000

19 >>> Ob1100 & a

20 Bits4(0x8) # 0b1000

21

22 # Type mismatch errors

23 >>> a = Bits4( 0b1010 )

24 >>> a & Bits5( 0b1100 )

25

. . .

26 ValueError: Operands of '&' (and) operation must

have matching bitwidth, but here Bits4 != Bits5.

27

28

29 # Reduction operators

30 >>> a = Bits8( 0b10101100 )

31 >>> reduce_and(a)

32 Bits1(0x0)

33 >>> reduce_or(a)

34 Bits1(0x1)

35 >>> reduce_xor(a)

36 Bits1(0x0)

```

Figure 3: Bits Logical and Reduction Operators

Figure 4 shows an example session in the Python interpreter that illustrates how to use the shift, arithmetic, and relational operators with Bits objects. Type these commands into the Python interpreter and observe the output.

Lines 3–13 illustrate left and right shift operators that can use either a standard integer value or a Bits object as the shift amount. The right shift operator is a logical shift and inserts zeros in the mostsignificant bit positions. The bitwidth of the result from a shift is always the same as the first operand to the shift operator.

Lines 17–37 illustrate addition and subtraction operators. The bitwidth of the result is always the max of the bitwidths of the two operands. These operators perform modular arithmetic. On line 20, the result of 3 + 15 is 18 which is represented in binary as 10010 but the result is truncated to four bits. Negative numbers are converted to two's complement before performing the addition.

Lines 41–54 illustrate relational operators for comparing two Bits objects. The less than and greater than operators always treat the operands as unsigned.

★ To-Do On Your Own: Try writing some code which does a sequence of additions resulting in overflow and then a sequence of subtractions that essentially undo the overflow. For example, use an eight-bit Bits object to calculate 200 + 100 + 100 - 100 - 100. Does this expression produce the expected answer even though the intermediate values overflowed?

Write a Python function that does a signed lessthan comparison between two Bits objects of any bitwidth. You will need to use the nbits attribute to determine the sign bit for each Bits object, and handle all four cases where either operand can be positive or negative.

```

1 # Shift operators

2

>>> a = Bits4( 0b1011 )

3

4 >>> a << 2

5 Bits4(0xc) # 0b1100

6 >>> a >> 2

7 Bits4(0x2) # 0b0010

>>> b = Bits4( 2 )

9

10 >>> a << b

Bits4(0xc) # 0b1100

11

>>> a >> b

12

Bits4(0x2) # 0b0010

13

14

# Arithmetic operators

15

16

>>> a = Bits4(3)

17

18 >>> a + 2

19 Bits4(0x5)

20 >>> a + 15

21 Bits4(0x2)

22 >>> a - 2

23

Bits4(0x1)

24 >>> a - 15

Bits4(0x4)

25

26

>>> b = Bits4( 2 )

27

28 >>> a + b

29 Bits4(0x05)

30 >>> a - b

31 Bits4(0x01)

32

>>> c = Bits4( -2 )

33

34 >>> a + c

Bits4(0x01)

35

>>> a - c

36

Bits4(0x05)

37

# Relational operators

39

40

_{41} >>> a = Bits4(3)

42 >>> b = Bits4(2)

43 >>> a == b

44 Bits1(0x0)

45 >>> a != b

Bits1(0x1)

46

>>> a > b

47

Bits1(0x1)

48

>>> a >= b

49

50 Bits1(0x1)

51 >>> a < b

52 Bits1(0x0)

53 >>> a <= b

Bits1(0x0)

54

```

Figure 4: Bits Shift, Arithmetic, and Relational Operators Figure 5 shows an example session in the Python interpreter that illustrates functions for concatenating, zero extending, and sign extending Bits objects. Type these commands into the Python interpreter and observe the output.

Lines 1–7 illustrate concatenating two Bits objects using the concat function. Lines 9–14 illustrate concatenating more than two Bits objects. Note that one can only concatenate actual Bits objects as opposed to integer literals since the exact bitwidth of a decimal or hexadecimal integer literal is ambiguous.

Lines 16–28 illustrate using the sext and zext functions to sign extend and zero extend a Bits object to the given larger bitwidth. Lines 30–33 illustrate using the trunc function to truncate a Bits object to the given smaller bitwidth.

★ To-Do On Your Own: Experiment with different variations of concatenation to create interesting bit patterns.

```

1 # Concatenation

2 >>> a = Bits8( 0xab )

3 >>> b = Bits12( 0xcde )

_4 >>> concat(a, b)

5 Bits20(Oxabcde)

6 >>> concat( b, a )

7 Bits20(0xcdeab)

8

9 >>> a = Bits4( 0xd )

10 >>> b = Bits12( 0xead )

11 >>> c = Bits12( 0xbee )

12 >>> d = Bits4( 0xf )

13 >>> concat( a, b, c, d )

14 Bits32(Oxdeadbeef)

15

16 # Zero extension

17 >>> a = Bits4( 0xa )

18 >>> sext( a, 8 )

19 Bits8(Oxfa)

20 >>> zext( a, 8 )

21 Bits8(0x0a)

22

# Sign extension

23

24 >>> a = Bits4( 0x6 )

25 >>> sext( a, 8 )

Bits8(0x06)

26

27 >>> zext( a, 8 )

Bits8(0x06)

28

29

30 # Truncation

31 >>> a = Bits8( 0xff )

32 >>> trunc( a, 3 )

33 Bits3(0x7)

```

Figure 5: Bits Other Operators

#### 3.3. BitStruct Data Type

Figure 6 shows an example session in the Python interpreter that illustrates creating and using a BitStruct for storing a value with predefined named bit fields. Type these commands into the Python interpreter and observe the output.

Lines 2–6 define a new BitStruct named Point that represents a two-dimensional point with two four-bit fields; one for the X coordinate and one for the Y coordinate. The bit struct class must be decorated using @bitstruct decorator. As a quick aside, creating a bit struct using a decorator mimics the dataclass library introduced in Python 3.7. We can instantiate new Point objects, turn it into a compact string, read the named fields, and write the named fields. Lines 16-17 illustrate that the to\_bits() API can pack a bit struct instance into a Bits object. Lines 18–19 shows that it is also possible to unpack a Bits object into a bit struct instance using the class method Point.from\_nbits. Note that the order of packing/unpacking starts from the most significant bits.

Lines 21–26 define a parameterized BitStruct where the bit struct class name and a dictionary that contains name/bitwidth of the two coordinate fields are given as mk\_bitstruct call arguments. This is very useful when the bitwidths are only known at runtime.

★ To-Do On Your Own: Create a new BitStruct type for holding the an RGB color pixel. The BitStruct should include three fields named red, green, and blue. Each field should be eight bits. Experiment with reading and writing these named fields.

```

1 # Point BitStruct

>>> @bitstruct

... class Point:

x: Bits4

. . .

y: Bits4

. . .

. . .

7

>>> pt1 = Point(3, 4)

8 >>> pt1

Point(Bits4(0x3),Bits4(0x4))

10 >>> str(pt1)

'3:4'

11

12 >>> pt1.x

13

Bits4(0x3)

14 >>> pt1.y

15 Bits4(0x4)

16 >>> pt1.to_bits()

Bits8(0x34) # notice the order!

17

18

>>> Point.from_bits( Bits8(0x34) )

19

Point(Bits4(0x3),Bits4(0x4))

20

# Parameterized Point BitStruct

21

>>> nbits = 8

22

>>> PointN = mk_bitstruct( f"Point{nbits}", {

23

24 ... 'x': mk_bits(nbits),

'y': mk_bits(nbits),

25

. . .

...})

26

27

. . .

>>> pt2 = PointN( 3, 4 )

28

29 >>> pt2

30 Point8(Bits8(0x03),Bits8(0x04))

>>> pt2.to_bits()

31

32 Bits16(0x0304)

```

Figure 6: Creating and Using BitStruct Objects

## 4. Registered Incrementer

In this section, we will create our very first PyMTL3 hardware model and then learn how to simulate, visualize, verify, reuse, parameterize, and package this model. In order to learn about PyMTL3 more deeply, we will be using PyMTL3 for actual RTL modeling even though students will primarily be using Verilog for RTL modeling. Note that the same constructs we use for RTL modeling also be used in functional-level models.

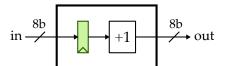

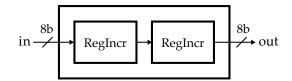

It is good design practice to usually draw some kind of picture of the hardware we wish to model before starting to develop the corresponding PyMTL3 model. This picture might be a block-level diagram, a datapath diagram, a finite-state-machine diagram, or even a control signal table; the more we can structure our code to match this diagram the more confident we can be that our model actually models what we think it does. In this section, we wish to model the eight-bit registered incrementer shown in Figure 7. In this section, you will be gradually adding code to what we provide you in the regincr subdirectory.

### 4.1. Modeling a Registered Incrementer

Figure 8 shows one way to implement the model shown in Figure 7 using PyMTL3. Every PyMTL3 file should begin with a header comment as shown on lines 1–6. The header comment identifies the primary model in the file and includes a brief description of what the model does. Reserve discussion of the actual implementation for later in the file. In general, you should attempt to keep lines in your PyMTL3 source code to less than 74 characters. This will make your code easier to read, enable printing on standard sized paper, and facilitate viewing two source files side-by-side on a single monitor.

We begin by importing the PyMTL3 framework on line 8. A PyMTL3 model is just a Python class that inherits from the Component base class provided by the PyMTL3 framework. A couple of comments about the coding conventions that we will be using in this course. PyMTL3 model names should always use CamelCaseNaming; each word begins with a capital letter without any underscores (e.g., RegIncr). Port names (as well as internal signal names and model instance names) should use underscore\_naming; all lowercase with underscores to separate words. We use in\_ to name the input port because in is a reserved keyword in Python. Carefully group ports to help the reader understand how these ports are related. Use port names (as well as variable and module instance names) that are descriptive; prefer longer descriptive names (e.g., write\_en) over shorter confusing names (e.g., wen). We usually prefer using two spaces for each level of indentation; larger indentation can quickly result in significantly wasted horizontal space. Indentation affects a Python program's semantics; so you must be consistent in how you indent blocks. This also means you cannot mix spaces and real tab characters in your source code. Our policy is to always use spaces and never insert any real tab characters in source code. Using space can also prevent a program from looking differently across different text editor settings.

The components's construct method is used to declare the port-based interface, instantiate child components, connect ports, and define concurrent blocks. This simple model does not include any child components and does not include any internal structural connectivity. Note that we diverge from standard Python coding conventions by using s instead of self to refer to the model instance in model methods. This is to reduce the non-trivial syntactic overhead of referencing ports, signals, and child components in the constructor.

Lines 18–19 declare the port-based interface for the RegIncr model, which in this case includes an eight-bit input port and eight-bit output port. Ports are just class attributes that refer to instances of the InPort or OutPort classes provided by the PyMTL3 framework. The constructor for these port

**Figure 7: Block Diagram for Registered Incrementer** – An eight-bit registered incrementer with an eight-bit input port, an eight-bit output port, and (implicit) clock and reset inputs.

```

1

2

# RegIncr

3

# This is a simple model for a registered incrementer. An eight-bit value

4

# is read from the input port, registered, incremented by one, and

5

# finally written to the output port.

6

from pymtl3 import *

8

class RegIncr( Component ):

10

11

# Constructor

12

13

def construct( s ):

14

15

# Port-based interface

16

17

s.in_ = InPort ( Bits8 )

18

s.out = OutPort ( Bits8 )

19

20

# update_ff block modeling register

21

22

s.reg_out = Wire(8) # 8 is the same as Bits8 for Wire/InPort/OutPort

23

24

@update_ff

25

def block1():

26

if s.reset:

27

28

s.reg_out <<= 0

29

else:

s.reg_out <<= s.in_</pre>

30

31

# update block modeling incrementer

32

33

Qupdate

34

def block2():

35

s.out @= s.reg_out + 1

36

```

Figure 8: Registered Incrementer – An eight-bit registered incrementer corresponding to Figure 7.

objects is parameterized by the type of values that can be sent through that port. In this example, both the input and output ports support sending eight-bit Bits objects. Note that we do not need to explicitly define a clock or reset input port; all PyMTL3 components have implicit clk and reset input ports. PyMTL3 components should never write the special clk or reset signal directly, and PyMTL3 components should never read the clk signal. PyMTL3 components can read the reset signal but only to reset state.

Line 23 declares an eight-bit internal wire within the model. Wires can be used to communicate values between concurrent blocks. Ports and wires are examples of PyMTL3 "signals", and for the most part we read and write all signals (i.e., both ports and wires) in the same way. Lines 25–30 define

a concurrent block named block1 to model the register in Figure 7. Concurrent blocks are just nested functions annotated with specific decorators. In this case, we use an update\_ff decorator, which informs the framework that the corresponding nested function should be called once on every rising clock edge (i.e., the nested function should be "ticked" once per cycle). Within the nested function we refer to the implicit reset signal to determine if we should reset the reg\_out wire to zero or copy the value on the input port to the reg\_out wire. When writing signals from within a update\_ff concurrent block, we always use the <<= operator. The <<= operator informs the framework that this non-blocking assignment should only be visible after all other update\_ff concurrent blocks have executed. Using the <<= operator is the key to making it appear as if all update\_ff concurrent blocks execute in parallel.

Lines 34–36 define a concurrent block named block2 to model the combinational logic for the incrementer in Figure 7. We use the update decorator, which informs the framework that the corresponding nested function should be called whenever any of the signals it reads change. In this case, this means block2 will be called whenever the value on the reg\_out wire changes. Note that a update concurrent block might be called multiple times within a single clock cycle until the values read by the block reach a fixed point. If the values read by an update block never reach a fixed point then we say the design has a "combinational loop." When writing signals from within an update concurrent block, we always use the @= operator. Unlike using the <<= operator, the @= operator informs the framework that this blocking assignment should be visible immediately. The write to the out port can cause other update concurrent blocks in other components that read the out port to be called.

The two concurrent blocks work together to model the registered incrementer shown in Figure 7. On every rising clock edge, the framework will call block1 which copies the value on the input port to the reg\_out wire. Since block1 is an s.tick concurrent block, it will appear to happen in parallel with all other update\_ff concurrent blocks in the system. After all update\_ff concurrent blocks have been called, the update to the reg\_out wire will be visible. If the value on the reg\_out wire has changed, then this will cause block2 to be called; block2 reads the reg\_out wire, increments the value by one, and writes the output port. Then the whole process starts again on the next rising clock edge.

A small aside about synchronous versus asynchronous resets. Although students are allowed to read the special reset signal, they can only do so within a update\_ff concurrent block (i.e., synchronous reset). Reading the reset signal in an update concurrent block is not allowed. If you need to factor the reset signal into some combinational logic, you should instead use the reset signal to reset some state bit, and the output of this state bit can be factored into some combinational logic. In other words, students should only use synchronous and not asynchronous resets.

Edit the PyMTL3 source file named RegIncr.py tut4\_pymtl/regincr subdirectory using your favorite text editor. Add the combinational concurrent block shown on lines 34–36 in Figure 8 which models the incrementer logic.

#### 4.2. Ad-Hoc Testing Using PyMTL3

Now that we have developed a new hardware model, we can test its functionality using a Python script. Figure 9 illustrates a simple Python script that elaborates the registered incrementer model, creates a simulator, writes input values to the input ports, and displays the input/output ports.

Line 12 uses a Python list comprehension to read all of the command line parameters from the argv variable, convert each parameter into an integer, and store these integers in a list named input\_values. Line 16 adds three zero values to the end of the list so that our simulation will run for a few extra cycles before stopping. Lines 20–21 construct and elaborate the new RegIncr model. Line 25 uses the

```

1

2 # regincr-adhoc-test <input-values>

#_____

3

4

5 from pymtl3 import *

6 from pymtl3.passes.backends.verilog import *

7

s from sys import argv

9 from RegIncr import RegIncr

10

11 # Get list of input values from command line

12

input_values = [ int(x,0) for x in argv[1:] ]

13

14

# Add three zero values to end of list of input values

15

16

input_values.extend( [0]*3 )

18

# Instantiate and elaborate the model

19

20

21 model = RegIncr()

22 model.elaborate()

23

24 # Apply the Verilog import passes and the default pass group

25

26 model.apply( VerilogPlaceholderPass() )

27 model = VerilogTranslationImportPass()( model )

model.apply( DefaultPassGroup() )

28

29

30 # Reset simulator

31

32 model.sim_reset()

33

34 # Apply input values and display output values

35

36 for input_value in input_values:

37

# Write input value to input port

38

39

model.in_ @= input_value

40

model.sim_eval_combinational()

41

42

# Print input and output ports

43

44

print( f" cycle = {model.sim_cycle_count()}: in = {model.in_}, out = {model.out}" )

45

46

47

# Tick simulator one cycle

48

model.sim_tick()

49

```

**Figure 9: Ad-Hoc Testing Using Python for Registered Incrementer** – Python script to elaborate the model, apply PyMTL3 passes, write input values to the input ports, and display the input/output ports.

DefaultPassGroup to add simulation facilities to the top-level component. A key feature of PyMTL3 is its IMIR software architecture that separates the domain-specific language implementation (e.g., the implementation to support and collect update\_ff and <<=), in-memory intermediate representation, and passes, meaning that designers create models and then apply various passes (such as the DefaultPassGroup,) to analyze, instrument, and transform the elaborated designs. We reset the simulator on line 29 which will raise the implicit reset signal for two cycles. Lines 33–47 define a loop that is used to iterate through the list of input values. For each input value, we write the value to the model's input port, display the values on the input/output ports, and tick the simulator. Note that we must use @= attribute when writing ports in the simulator script, similar to how signals are written from within update concurrent blocks. Otherwise, the simulator will throw an exception.

Edit the simulator script named regincr-sim. Add the code on lines 18–25 in Figure 9 to construct the model, elaborate the model, and build a simulator using the default pass group. Then run the simulator script as follows:

```

% cd ${TUTROOT}/build

% python ../tut4_pymtl/regincr/regincr-adhoc-test.py 0x01 0x13 0x25 0x37

```

You should see output from executing the simulator over several cycles. Note that the output starts on cycle 3; this is because calling the simulator's reset method raises the implicit reset signal for the first two cycles. On every cycle, we see a new input value being written into the registered incrementer, and on the *next* cycle we should see the corresponding incremented value being read from the output port.

★ *To-Do On Your Own:* Try running the simulator script with a different list of input values specified on the command line. Verify that the registered incrementer performs as expected when given the input value 0xff.

Instead of reading the input values from the command line on line 12, experiment with generating a sequence of numbers automatically from within the script. You can use Python's range function to generate a sequence of numbers (potentially with a step greater than one), and you can use the shuffle function from the standard Python random module to randomly shuffle a sequence of numbers.

#### 4.3. Visualizing a Model with Line Traces

While it is possible to visualize the execution of a model by manually inserting print statements both in the simulator script and in concurrent blocks, this can be quite tedious. Because this kind of visualization is so common, PyMTL3 includes built-in support for *line tracing*. A line trace consists of plain-text trace output with each line corresponding to one (and only one!) cycle. Fixed-width columns will correspond to either state at the beginning of the corresponding cycle or the output of combinational logic during that cycle. Line traces will abstract the detailed bit representations of signals in our design into useful character representations. So for example, instead of visualizing messages as raw bits, we will visualize them as text strings. Line traces can give designers a high-level view of how data is moving throughout the system.

To use line tracing, we need define a line\_trace method in our models. Add the following method to the RegIncr component:

```

def line_trace( s ):

return f"{s.in_} ({s.reg_out}) {s.out}"

```

Each component's line\_trace method should: read the ports, wires, and other internal variables; create a fixed-width string representation of the current state and operation; and then return this string. You can use Python's extensive string manipulation capabilities to create compact and useful line traces. To display the line trace, remove the print statement on lines 38–39 in the regincr-adhoc-test script shown in Figure 9, and add linetrace=True as a keyword argument as follows to DefaultPassGroup to enable the simulator to automatically call the line\_trace method.

```

model.apply( DefaultPassGroup(linetrace=True) )

```

Make these modifications and rerun the simulator. You can see the value at the input port, the current state of the register in the model, and the value at the output port.

★ *To-Do On Your Own:* Modify the line tracing code to show the port labels. After your modifications, the line trace might look something like this:

2: in:01 (00) out:01 3: in:13 (01) out:02 4: in:25 (13) out:14

#### 4.4. Visualizing a Model with Text-Based Waveform

Line tracing can be useful for initially debugging the high-level behavior of your design, but it can also be useful to visualize various signals as waveforms. If you want to take a quick look at the value changes of all the signals in a small design over just a few cycles, you can display a text-based waveform *inside the terminal*.

We need to modify regincr-adhoc-test to enable this functionality. Pass a textwave=True parameter to default pass group, and add model.print\_textwave() after the loop of regincr-adhoc-test script shown in Figure 9. This is because PyMTL3 doesn't want to dump the text-based waveform when your simulation is still going, so you need to call the print\_textwave method by yourself.

```

model.apply( DefaultPassGroup(textwave=True) )

```

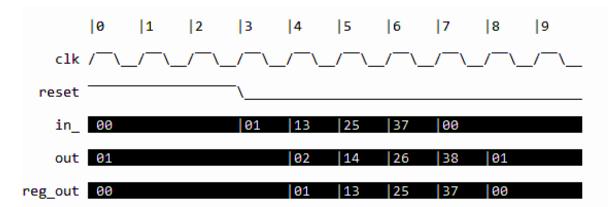

Make these modifications and rerun the ad-hoc test. Figure 10 shows screenshot of the terminal displaying the text-based waveform.

#### 4.5. Visualizing a Model with VCD Waveforms

Line tracing can be useful for initially debugging the high-level behavior of your design, but often we need to visualize many more signals than can be easily captured in a line trace. The PyMTL3 framework can output waveforms in the Value Change Dump (VCD) format for every signal (i.e., ports and wires) in your design.

To generate VCD in regincr-adhoc-test, you need to pass a vcdwave keyword argument to the default pass group. The parameter should be a string containing the desired file name for the generated VCD (no need to add .vcd extension though). The default pass group will properly enable VCD dumping. Replace line 25 in the regincr-adhoc-test script shown in Figure 9 with the following line of code.

```

model.apply( DefaultPassGroup(vcdwave='regincr-adhoc-test) )

```

Make these modifications and rerun the ad-hoc test.

**Figure 10: PyMTL3 Text-Based Waveforms** – Text-based waveforms are being used to display signals directly in the terminal associated with the registered incrementer shown in Figure 8.

```

% cd ${TUTROOT}/build

```

% python ../tut4\_pymtl/regincr/regincr-adhoc-test.py 0x01 0x13 0x25 0x37

There are two options for viewing VCD files: (1) the Surfer extension for VS Code; or (2) the standalone GTKWave program.

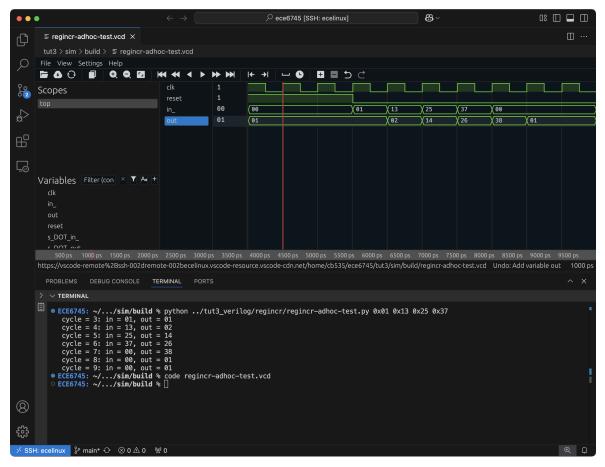

Surfer only works if you are using VS Code. You just need to use the standard code command to open the VCD file and VS Code will automatically take care of launching Surfer.

% cd \${TUTROOT}/build

% code regincr-adhoc-test.vcd &

You can browse the module hierarchy of your design in the upper-left "Scopes" panel, with the signals in any given module being displayed in the lower-left "Variables" panel. Clicking on a signal will cause it to be added to the waveform panel on the right. You can drag-and-drop signals to arrange them as desired. You can use the scrollbar at the bottom to scroll to the right through the waveform, and you can use the *View* > *Zoom In* and *View* > *Zoom Out* menu options or the corresponding magnifying glass icons in the toolbar to zoom in or out. To see the full hierarchical names of each signal choose *Settings* > *Variable names* > *Global*. Choose *File* > *Reload* (or click the circular arrows icon in the toolbar) to update Surfer after you have rerun a simulation. Organizing signals can sometimes be quite time consuming, so you can save and load the current configuration using *File* > *Save state as* and *File* > *Load state*. Figure 11 illustrates using Surfer to view the waveforms from our ad-hoc test. Surfer has many useful options which can make debugging your design more productive, so feel free to explore the associated documentation.

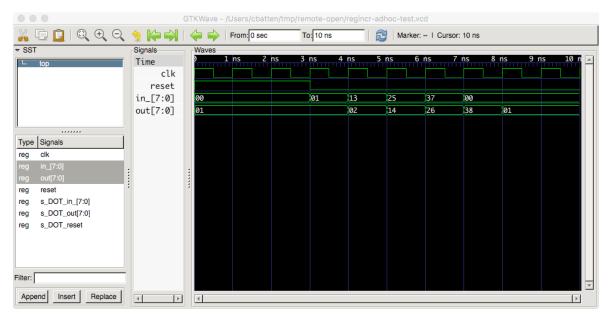

The stand-alone GTKWave program is a Linux GUI application which means you will need to be logged into ecelinux using Microsoft Remote Desktop. You can then use GTKWave to browse the generated waveforms by entering the following commands in the terminal within Microsoft Remote Desktop:

% cd \${TUTROOT}/build

% gtkwave regincr-adhoc-test.vcd &

You can browse the module hierarchy of your design in the upper-left panel, with the signals in any given module being displayed in the lower-left panel. Select signals and use the *Append* or *Insert*

**Figure 11: Surfer Waveform Viewer** – Surfer extension for VS Code is being used to browse the signals associated with the registered incrementer shown in Figure 8 and the ad-hoc test shown in Figure 13.

button to add them to the waveform panel on the right. You can drag-and-drop signals to arrange them as desired. You can use the scrollbar at the bottom to scroll to the right through the waveform, and you can use the *Time* > *Zoom* menu or the corresponding magnifying glass icons in the toolbar to zoom in or out. To see the full hierarchical names of each signal choose *Edit* > *Toggle Trace Hierarchy* or simply press the H key. Choose *File* > *Reload Waveform* (or click the blue circular arrow icon in the toolbar) to update GTKWave after you have rerun a simulation. Organizing signals can sometimes be quite time consuming, so you can save and load the current configuration using *File* > *Write Save File* and *File* > *Read Save File*. Figure 12 illustrates using GTKWave to view the waveforms from our ad-hoc test. GTKWave has many useful options which can make debugging your design more productive, so feel free to explore the associated documentation.

★ To-Do On Your Own: Edit the register incrementer so that it now increments by +2 instead of +1.

Rerun the simulator script and take another look the waveforms to see how they have changed.

When you are finished, edit the registered incrementer so that it again increments by +1.

**Figure 12: GTKWave Waveform Viewer** – GTKWave is being used to browse the signals associated with the registered incrementer shown in Figure 8 and the ad-hoc test shown in Figure 13.

#### 4.6. Verifying a Model with Unit Testing

Now that we have developed a new hardware model, our first thought should always turn to testing that model. Students might be tempted to simply look at line traces and/or waveforms from a simulator script to determine if their design is working, but this kind of "verification by inspection" is error prone and not reproducible. If you later make a change to your design, you would have to take another look at the line traces and/or waveforms to ensure that your design still works. If another member of your group wants to understand your design and verify that it is working, he or she would also need to take a look at the line traces and/or waveforms. While this might be feasible for very simple designs, it is obviously not a scalable approach when building the more complicated designs we will tackle in this course. Automated testing through unit testing is the best way to rigorously verify your designs.

We could simply write ad-hoc Python scripts to unit test our designs. These scripts would instantiate our design, write values to the input ports, and then verify the outputs. Unfortunately, there are many issues with using ad-hoc unit testing. Ad-hoc unit testing is usually verbose, which makes it error prone and more cumbersome to write tests. Ad-hoc unit testing is difficult for others to read and understand since by definition it is ad-hoc. Ad-hoc unit testing does not use any kind of standard test output, and does not provide support for controlling the amount of test output. In this course, we will be using the powerful pytest unit testing framework. The pytest framework is popular in the Python programming community with many features that make it well-suited for test-driven hardware development including: no-boilerplate testing with the standard assert statement; automatic test discovery; helpful traceback and failing assertion reporting; standard output capture; sophisticated parameterized testing; test marking for skipping certain tests; distributed testing; and many third-party plugins. More information is available at http://www.pytest.org.

Figure 13 illustrates a simple unit testing script for our registered incrementer. Notice at a high-level the test code is very straight-forward; the pytest framework enables unit testing to be as simple or as complex as necessary. The pytest framework includes automatic test discovery, which means that

2 # RegIncr\_simple\_test 3 #-----5 from pymtl3 import \* 6 7 from pymtl3.stdlib.test\_utils import config\_model\_with\_cmdline\_opts 9 from ..RegIncr import RegIncr 10 11 # In pytest, unit tests are simply functions that begin with a "test\_" 12 # prefix. PyMTL3 is setup to collect command line options. Simply specify 13 # "cmdline\_opts" as an argument to your unit test source code, 14 # and then you can dump VCD by adding --dump-vcd option to pytest 15 # invocation from the command line. 16 17 def test\_basic( cmdline\_opts ): 18 # Create the model 19 20 model = RegIncr() 21 22 # Configure the model 23 24 model = config\_model\_with\_cmdline\_opts( model, cmdline\_opts, duts=[] ) 25 26 # Create and reset simulator 27 28 model.apply( DefaultPassGroup(linetrace=True) ) 29 30 model.sim\_reset() 31 # Helper function 32 33 def t( in\_, out ): 34 35 # Write input value to input port 36 37 38 model.in\_ @= in\_ 39 # Ensure that all combinational concurrent blocks are called 40 41 sim.sim\_eval\_combinational() 42 43 44 # If reference output is not '?', verify value read from output port 45 if out != '?': 46 assert model.out == out 47 48 # Tick simulator one cycle 49 50 sim.sim\_cycle() 51 52 53 # Cycle-by-cycle tests 54 t( 0x00, '?' ) 55 t( 0x13, 0x01 ) 56 t( 0x27, 0x14 ) 57 t( 0x00, 0x28 ) 58 t( 0x00, 0x01 ) 59 t( 0x00, 0x01 ) 60

**Figure 13: Unit Test Script for Registered Incrementer** – A unit test for the eight-bit registered incrementer in Figure 8, which uses the pytest unit testing framework.

it will look through the unit test script and assume that any function that begins with test\_ is a test case. In this example, pytest will discover a single test case named test\_basic corresponding to the function declared on lines 16–59. To test our registered incrementer, we need to instantiate and elaborate the model, use the default pass group to add simulation facilities, write values to the input ports of the model, and finally verify that the values read from the output ports of the model are correct.

Lines 20–24 instantiate and configures the model using the command line options. Note that the dump\_vcd flag passed from the command lines is collected in the cmdline\_opts dictionary to the unit test. If a user includes --dump-vcd on the command-line when running pytest, then the framework will generate a VCD file for every unit test. The name of the VCD file is derived from the name of the unit test. If a user does not include --dump-vcd on the command-line when running pytest, then dump\_vcd will be None and no VCD file will be generated. Lines 28–29 use the SimulationTool to create and reset a simulator.

Lines 33–50 define a simple helper function that is responsible for verifying one cycle of execution. The helper function takes the desired test input and the reference test output as arguments. Line 37 writes the test input to the in\_ port of the registered incrementer. Note that it is important to use @= operator when writing ports in the test harness, similar to how signals are written from within update concurrent blocks. Line 41 tells the simulator to call any update concurrent blocks whose input values have changed. Lines 45–46 read the out port and compare it to the reference output to ensure that the registered incrementer is functioning correctly. Notice that we check to make sure the reference output is not set to a question mark character. This gives us a simple way to indicate that we do not care what the output value is on that cycle. Also notice that the pytest framework does not need special assertion checking functions, and instead hooks into the standard assert statement provided in Python. This means the pytest framework can carefully track the assert statement on line 46, and on an assertion error will display the context of the assert statement including the sequence of function calls that lead to the assertion and the values of the variables used in the assert statement.

Lines 54–59 use our helper function to test the registered incrementer over six cycles. These test cases are an example of *directed cycle-by-cycle gray-box testing*. It is directed since we are explicitly creating directed tests as opposed to using some kind of random testing. It is cycle-by-cycle since we are explicitly setting the inputs and verifying the outputs every cycle. *Black-box testing* describes a testing strategy where the test cases depend only on the interface and not the specific implementation of the DUT (i.e., they should be valid for any correct implementation). *White-box testing* describes a testing strategy where the test cases depend on the specific implementation of the DUT (i.e., they may not be valid for every correct implementation). The test cases in Figure 13 are *black-box* with respect to the functional behavior of the DUT, but they are *white-box* with respect to the timing behavior of the device. The test cases rely on the fact that the registered incrementer includes exactly one edge and they would fail if we pipelined the incrementer such that each transaction took two edges. In Section 6, we will see how we can use latency-insensitive interfaces to create true black-box unit tests.

Edit the test script named RegIncr\_test.py. Note that it is important that all test script file names end in \_test.py, since this suffix is used by the pytest framework for automatic test discovery. Add the tests cases shown on lines 54–59 in Figure 8. We can run the test script using pytest as follows:

```

% cd ${TUTROOT}/build

```

% pytest ../tut4\_pymtl/regincr/test/RegIncr\_test.py

Note that we run our unit test scripts from within a separate build directory. The PyMTL3 framework often creates extra temporary and/or output files, so keeping these generated files in a separate build

**Figure 14:** pytest **Output** – Each line corresponds to one test script, and each dot corresponds to one passing test case. Failing test cases are shown with an F character.

directory helps avoid creating generated files in the source tree and facilitates performing a clean build. The pytest framework automatically discovers the test\_basic test case. The output from running pytest should look similar to what is shown in Figure 14; pytest will display the name of the test script and a single dot indicating that the corresponding test case has passed. If we ran multiple test scripts, then each test script would have a separate line in the output. If we had multiple test\_functions in RegIncr\_test.py, then each test case would have its own dot. Failing test cases are shown with an F character.

Note that our test script prints the line trace, yet the line trace is not included in the output shown in Figure 14. This is because by default, the pytest framework "captures" the standard output from a test script instead of displaying this output. The output is only displayed when a test case fails, or if the users explicitly disables capturing the standard output. So to generate a line trace for this test, we simply use the --capture=no (or -s) command line option as follows:

```

% cd ${TUTROOT}/build

% pytest ../tut4_pymtl/regincr/test/RegIncr_test.py -s

```

Note that by default, pytest will not show much detail on an error. This enables a designer to quickly get an overview of which tests are passing and which tests are failing. If some of your tests are failing, then you will want to produce more detailed error output using the --tb command line options.

```

% cd ${TUTROOT}/build

% pytest ../tut4_pymtl/regincr/test/RegIncr_test.py --tb=short

% pytest ../tut4_pymtl/regincr/test/RegIncr_test.py --tb=long

```

The --tb command line option specifies the level of "trace-back" output, and there are a couple of different options you might want to use including: long, short, and line. To generate waveforms for this test, we simply use the --dump-vcd command line option as follows:

```

% cd ${TUTROOT}/build

% pytest ../tut4_pymtl/regincr/test/RegIncr_test.py --dump-vcd

% gtkwave tut4_pymtl.regincr.test.RegIncr_test_test_basic.vcd &

```

★ To-Do On Your Own: Edit the register incrementer so that it now increments by +2 instead of +1. Rerun the unit test and verify that the tests no longer pass. Use the --tb=long command line option to display more detailed error output. Study the output carefully to understand the corresponding error messages. You should see: (1) a sequence of two function calls that lead to the assertion failure; (2) the exact assertion that is failing; (3) the value of the output port and the reference output in the failing assertion; and (4) the captured standard output which usually a line trace. Modify the unit test so that it includes the correct reference outputs for a +2 incrementer, rerun the unit test, and verify that the test now passes. When you are finished, edit the registered incrementer so that it again increments by +1.

#### 4.7. Verifying a Model with Test Vectors

The unit test shown in Figure 13 requires quite a bit of setup code. Usually we want to include many directed test cases in a test script; each test case focuses on testing a different specific aspect of our design. If we simply extend the approach shown in Figure 13, then each test case would need to duplicate lines 16–50. We could refactor this code into a separate helper function that can be reused across all test cases in a given test script. However, since this kind of testing is so common, PyMTL3 includes a flexible helper function for unit testing any model using test vectors. This function is named run\_test\_vector\_sim and it is part of pymtl3.stdlib (PyMTL3 Standard Library), which has a variety of RTL and testing functions, classes, and models that we will be using in this class. To find out more about stdlib, you can browse the source code on the public PyMTL3 GitHub repository:

- https://github.com/pymtl/pymtl3/tree/pymtl4.0-dev/pymtl3/stdlib/primitive

- https://github.com/pymtl/pymtl3/tree/pymtl4.0-dev/pymtl3/stdlib/test\_utils

For example, here is the definition of the run\_test\_vector\_sim helper function:

• https://github.com/pymt1/pymt13/blob/pymt14.0-dev/pymt13/stdlib/test\_utils/test\_helpers.py#L275

Test vectors are essentially a table of test inputs and reference outputs. Figure 15 shows an extra test script that uses the run\_test\_vector\_sim helper function provided by the PyMTL3 framework. There are three test cases for testing small input values, large input values, and the registered incrementer's overflow condition. The run\_test\_vector\_sim helper function takes two arguments: an instantiated model and a test vector table. The function elaborates a model, uses the simulation tool to create a simulator, resets the simulator, writes the input values provided in the test vector table to the model's input ports, reads the values from the model's output ports, and compares the values to the reference values provided by the test vector table. The test vector table is a list of lists and is written so as to look like a table. Each column corresponds to either an input value or a reference output value, and each row corresponds to one cycle of the simulation. Question marks are allowed for reference output values when we don't care what the output is on that cycle. The first row of the test vector table is always a special "header string" that specifies the name of the model's input/output port for that column. Output ports are denoted with an asterisk suffix. Note how compact this test script is compared to the test script in Figure 13. This sophisticated helper function demonstrates the power of using a general-purpose dynamic language such as Python to write test harnesses.

Edit the new test script named RegIncr\_extra\_test.py. Add the code on lines 35–46 in Figure 15 which tests for overflow. Run this extra test script using pytest as follows:

% cd \${TUTROOT}/build

```

1 #------

2 # RegIncr_test

3 #-----

5 from pymtl3 import *

6 from pymtl3.stdlib.test_utils import run_test_vector_sim

7 from ..RegIncr import RegIncr

9 #-----

10 # test_small

11 #-----

12

13 def test_small( cmdline_opts ):

run_test_vector_sim( RegIncr(), [

14

('in_ out*'),

15

[ 0x00, '?' ],

16

[ 0x03, 0x01 ],

17

[ 0x06, 0x04 ],

18

[0x00, 0x07],

19

], cmdline_opts )

20

21

22 #-----

_____

23 # test large

24 #-----

25

26 def test_large( cmdline_opts ):

run_test_vector_sim( RegIncr(), [

27

('in_ out*'),

28

[ 0xa0, '?' ],

29

[ 0xb3, 0xa1 ],

30

[ 0xc6, 0xb4 ],

31

[ 0x00, 0xc7 ],

32

], cmdline_opts )

33

34

35 #-----

36 # test_overflow

37 #-----

38

39 def test_overflow( cmdline_opts ):

run_test_vector_sim( RegIncr(), [

40

41

('in_ out*'),

[ 0x00, '?' ],

42

[ 0xfe, 0x01 ],

43

[ Oxff, Oxff ],

44

[ 0x00, 0x00 ],

45

], cmdline_opts )

46

```

**Figure 15: Unit Test Script using Test Vectors for Registered Incrementer** – A unit test for the eight-bit registered incrementer in Figure 8, which uses test vectors and the pytest unit testing framework.

% pytest ../tut4\_pymtl/regincr/test/RegIncr\_extra\_test.py

The output should show the name of the test script and three dots corresponding to the three test cases in Figure 15. The pytest framework can automatically discover test scripts in addition to automatically discovering the test cases within a test script. If the argument to pytest is a directory, then pytest will search that directory for any files ending in \_test.py and assume that these files are

collected 21 items

```

../tut4_pymt1/regincr/test/RegIncr2stage_test.py::test_small FAILED

../tut4_pymt1/regincr/test/RegIncr2stage_test.py::test_large FAILED

../tut4_pymtl/regincr/test/RegIncr2stage_test.py::test_overflow FAILED

../tut4_pymtl/regincr/test/RegIncr2stage_test.py::test_random FAILED

../tut4_pymtl/regincr/test/RegIncrNstage_test.py::test[2stage_small] FAILED

../tut4_pymtl/regincr/test/RegIncrNstage_test.py::test[2stage_large] FAILED

../tut4_pymtl/regincr/test/RegIncrNstage_test.py::test[2stage_overflow] FAILED

../tut4_pymtl/regincr/test/RegIncrNstage_test.py::test[2stage_random] FAILED

../tut4_pymtl/regincr/test/RegIncrNstage_test.py::test[3stage_small] FAILED

../tut4_pymtl/regincr/test/RegIncrNstage_test.py::test[3stage_large] FAILED

../tut4_pymtl/regincr/test/RegIncrNstage_test.py::test[3stage_overflow] FAILED

../tut4_pymtl/regincr/test/RegIncrNstage_test.py::test[3stage_random] FAILED

../tut4_pymtl/regincr/test/RegIncrNstage_test.py::test_random[1] PASSED

../tut4_pymtl/regincr/test/RegIncrNstage_test.py::test_random[2] FAILED

../tut4_pymtl/regincr/test/RegIncrNstage_test.py::test_random[3] FAILED

../tut4_pymtl/regincr/test/RegIncrNstage_test.py::test_random[4] FAILED

../tut4_pymtl/regincr/test/RegIncrNstage_test.py::test_random[5] FAILED

../tut4_pymtl/regincr/test/RegIncrNstage_test.py::test_random[6] FAILED

../tut4_pymtl/regincr/test/RegIncr_simple_test.py::test_basic PASSED

../tut4_pymtl/regincr/test/RegIncr_test.py::test_small PASSED

../tut4_pymtl/regincr/test/RegIncr_test.py::test_large PASSED

```

**Figure 16:** pytest **Verbose Output** – Each line corresponds to one test case. Passing test cases are marked with **PASSED** and failing test cases are marked with **FAILED**.

test scripts. The pytest framework also provides a more verbose output where each test case is listed on a separate line; passing test cases are marked with PASSED and failing test cases are marked with FAILED. Run both of the test scripts using the --verbose (or -v) command line option as follows:

```

% cd ${TUTROOT}/build

% pytest ../tut4_pymtl/regincr/test -v

```

The verbose output should look similar to what is shown in Figure 16. Some test cases are passing for those models which we have completed, while other test cases are failing because we will work on them later in the tutorial. We can use the -k command line option to select just a few test cases to run and debug in more detail. For example to run just the test case for testing small input values, we can use the following:

```

% cd ${TUTROOT}/build

% pytest ../tut4_pymtl/regincr/test -k small

```

We can use the -x command line option to have pytest stop after the very first failing test case:

```

% cd ${TUTROOT}/build

% pytest ../tut4_pymtl/regincr -x

```

When testing an entire directory, we often use an iterative process to "zoom" in on a failing test case. We start by running all tests in the directory to see an overview of which tests are passing and which tests are failing. We then explicitly run a single test script with the -v command line option to see which specific test cases are failing. Finally, we use the -k or -x command line options with --tb, -s, and/or --dump-vcd command line option to generate error output, line traces, and/or waveforms

```

1 #-----

2 # test_random

3 #-----

5 import random

7 def test_random( cmdline_opts ):

test_vector_table = [( 'in_', 'out*' )]

9

last_result = '?'

10

for i in range(20):

11

rand_value = Bits8( random.randint(0,0xff) )

12

13

test_vector_table.append( [ rand_value, last_result ] )

14

last_result = Bits8( rand_value + 1, trunc_int=True )

15

run_test_vector_sim( RegIncr(), test_vector_table, cmdline_opts )

16

```

**Figure 17: Random Test Case for Registered Incrementer** – Random input values and the corresponding incremented output value are added to a test vector table for random testing.

for the failing test case. Here is an example of this three-step process to "zoom" in on a failing test case:

```

% cd ${TUTROOT}/build

% pytest ../tut4_pymtl/regincr/test/

% pytest ../tut4_pymtl/regincr/test/RegIncr2stage_test.py -v

% pytest ../tut4_pymtl/regincr/test/RegIncr2stage_test.py -v -x --tb=short

% pytest ../tut4_pymtl/regincr/test/RegIncr2stage_test.py -v -x --tb=long

```

$\star$

*To-Do On Your Own:* Add another directed test case for the registered incrementer which tests another arbitrary set of input values. Rerun the test script, and verify that the output matches your expectations.

#### 4.8. Verifying a Model with Random Testing

So far we used a directed cycle-by-cycle gray-box testing strategy. Once we have finished writing hand-crafted directed tests, we almost always want to leverage randomized testing to further improve our confidence in the correct functionality of the design. Generating random test vectors in Python is relatively straight forward, especially if we make use of the standard Python random module. Figure 17 illustrates a random test case for the registered incrementer. Note that the random test vector generation must carefully take into account the latency of the registered incrementer in order to ensure that each reference output is placed in the correct row of the test vector table. Add this test case to the RegIncr\_extra\_test.py test script, and run the new test case with line tracing enabled as follows:

```

% cd ${TUTROOT}/build

% pytest ../tut4_pymtl/regincr/test/RegIncr_extra_test.py -k random -s

```

★ *To-Do On Your Own:* Add another random test case for the registered incrementer where the input values are always less than 16 (i.e., small numbers). Rerun the test script, and verify that the output matches your expectations.

#### 4.9. Reusing a Model with Structural Composition

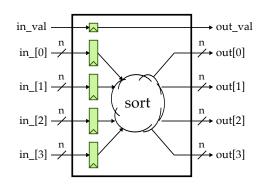

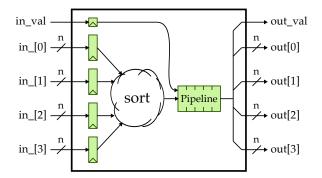

We will use modularity and hierarchy to structurally compose small, simple models into large, complex models. This incremental approach allows us to first design and test the small models, and thus ensure they are working, before integrating them and testing the larger models. Figure 18 shows a two-stage registered incrementer that uses structural composition to instantiate and connect two instances of a single-stage registered incrementer. Figure 19 shows the corresponding PyMTL3 model. Line 9 imports the child model that we will be reusing.

Lines 19–20 illustrate a simplified PyMTL3 syntax for specifying the type of the values that can be passed through the in\_ and out ports. If we use an integer N, then this is syntactic sugar for specifying that objects of type BitsN can be passed through the port.

Lines 24–33 actually perform the structural composition of the two instances of the child model. Line 24 instantiates the first RegIncr model with the instance name reg\_incr\_0. Line 26 uses the connect function to connect two ports together: the in\_ port, which is part of the parent interface, and the in\_ port for the first RegIncr. The arguments to the connect method can be ports or wires and can be in either order (i.e., the input signal is not required to be the first argument). Line 30 instantiates the second RegIncr model with the instance name reg\_incr\_1. Line 32 connects the output of the first RegIncr to the input of the second RegIncr. Line 33 connects the output of the second RegIncr to the out port in the parent interface using //= operator which is a syntactic sugar for connect. Ever since //= operator was introduced, almost all PyMTL3 design code has been using //= for connections.

Lines 37–43 show the line\_trace method for the two-stage registered incrementer. A key feature of line tracing is the ability to construct line trace strings hierarchically. On lines 40–41, we call the line\_trace methods for the two child RegIncr models.

As always, once we create a new hardware model, we should immediately write a unit test to verify its functionality. Figure 20 shows a test script using test vectors to verify our two-stage registered incrementer. Notice how we must carefully take into account the two-cycle latency of the registered incrementer in order to ensure that each reference output is placed in the correct row of the test vector table. This is because we are using a cycle-by-cycle gray-box testing strategy.

Edit the PyMTL3 source file named RegIncr2stage.py. Add lines 28-33 from Figure 19 to connect the second stage of the two-stage registered incrementer. Then run all of the test scripts as well as a subset of the test cases as follows:

% cd \${TUTROOT}/build

% pytest ../tut4\_pymtl/regincr/test/RegIncr2stage\_test.py -v

Figure 18: Block Diagram for Two-Stage Registered Incrementer – An eight-bit two-stage registered incrementer that reuses the registered incrementer in Figure 7 through structural composition.

```

2 # RegIncr2stage

4 # Two-stage registered incrementer that uses structural composition to

5 # instantiate and connect two instances of the single-stage registered

6 # incrementer.

8

from pymtl3 import *

from tut4_pymtl.regincr.RegIncr import RegIncr

10

11

class RegIncr2stage( Component ):

12

13

14

# Constructor

15

def construct( s ):

16

17

# Port-based interface

18

19

s.in_ = InPort (8)

20

s.out = OutPort(8)

21

22

# First stage

23

24

s.reg_incr_0 = RegIncr()

25

26

27

connect( s.in_, s.reg_incr_0.in_ )

28

# Second stage

29

30

s.reg_incr_1 = RegIncr()

31

32

s.reg_incr_0.out //= s.reg_incr_1.in_

33

s.reg_incr_1.out //= s.out

34

35

# Line Tracing

36

37

def line_trace( s ):

38

return "{} ({}|{}) {}".format(

39

s.in_,

40

41

s.reg_incr_0.line_trace(),

s.reg_incr_1.line_trace(),

42

43

s.out

)

44

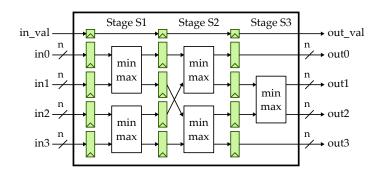

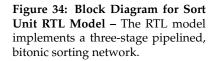

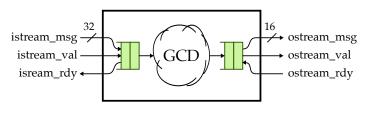

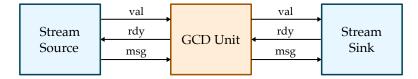

```