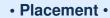

# ECE 6745 Complex Digital ASIC Design Topic 13: Physical Design Automation Algorithms

**Christopher Batten**

School of Electrical and Computer Engineering Cornell University

http://www.csl.cornell.edu/courses/ece6745

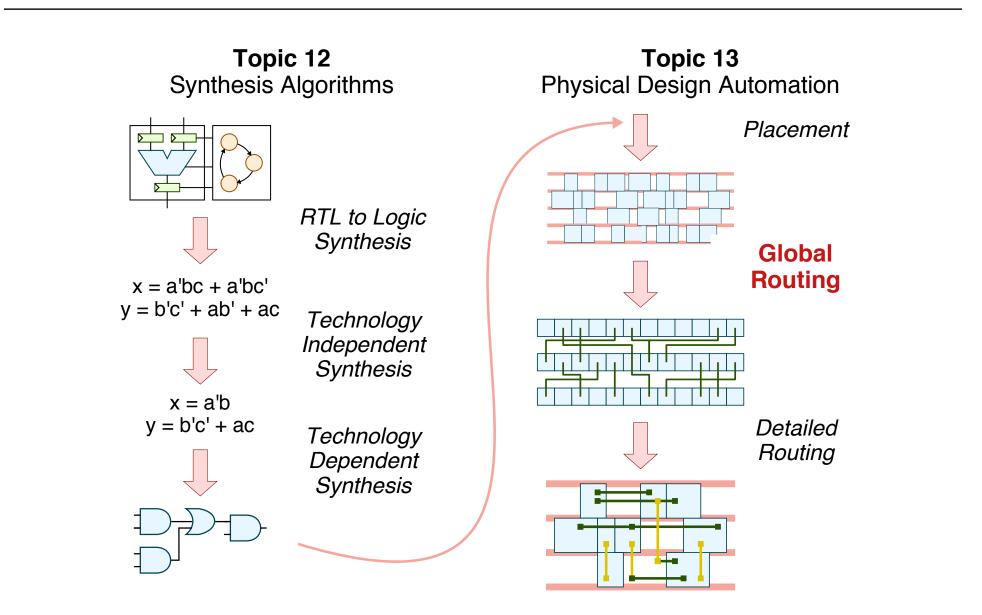

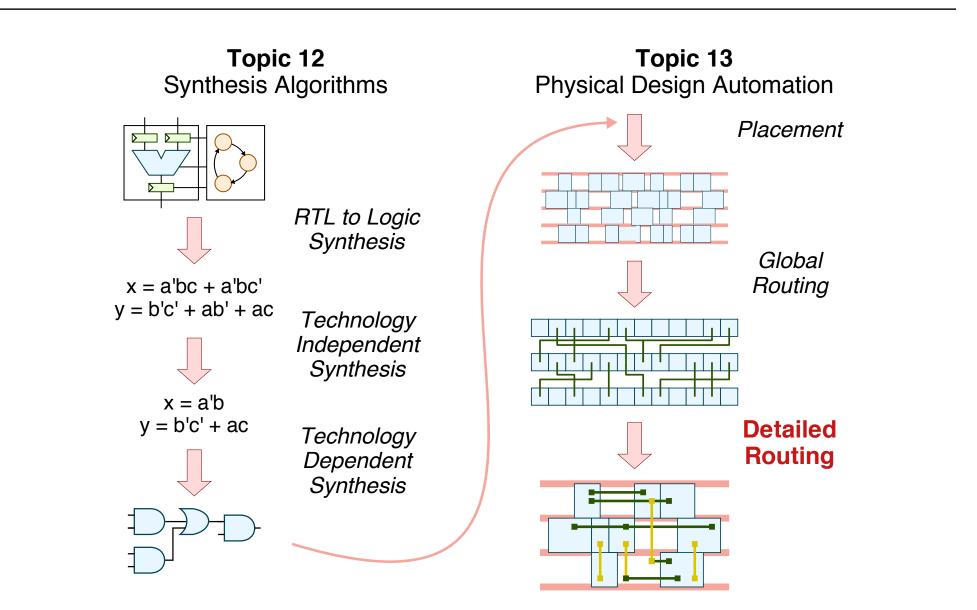

## Part 3: CAD Algorithms

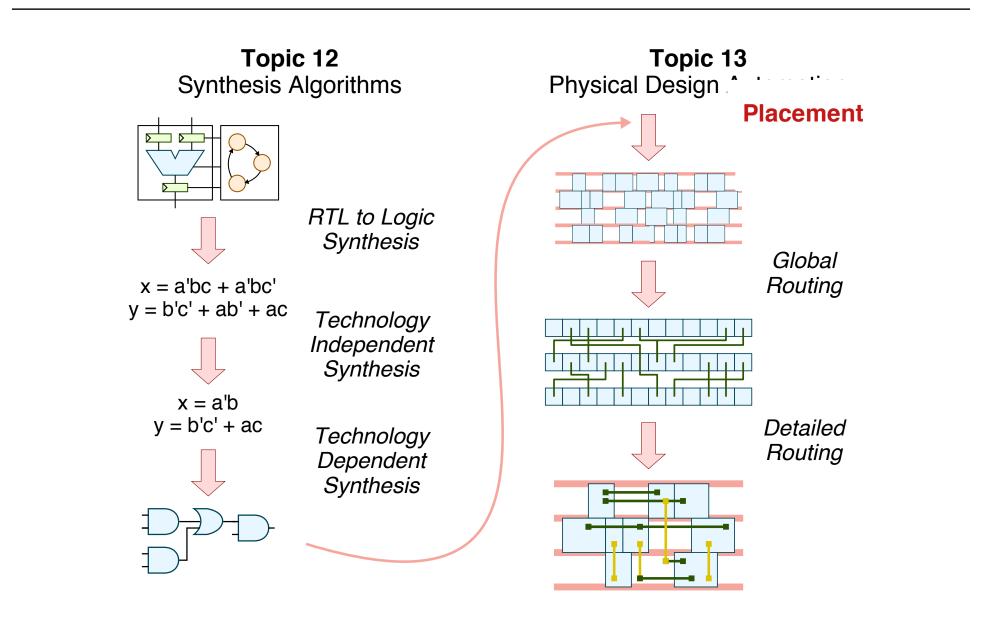

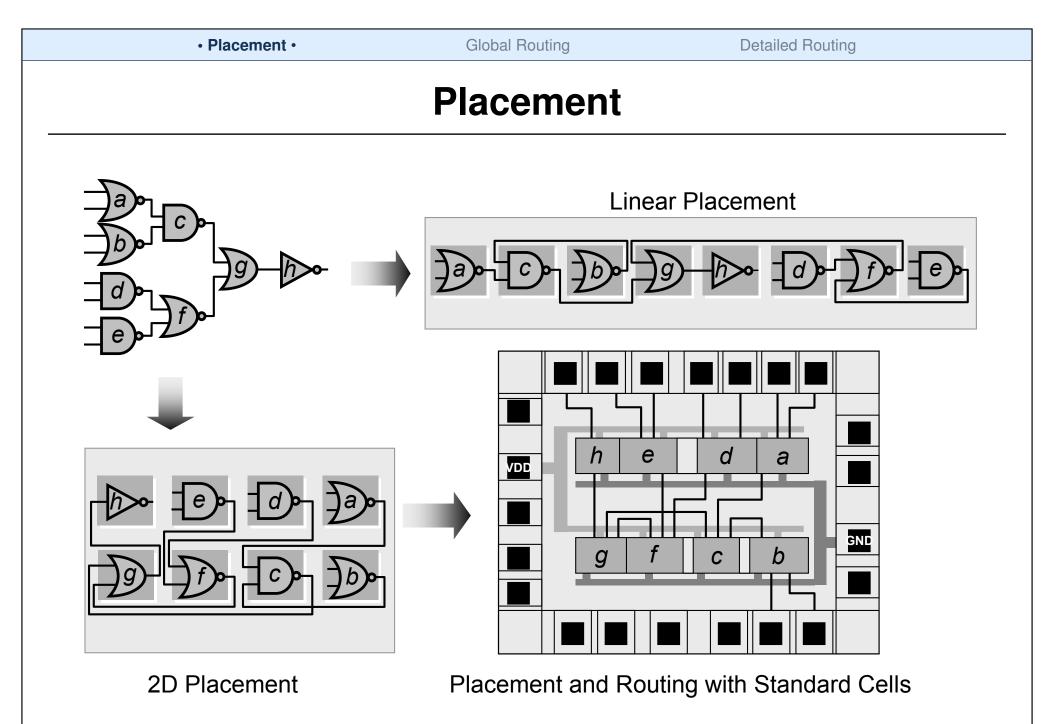

Placement

·

**Global Routing**

**Detailed Routing**

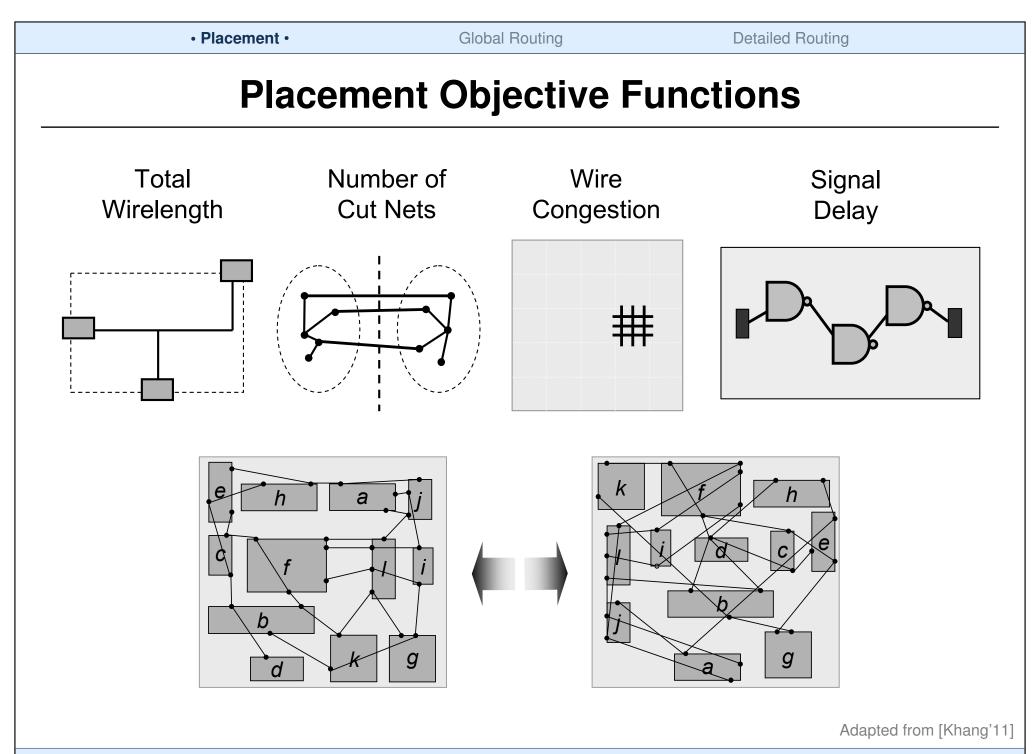

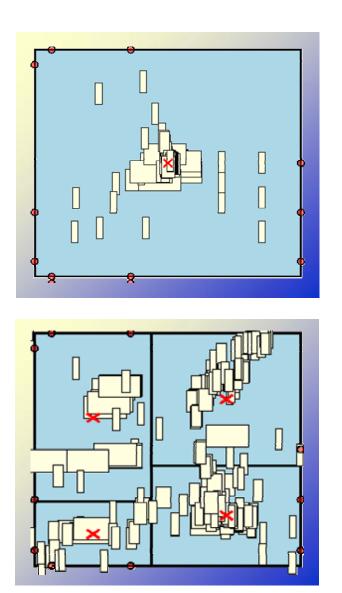

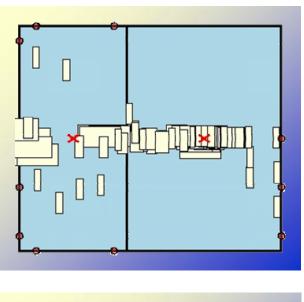

### Good vs. Bad Placement

Bad placement causes routing congestion resulting in:

- Increases in circuit area (cost) and wiring

- Longer wires → more capacitance

- Longer delay

- Higher dynamic power dissipation

#### **Good placement**

- •Circuit area (cost) and wiring decreases

- Shorter wires → less capacitance

- Shorter delay

- Less dynamic power dissipation

Adapted from [Devadas'06]

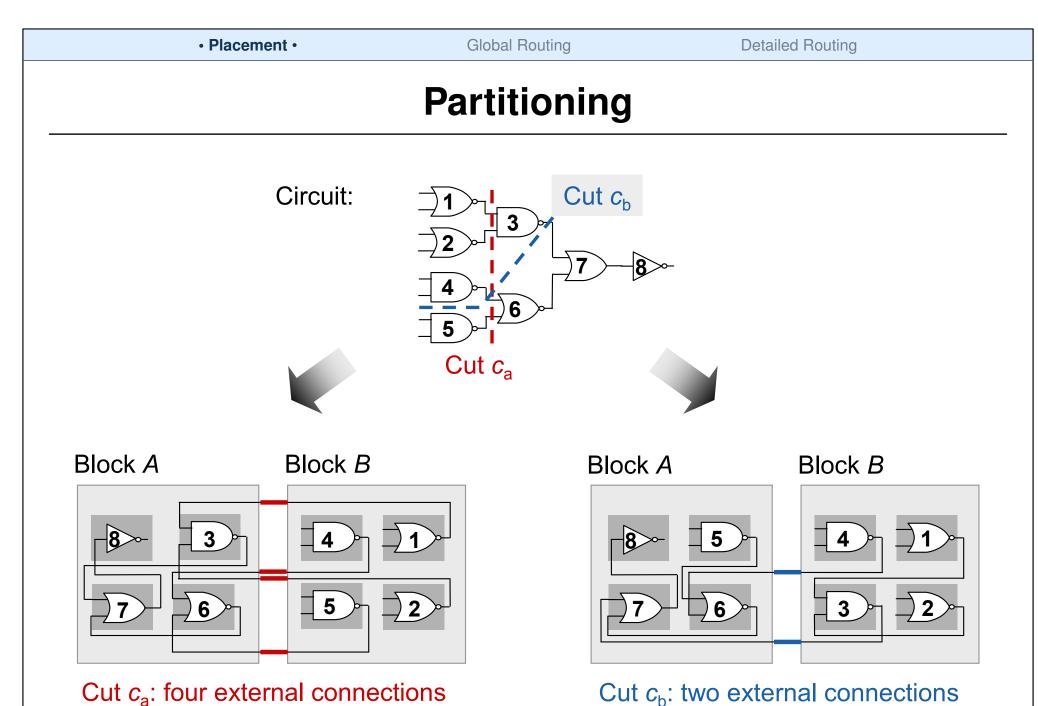

Cut  $c_{\rm b}$ : two external connections

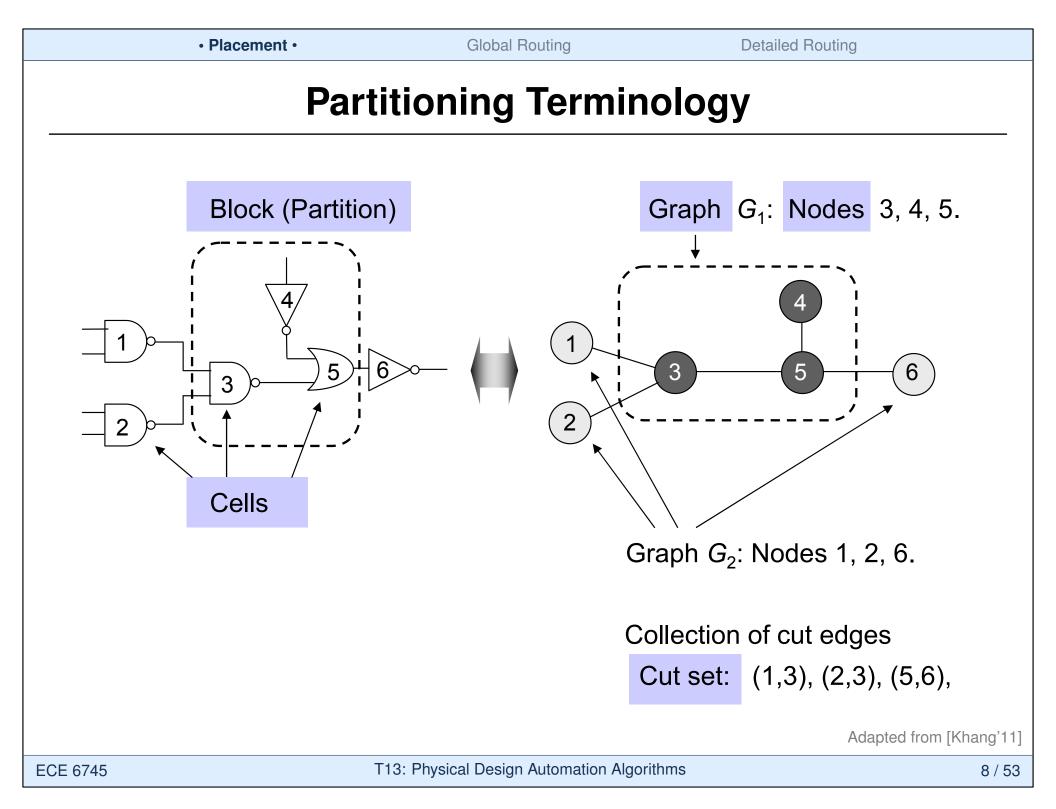

# Kernighan-Lin (KL) Algorithm

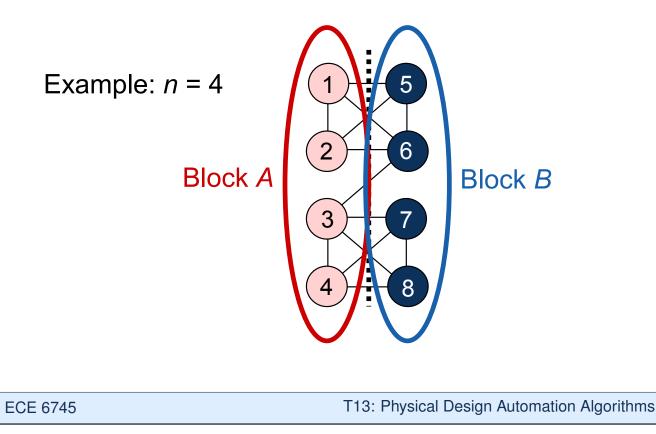

Given: A graph with 2n nodes where each node has the same weight.

Goal: A partition (division) of the graph into two disjoint subsets A and B with minimum cut cost and |A| = |B| = n.

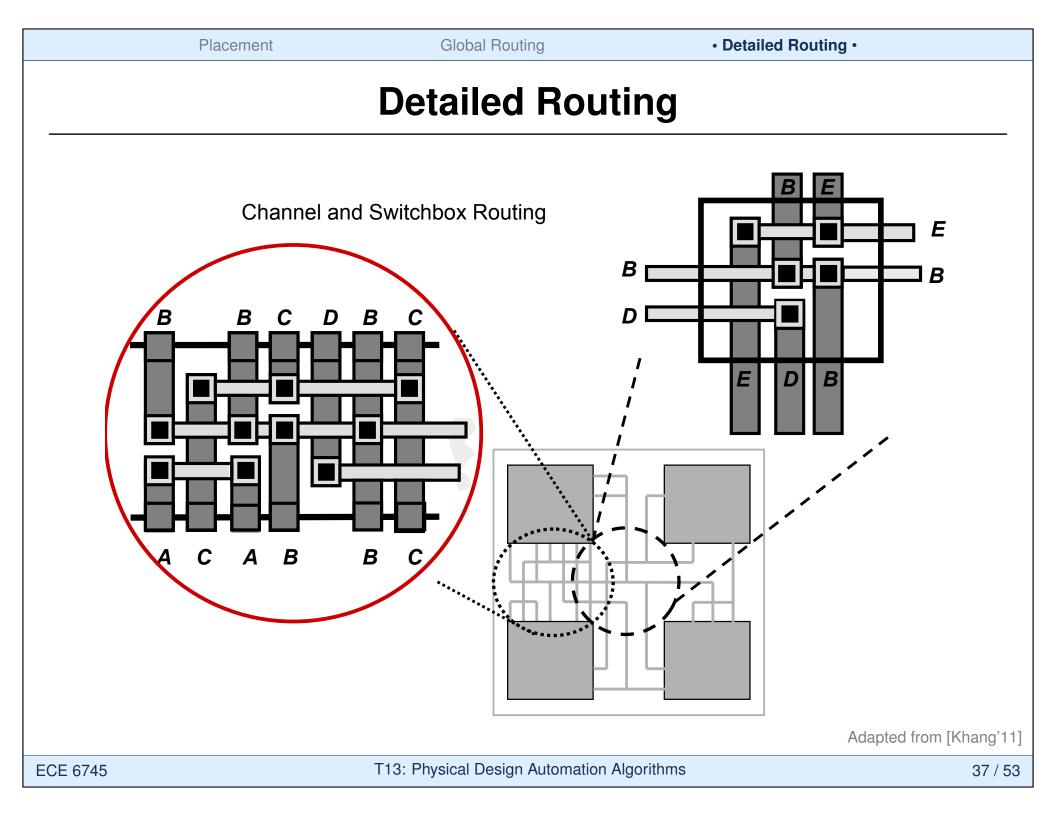

**Detailed Routing**

# Kernighan-Lin (KL) Algorithm Concepts

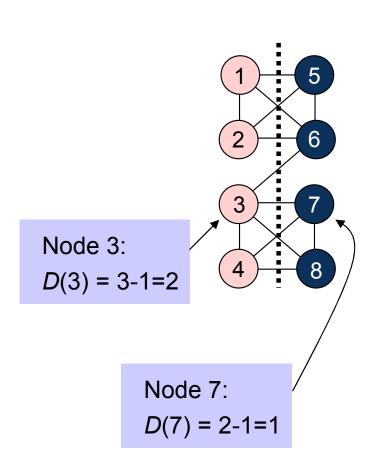

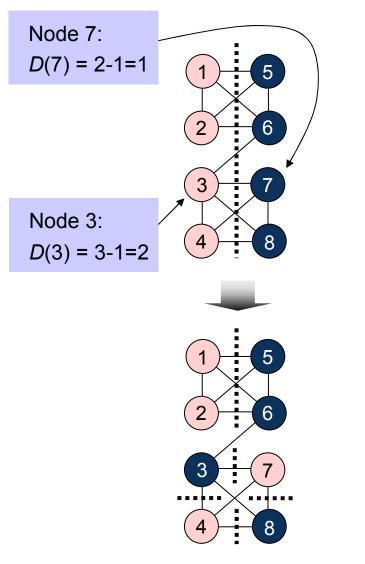

Cost D(v) of moving a node v

$$D(v) = |E_{\rm c}(v)| - |E_{\rm nc}(v)|$$

,

#### where

$E_{\rm c}(v)$  is the set of *v*'s incident edges that are cut by the cut line, and

$E_{\rm nc}(v)$  is the set of *v*'s incident edges that are not cut by the cut line.

High costs (D > 0) indicate that the node should move, while low costs (D < 0) indicate that the node should stay within the same partition.

**Detailed Routing**

# Kernighan-Lin (KL) Algorithm Concepts

Gain of swapping a pair of nodes a und b

$\Delta g = D(a) + D(b) - 2 \cdot c(a,b),$

#### where

• D(a), D(b) are the respective costs of nodes a, b

c(a,b) is the connection weight between a and b:

If an edge exists between a and b,

then c(a,b) = edge weight (here 1),

otherwise, c(a,b) = 0.

The gain  $\Delta g$  indicates how useful the swap between two nodes will be

The larger  $\Delta g$ , the more the total cut cost will be reduced

11 / 53

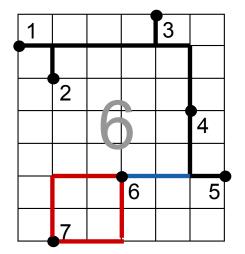

## Kernighan-Lin (KL) Algorithm Concepts

Gain of swapping a pair of nodes a und b

$\Delta g = D(a) + D(b) - 2 \cdot c(a,b),$

#### where

- D(a), D(b) are the respective costs of nodes a, b

- c(a,b) is the connection weight between a and b:

If an edge exists between a and b,

then c(a,b) = edge weight (here 1),

otherwise, c(a,b) = 0.

$\Delta g (3,7) = D(3) + D(7) - 2 \cdot c(a,b) = 2 + 1 - 2 = 1$

=> Swapping nodes 3 and 7 would reduce the cut size by 1

Adapted from [Khang'11]

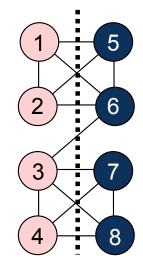

## Kernighan-Lin (KL) Algorithm Concepts

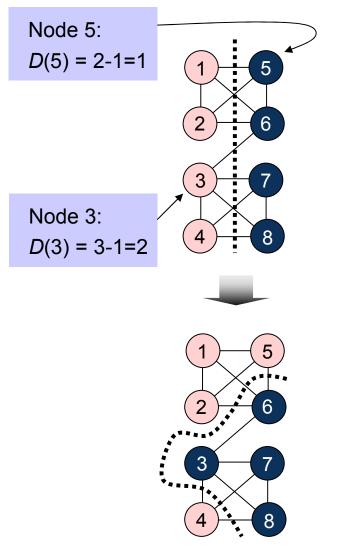

Gain of swapping a pair of nodes *a* und *b*

$\Delta g = D(a) + D(b) - 2 \cdot c(a,b),$

#### where

- D(a), D(b) are the respective costs of nodes a, b

- c(a,b) is the connection weight between a and b: If an edge exists between a and b, then c(a,b) = edge weight (here 1), otherwise, c(a,b) = 0.

$$\Delta g (3,5) = D(3) + D(5) - 2 \cdot c(a,b) = 2 + 1 - 0 = 3$$

=> Swapping nodes 3 and 5 would reduce the cut size by 3

Adapted from [Khang'11]

**Detailed Routing**

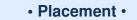

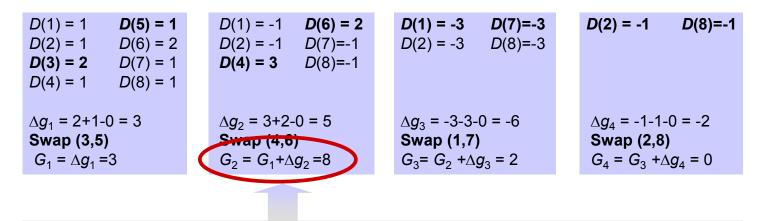

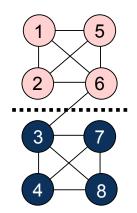

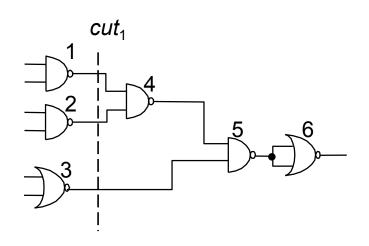

## Kernighan-Lin (KL) Algorithm Example

Placement

**Global Routing**

**Detailed Routing**

## Kernighan-Lin (KL) Algorithm Example

Maximum positive gain  $G_m = 8$  with m = 2.

Since  $G_m > 0$ , the first m = 2 swaps (3,5) and (4,6) are executed.

Since  $G_m > 0$ , more passes are needed until  $G_m \leq 0$ .

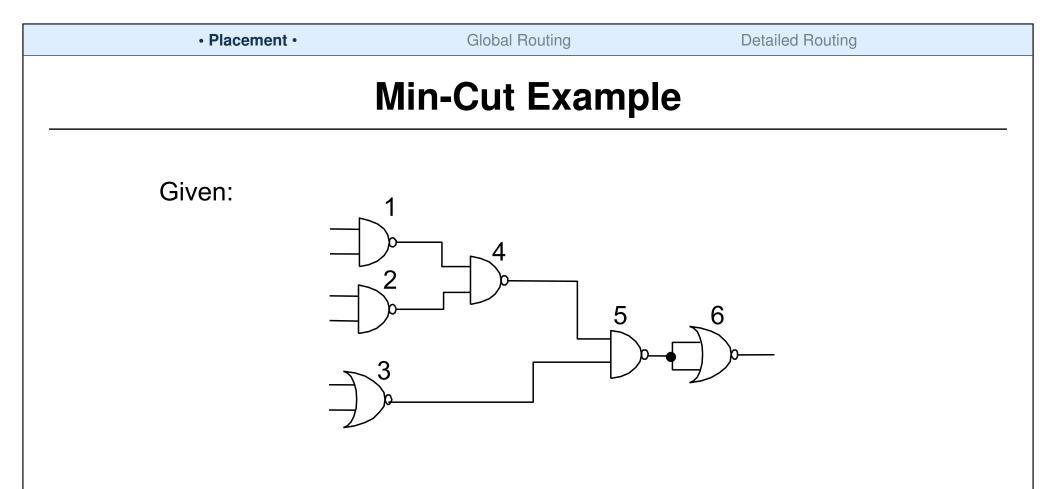

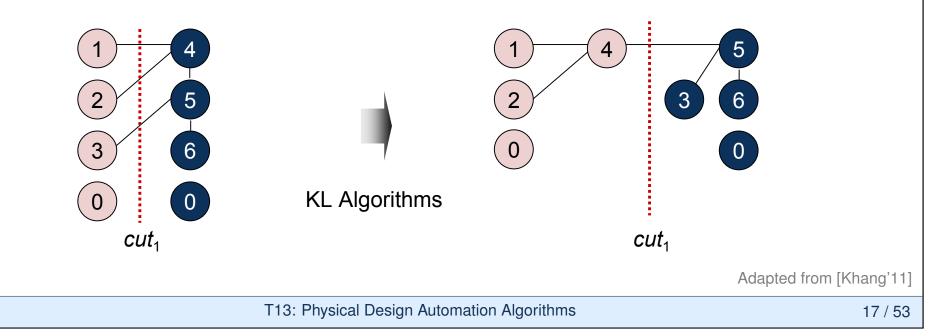

## **Min-Cut Placement**

- Use partitioning algorithm (such as KL) to divide netlist into two regions

- Use partitioning algorithm to recursively divide the two partitions into two smaller regions (four regions total)

- Each cut heuristically minimizes the number of cut nets

Task: 4 x 2 placement with minimum wirelength using alternative cutline directions and the KL algorithm

Placement

ECE 6745

**Global Routing**

**Detailed Routing**

## **Min-Cut Example**

Vertical cut *cut*<sub>1</sub>: *L*={1,2,3}, *R*={4,5,6}

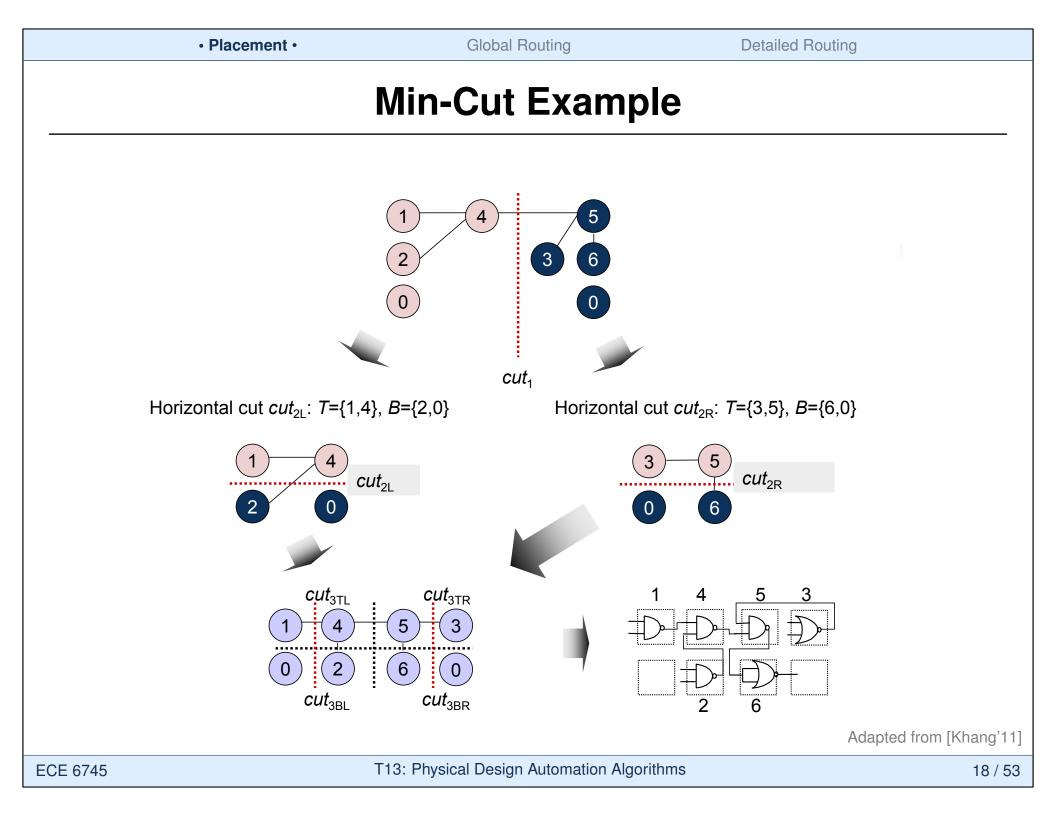

## Analytical Placement with Quadratic Placement Algorithm

Objective function is quadratic; sum of (weighted) squared Euclidean distance represents placement objective function

$$L(P) = \frac{1}{2} \sum_{i,j=1}^{n} c_{ij} \left( \left( x_i - x_j \right)^2 + \left( y_i - y_j \right)^2 \right)$$

where *n* is the total number of cells, and c(i,j) is the connection cost between cells *i* and *j*.

- Only two-point-connections

- Minimize objective function by equating its derivative to zero which reduces to solving a system of linear equations

Placement

**Global Routing**

**Detailed Routing**

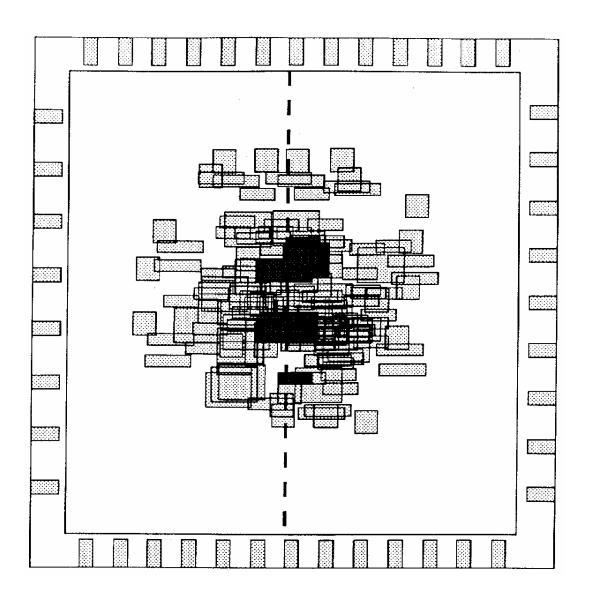

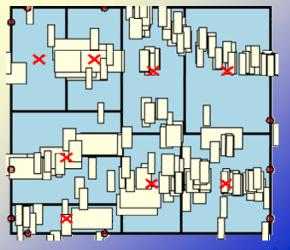

### **Minimizing Objective Function Clumps Cells Together**

Adapted from [Devadas'06]

Placement

**Global Routing**

**Detailed Routing**

## Using Partitioning to Pull Cells Apart

Adapted from [Devadas'06,Kahng'11]

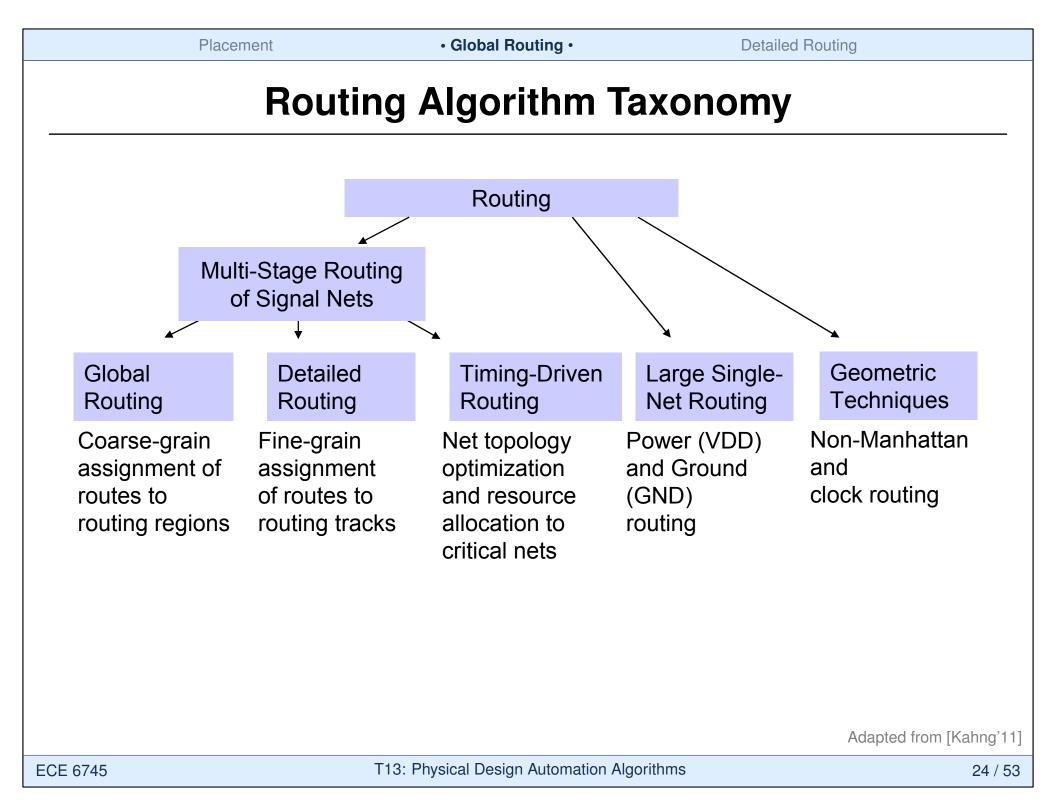

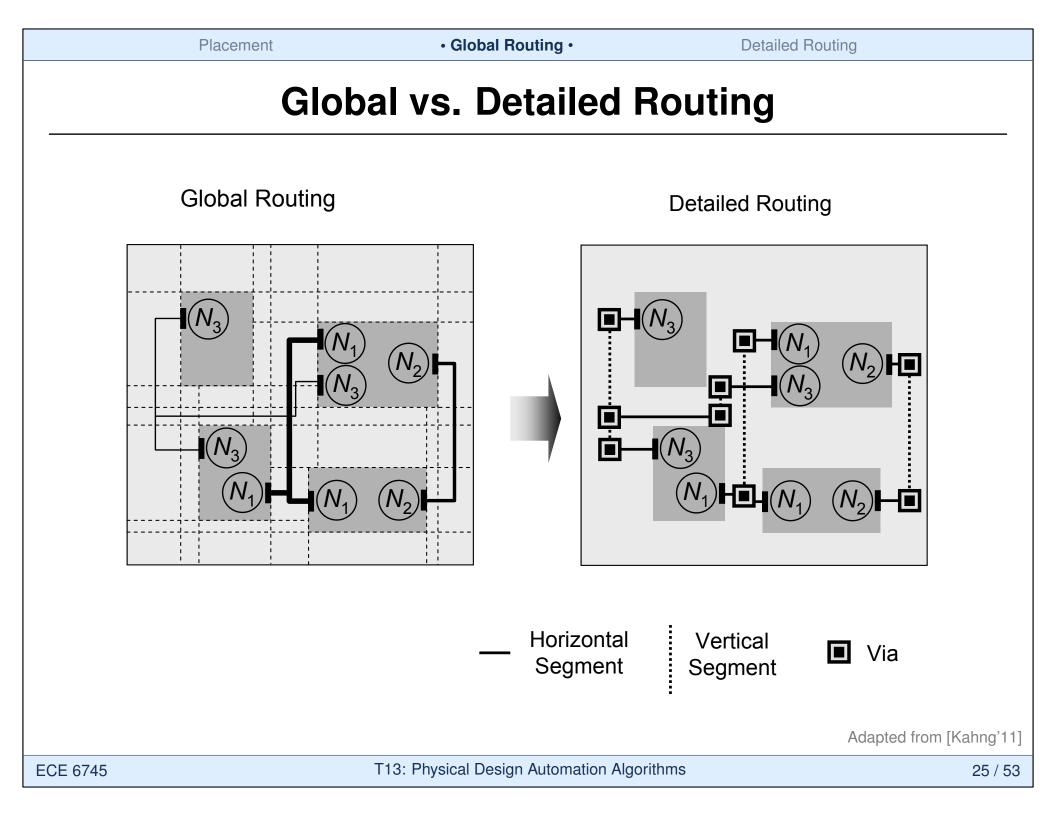

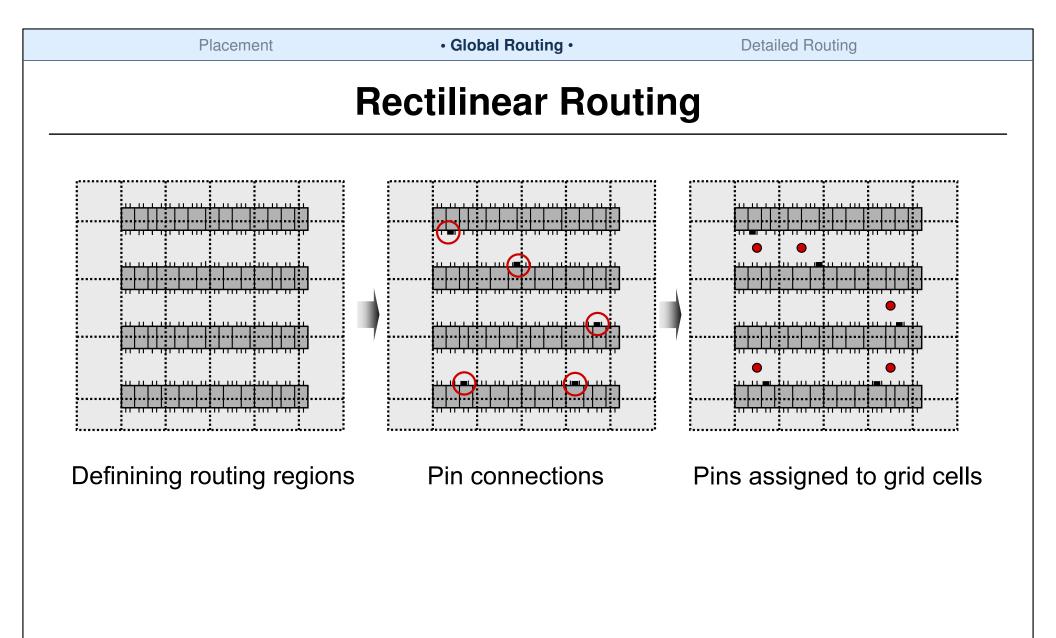

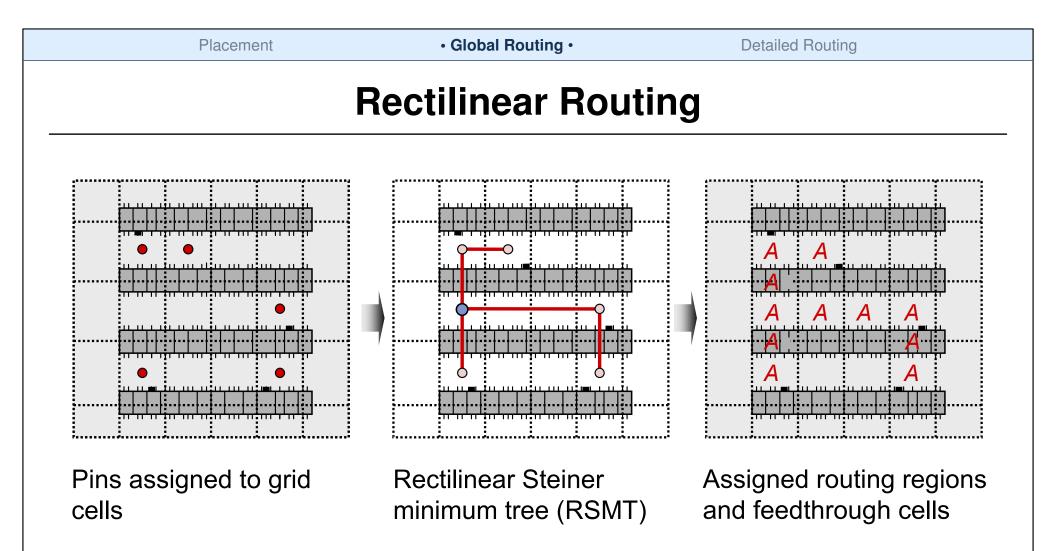

## Part 3: CAD Algorithms

**Detailed Routing**

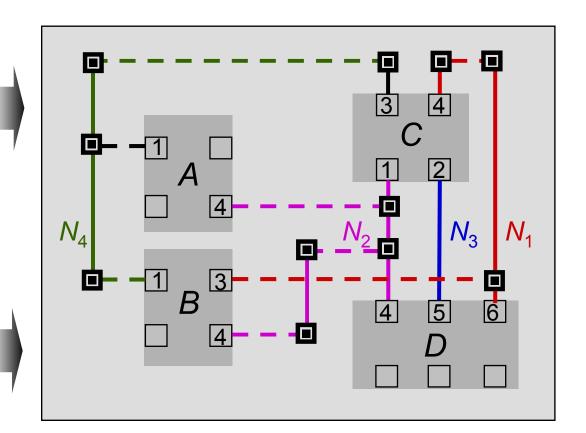

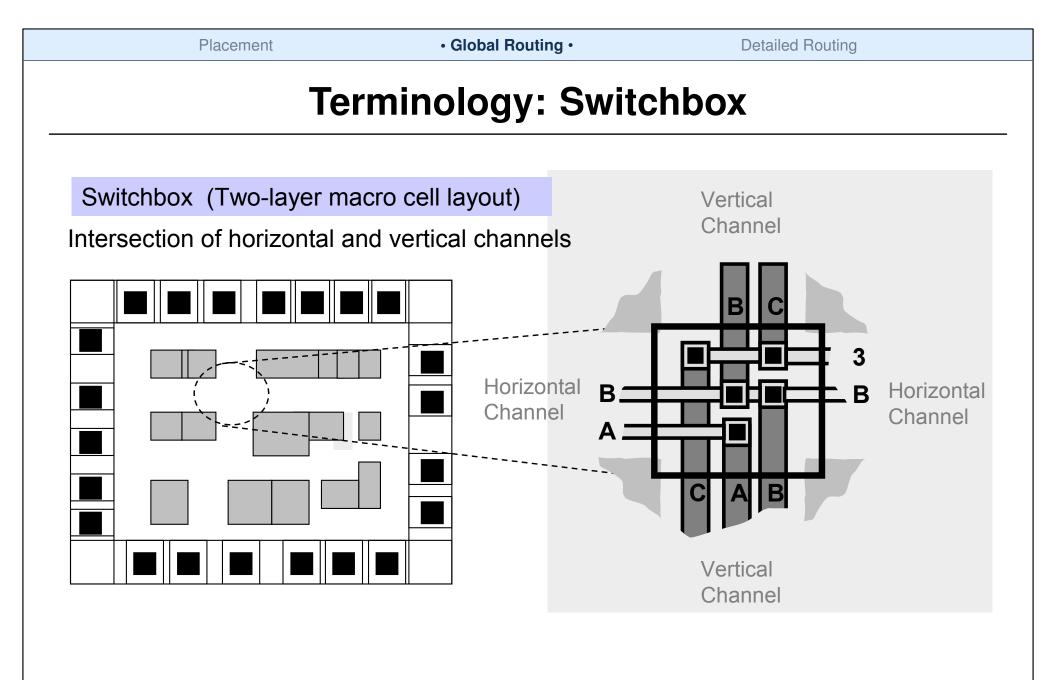

### **General Routing Problem**

#### Netlist:

$N_{1} = \{C_{4}, D_{6}, B_{3}\}$  $N_{2} = \{D_{4}, B_{4}, C_{1}, A_{4}\}$  $N_{3} = \{C_{2}, D_{5}\}$  $N_{4} = \{B_{1}, A_{1}, C_{3}\}$

Technology Information (Design Rules)

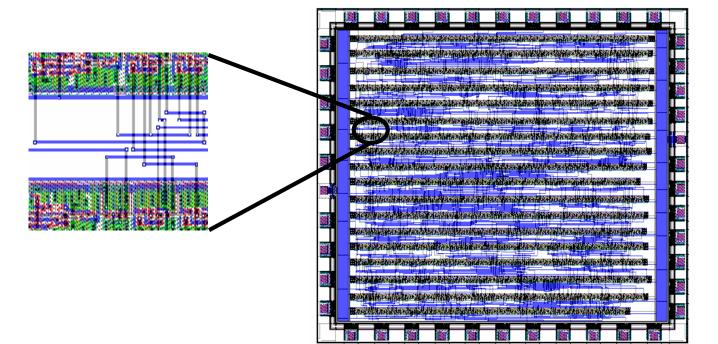

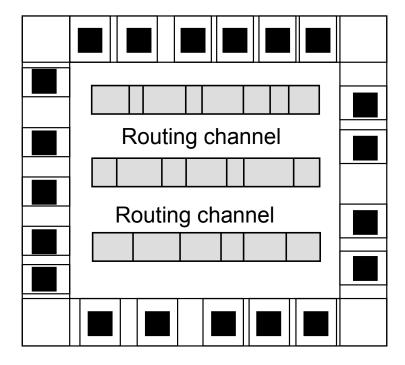

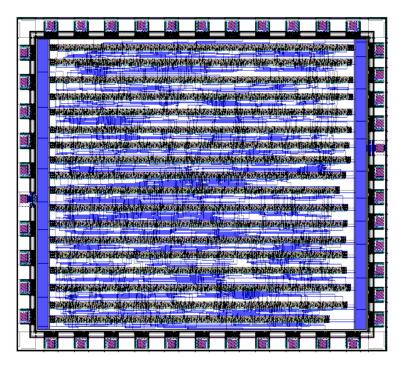

## **Terminology: Channel**

#### Channel

Rectangular routing region with pins on two opposite sides

Standard cell layout (Two-layer routing)

**Detailed Routing**

## **Terminology: Channel**

### Channel

Rectangular routing region with pins on two opposite sides

Standard cell layout (Two-layer routing)

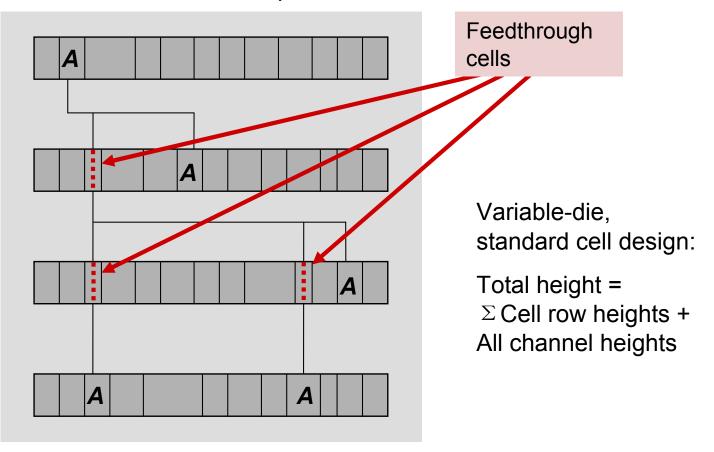

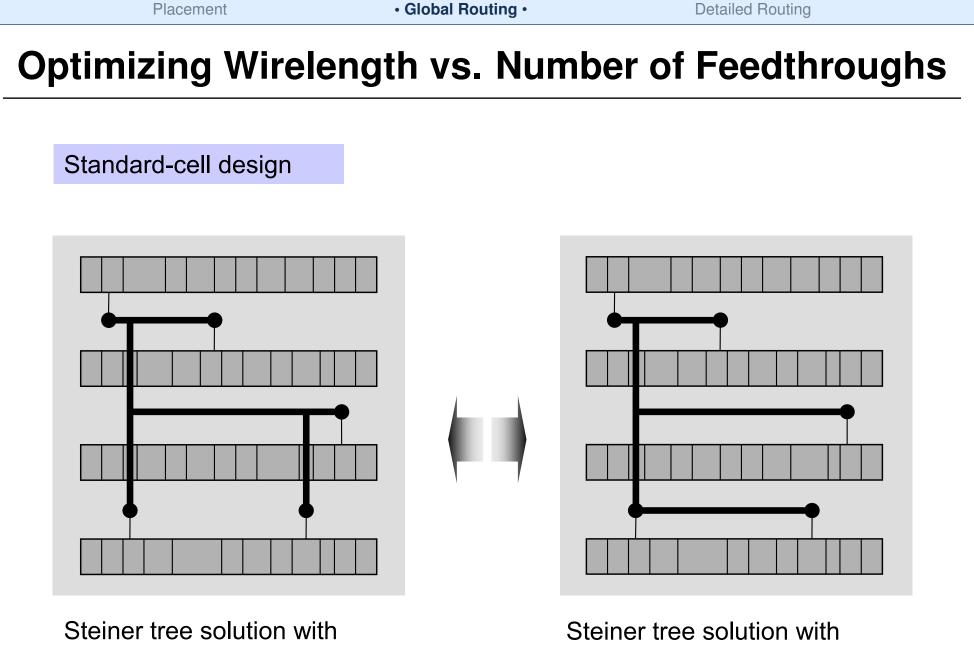

## Terminology: Feed-Through Cells

#### Standard-cell design

If number of metal layers is limited, feedthrough cells must be used to route across multiple cell rows

minimal wirelength

Steiner tree solution with fewest feedthrough cells

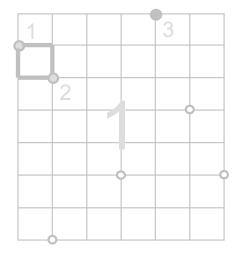

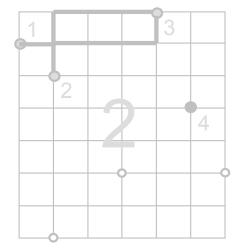

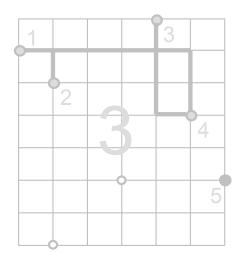

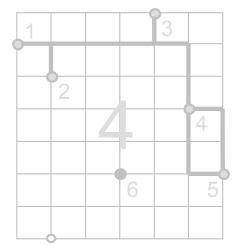

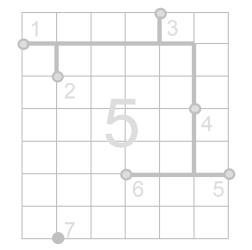

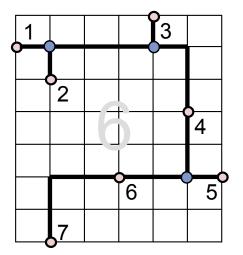

## **Heuristic Sequential Steiner Tree Algorithm**

- 1. Find the closest (in terms of rectilinear distance) pin pair, construct their minimum bounding box (MBB)

- 2. Find the closest point pair ( $p_{MBB}$ , $p_C$ ) between any point  $p_{MBB}$  on the MBB and  $p_C$  from the set of pins to consider

- **3**. Construct the MBB of  $p_{MBB}$  and  $p_C$

- 4. Add the *L*-shape that  $p_{MBB}$  lies on to *T* (deleting the other *L*-shape). If  $p_{MBB}$  is a pin, then add any *L*-shape of the MBB to *T*.

- 5. Goto step 2 until the set of pins to consider is empty

Placement

Global Routing

**Detailed Routing**

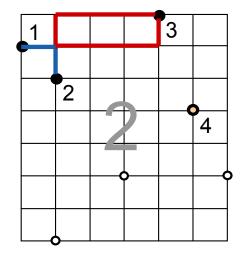

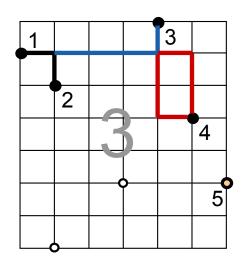

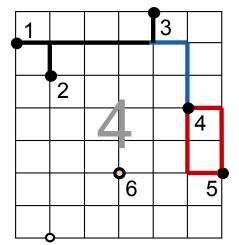

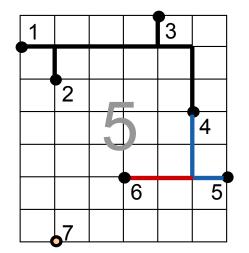

### **Heuristic Sequential Steiner Tree Example**

Placement

Global Routing

**Detailed Routing**

#### **Heuristic Sequential Steiner Tree Example**

**Global Routing**

Detailed Routing

### Part 3: CAD Algorithms

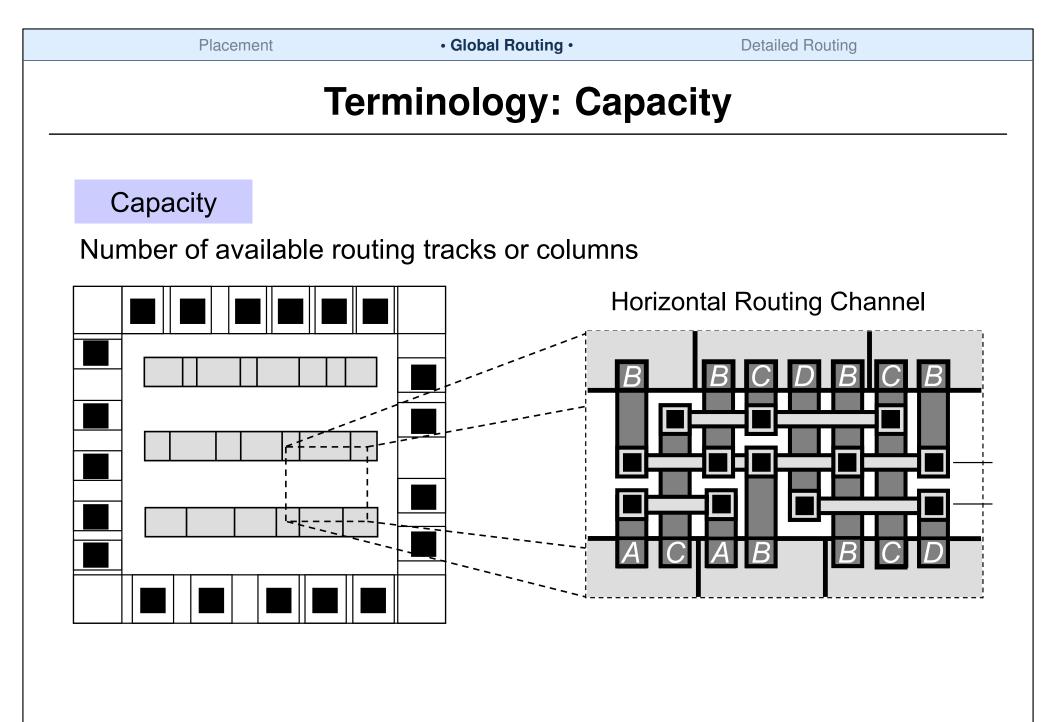

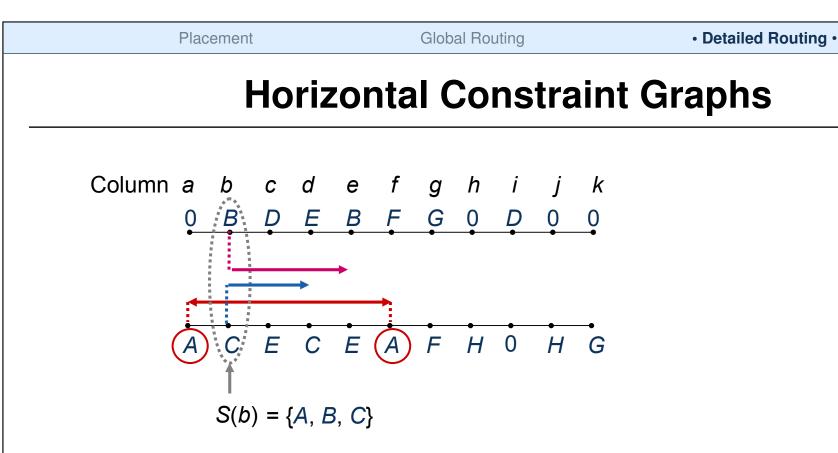

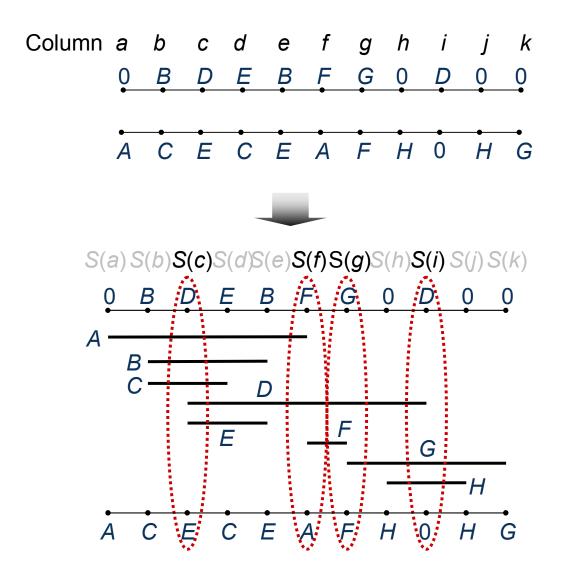

- Let *S*(*col*) denote the set of nets that pass through column *col*

- S(col) contains all nets that either (1) are connected to a pin in column col or (2) have pin connections to both the left and right of col

- Since horizontal segments cannot overlap, each net in *S*(*col*) must be assigned to a different track in column *col*

- S(col) represents the lower bound on the number of tracks in colum col; lower bound of the channel height is given by maximum cardinality of any S(col)

Global Routing

Detailed Routing

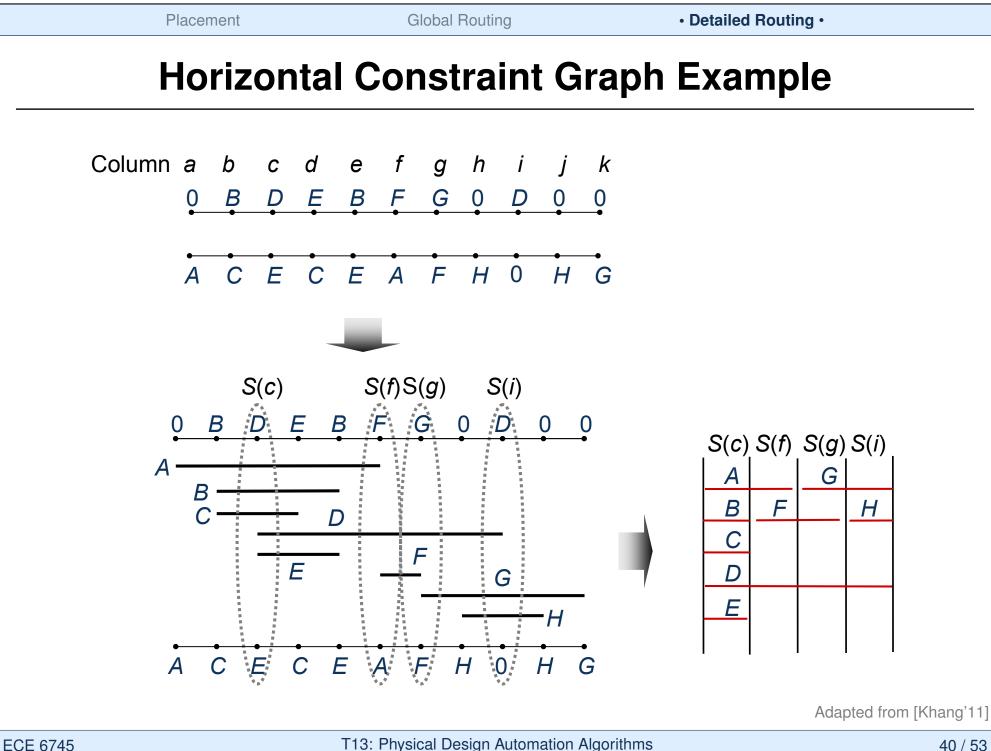

#### Horizontal Constraint Graph Example

Focus on columns which are not subsets of any other column

$S(a) = \{A\}$   $S(b) = \{A,B,C\}$   $S(c) = \{A,B,C,D,E\}$   $S(d) = \{A,B,C,D,E\}$   $S(e) = \{A,B,D,E\}$   $S(f) = \{A,D,F\}$   $S(f) = \{A,D,F\}$   $S(g) = \{D,F,G\}$   $S(h) = \{D,G,H\}$   $S(i) = \{D,G,H\}$   $S(j) = \{G,H\}$  $S(k) = \{G\}$

T13: Physical Design Automation Algorithms

40 / 53

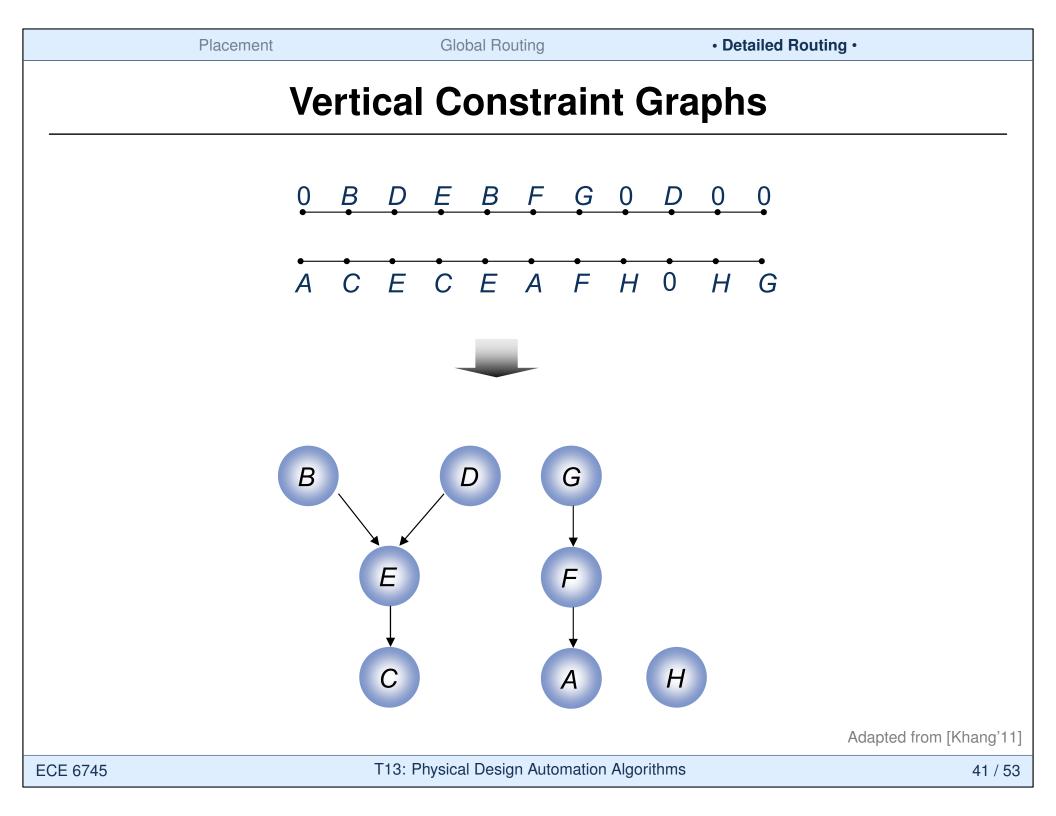

Placement

**Global Routing**

Detailed Routing

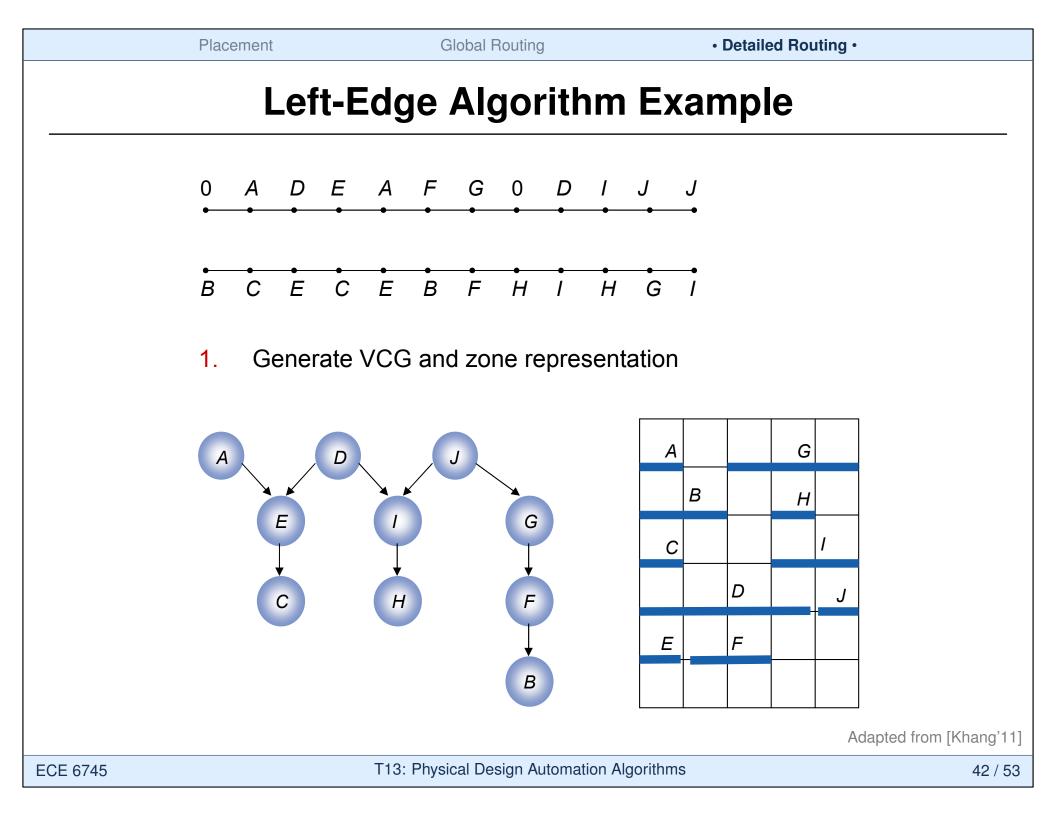

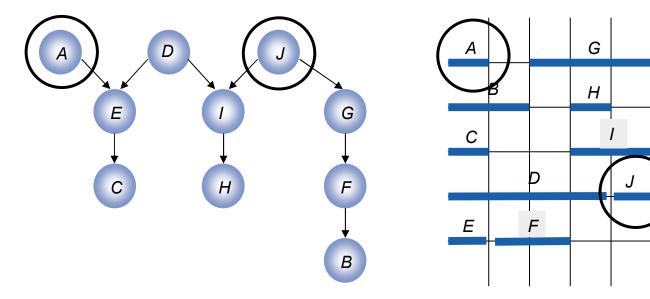

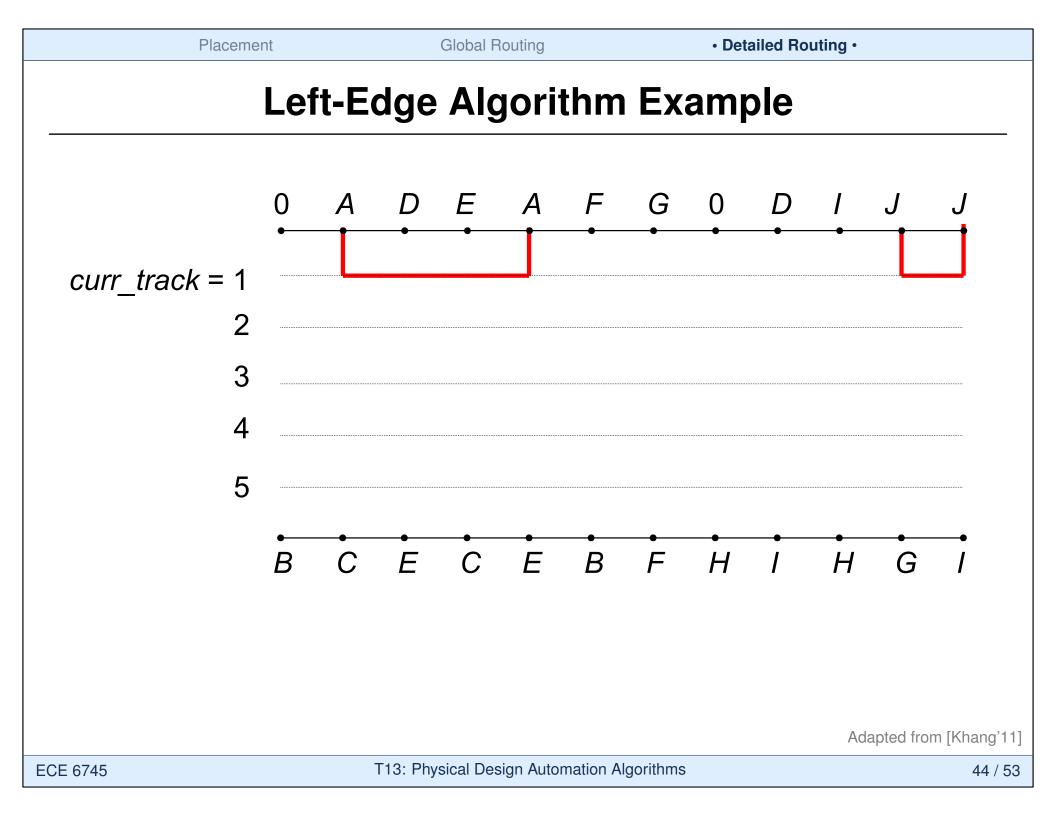

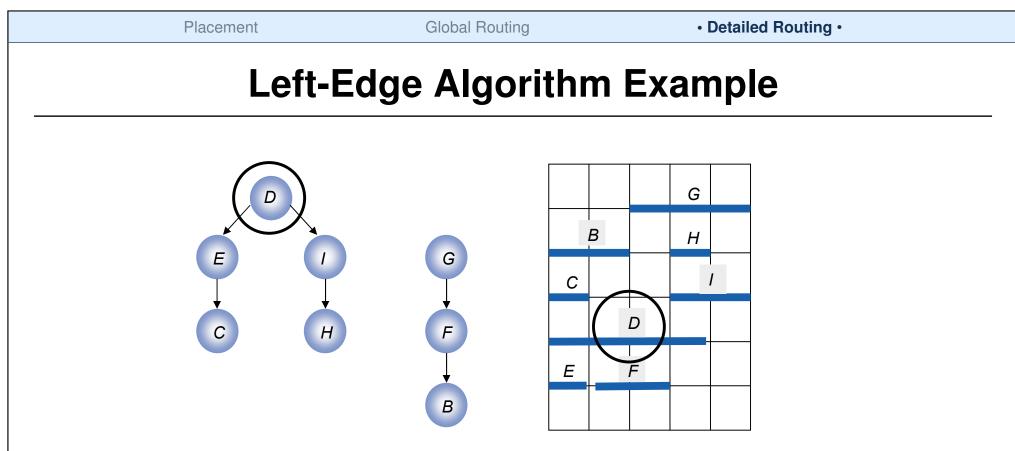

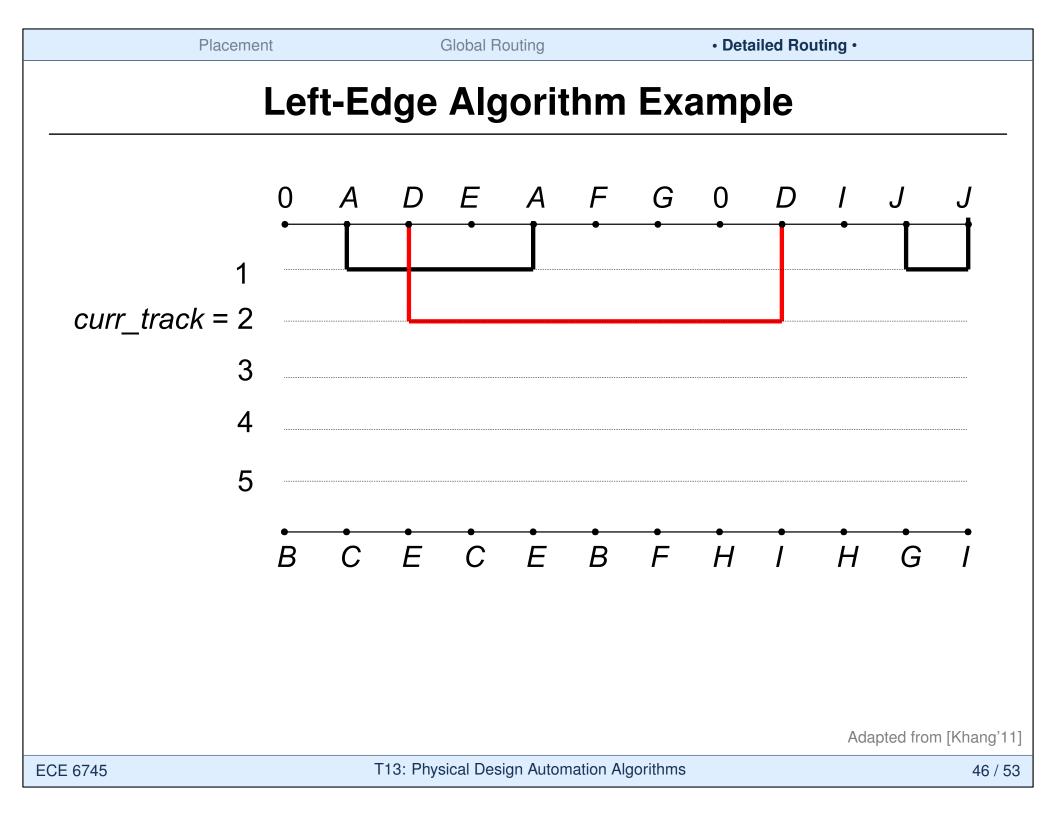

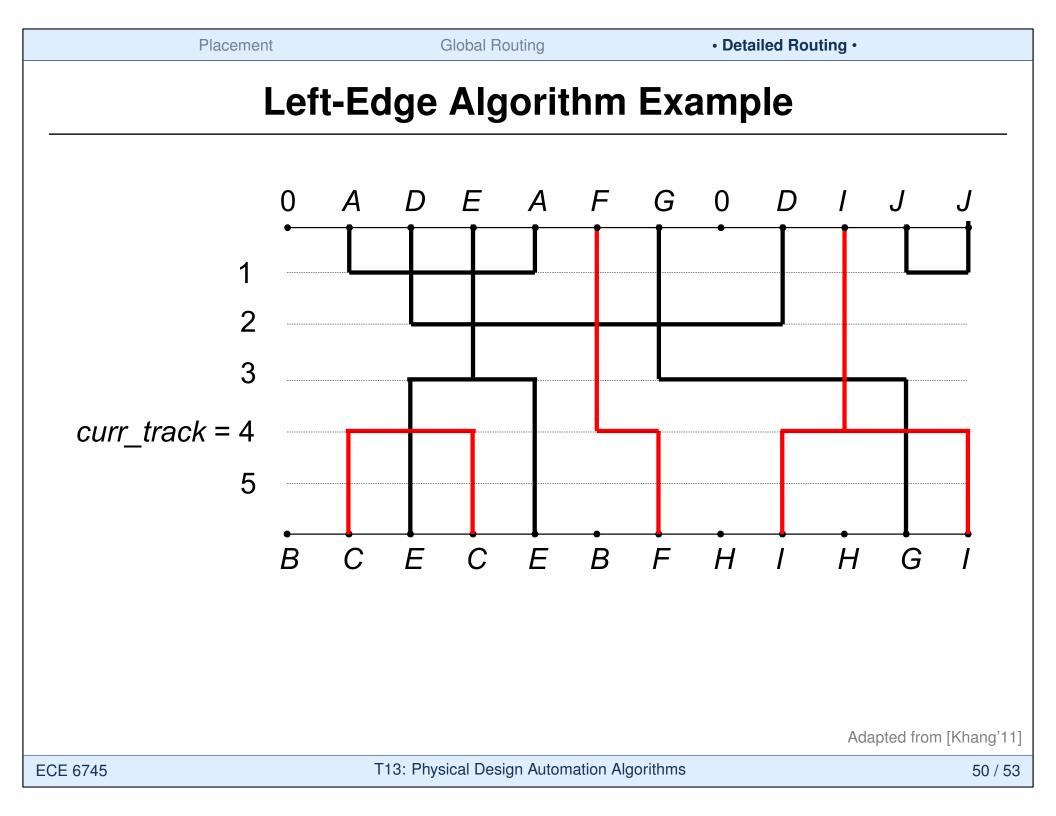

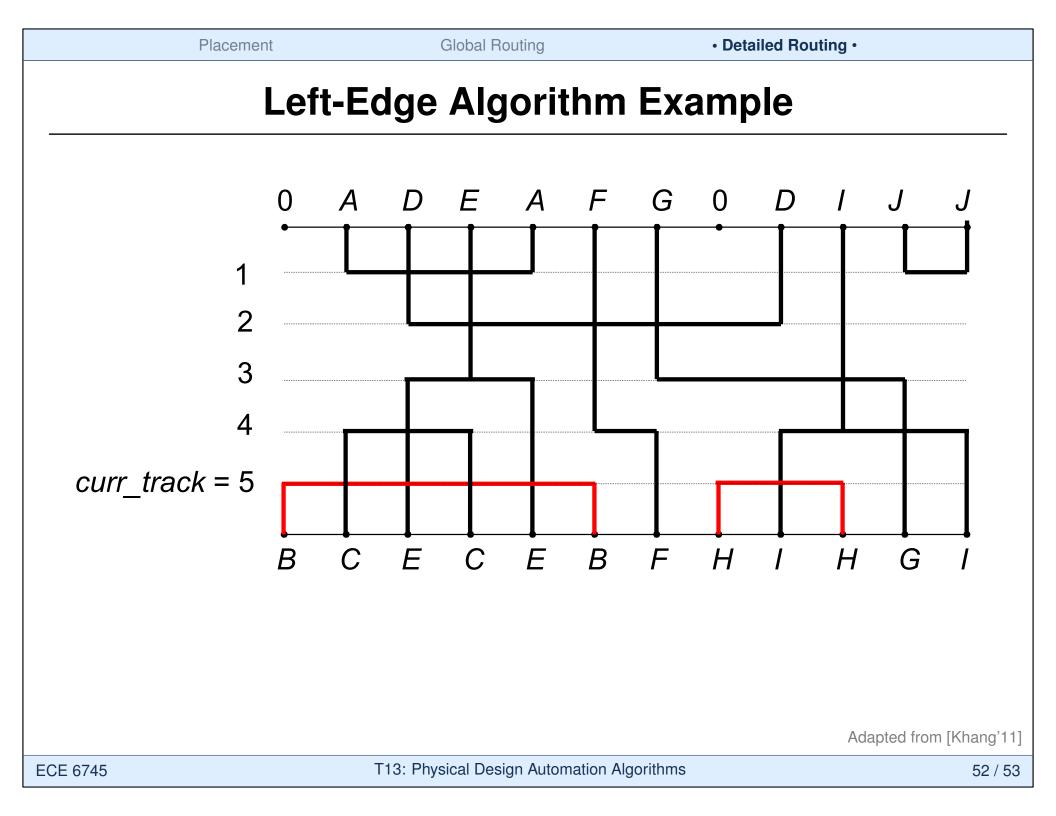

## Left-Edge Algorithm Example

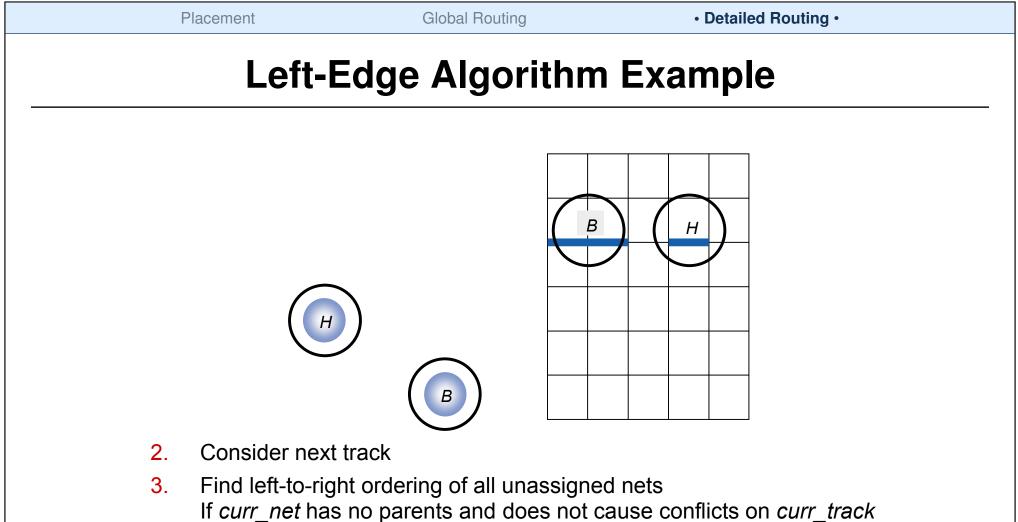

- 2. Consider next track

- Find left-to-right ordering of all unassigned nets If curr\_net has no parents and does not cause conflicts on curr\_track assign curr\_net

*curr\_track* = 1: Net *A* Net *J*

4. Delete placed nets (A, J) in VCG and zone representation

- 2. Consider next track

- Find left-to-right ordering of all unassigned nets If curr\_net has no parents and does not cause conflicts on curr\_track assign curr\_net

*curr\_track* = 2: Net *D*

4. Delete placed nets (*D*) in VCG and zone representation

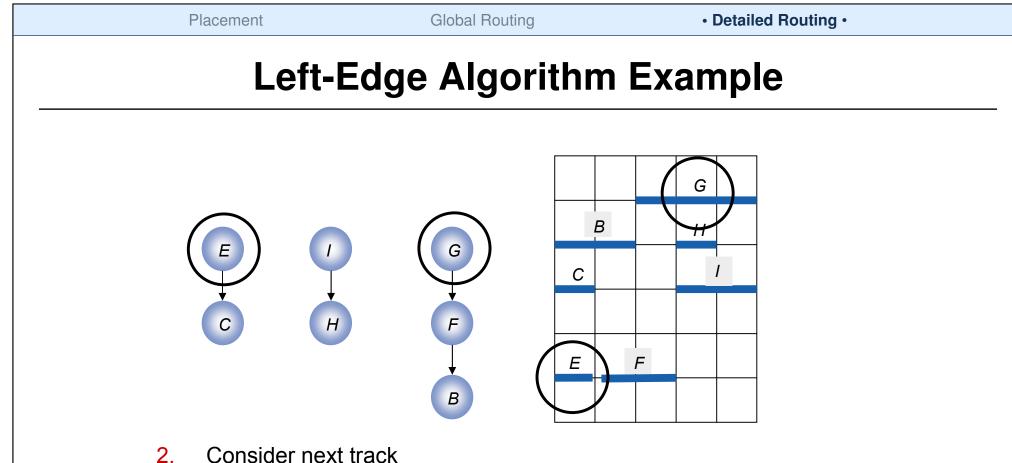

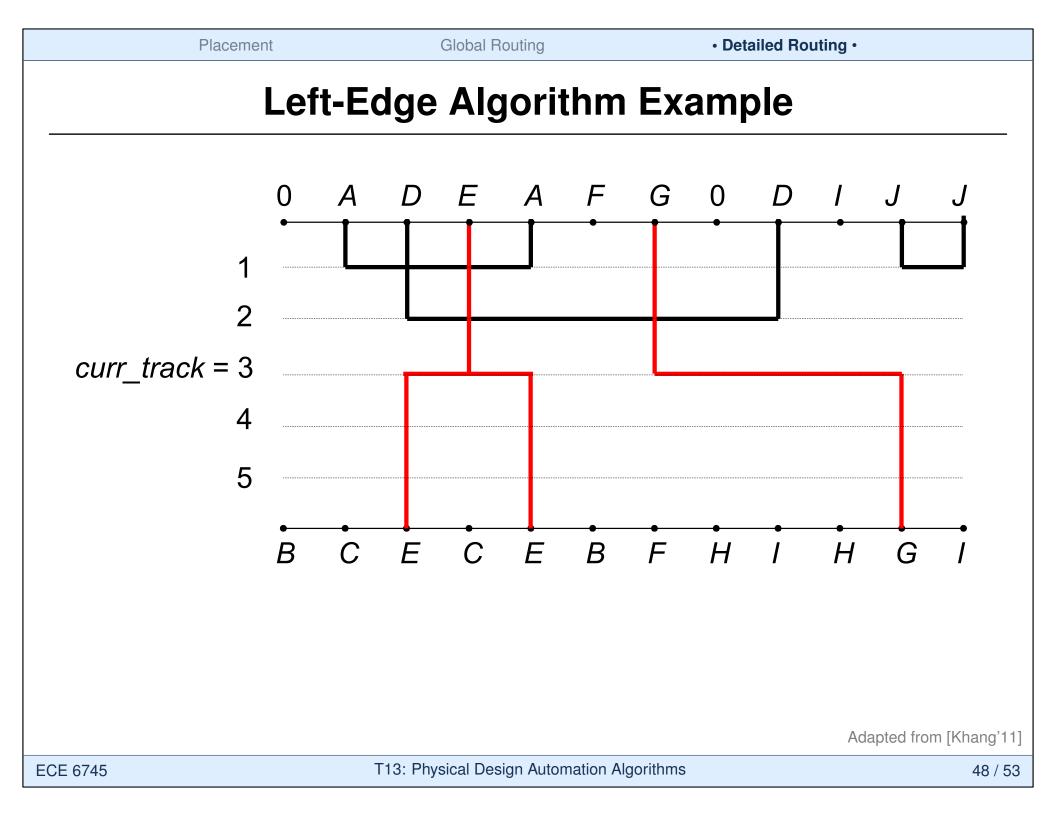

3. Find left-to-right ordering of all unassigned nets If *curr\_net* has no parents and does not cause conflicts on *curr\_track* assign *curr\_net*

*curr\_track* = 3: Net *E* Net *G*

4. Delete placed nets (*E*, *G*) in VCG and zone representation

**Global Routing**

Detailed Routing

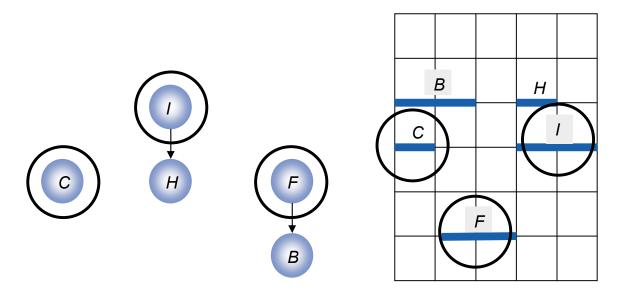

# Left-Edge Algorithm Example

- 2. Consider next track

- Find left-to-right ordering of all unassigned nets If curr\_net has no parents and does not cause conflicts on curr\_track assign curr\_net

*curr\_track* = 4: Net *C* Net *F* Net *I*

4. Delete placed nets (*C*, *F*, *I*) in VCG and zone representation

assign *curr\_net*

*curr\_track* = 5: Net *B* Net *H*

4. Delete placed nets (*B*, *H*) in VCG and zone representation

### Acknowledgments

- [Devadas'06] S. Devadas, "VLSI CAD Flow: Logic Synthesis, Placement, and Routing," MIT 6.375 Complex Digital Systems Guest Lecture Slides, 2006.

- [Kahng'11] A.B. Kahng, J. Liening, I.L. Markov, and J. Hu. Companion Slides for "VLSI Physical Design: From Graph Partitioning to Timing Closure," Springer 2011.