## ECE 6745 Complex Digital ASIC Design Topic 7: Packaging, Power Distribution, Clocking, and I/O

**Christopher Batten**

School of Electrical and Computer Engineering Cornell University

http://www.csl.cornell.edu/courses/ece6745

I/O

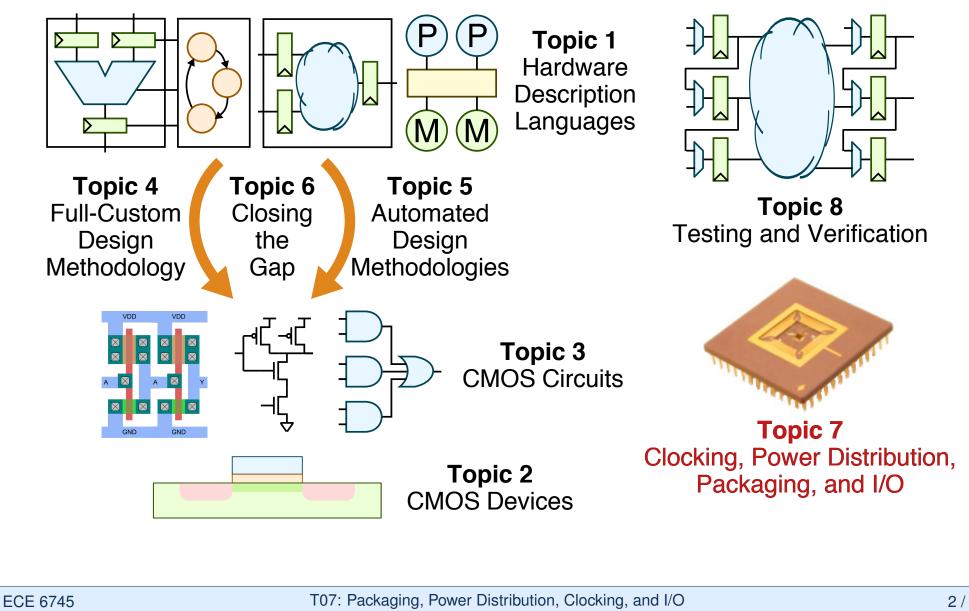

#### **Part 1: ASIC Design Overview**

| Power Distribution | Clocking | I/O    |  |

|--------------------|----------|--------|--|

| Agenda             |          |        |  |

|                    |          |        |  |

|                    |          |        |  |

|                    |          |        |  |

|                    |          |        |  |

| ibution            |          |        |  |

|                    |          |        |  |

|                    |          |        |  |

|                    |          |        |  |

|                    |          |        |  |

|                    |          |        |  |

|                    |          | Agenda |  |

ECE 6745

<sup>296-</sup>pin PGA

#### What makes a good package?

- Low cost

- Small size

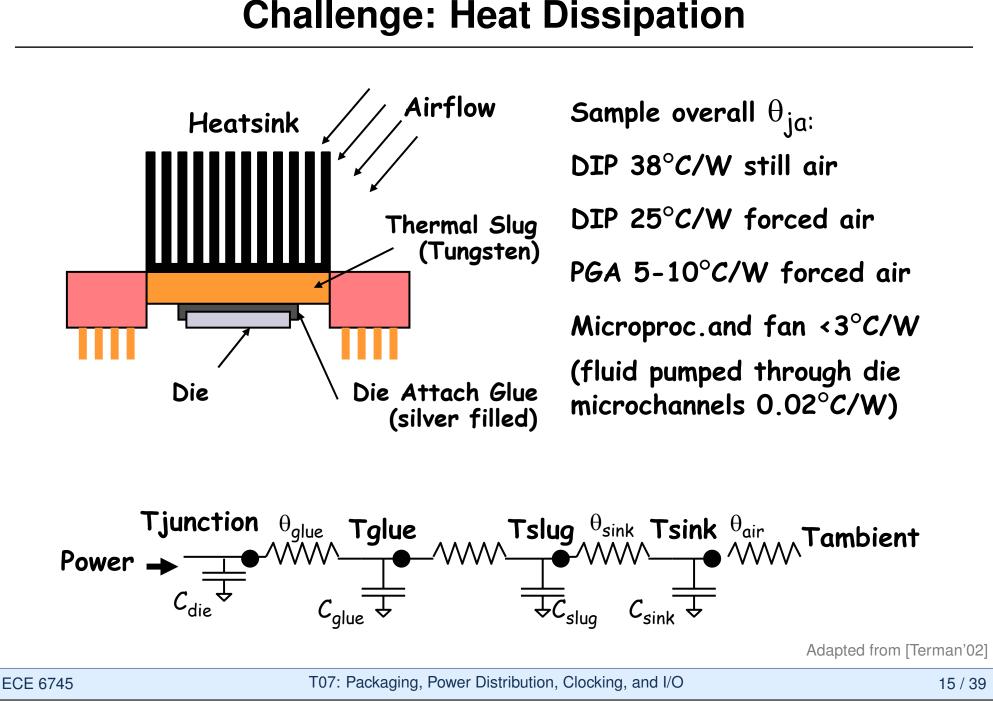

- Good thermal performance

- Large number of pins

- Low pin parasitics

- Easy to test

- Highly reliable

Adapted from [Weste'11]

| Packaging • |                     | ging •                                          | Power Distribution                                                                                                                                                                         | Clocking           | I/O           |

|-------------|---------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------|

|             | Basic Package Types |                                                 |                                                                                                                                                                                            |                    |               |

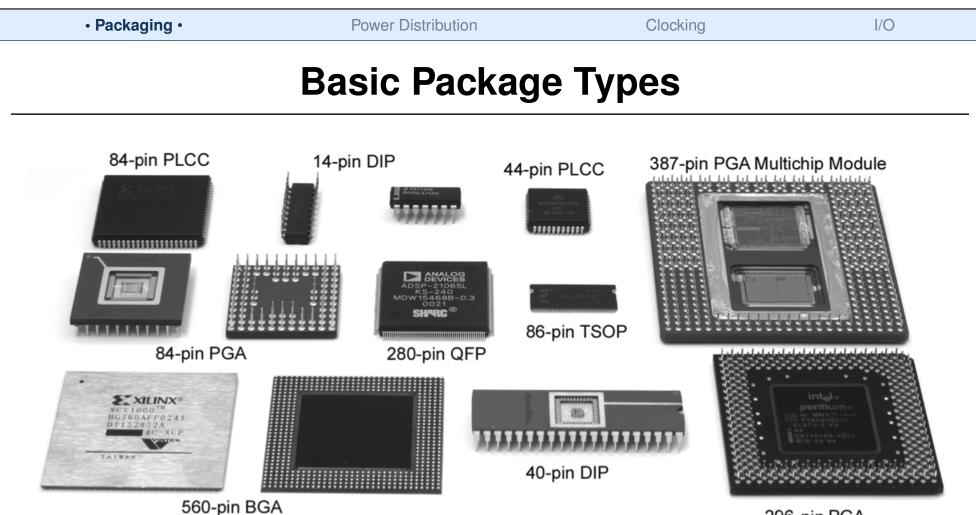

|             | DIP                 | 8–64                                            | Two rows of through-hole pins. 100mil pitch. Low cost. Long wires between chip and corner pins.<br>Array of through-hole pins. 100mil pitch. Low thermal resistance and higher pin counts. |                    |               |

|             | PGA                 | 65-400                                          |                                                                                                                                                                                            |                    |               |

|             | SOIC                | 8–28                                            | Two rows of SMT pins. 50mil pitch. Low cost.                                                                                                                                               |                    | ow cost.      |

|             | TSOP                | 28–86                                           | Two rows of SMT pir<br>package. Used in D                                                                                                                                                  | •                  | h in thin     |

|             | QFP                 | 44–240                                          | SMT pins on 4 sides                                                                                                                                                                        | s. 15–50mil pitch. | High density. |

|             | BGA                 | 49–2000+                                        | 49–2000+ Array of SMT solder balls on undersid<br>on 15–50mil pitch. Very high density v<br>parasitics. Costly assembly.                                                                   |                    |               |

|             | LGA                 | balls. Commonly used with sockets (processors). |                                                                                                                                                                                            |                    |               |

| ECE         | E 6745              |                                                 | T07: Packaging, Power Distribution, C                                                                                                                                                      | locking, and I/O   | 6 / 39        |

Adapted from [Weste'11]

T07: Packaging, Power Distribution, Clocking, and I/O

7 / 39

Power Distribution

Clocking

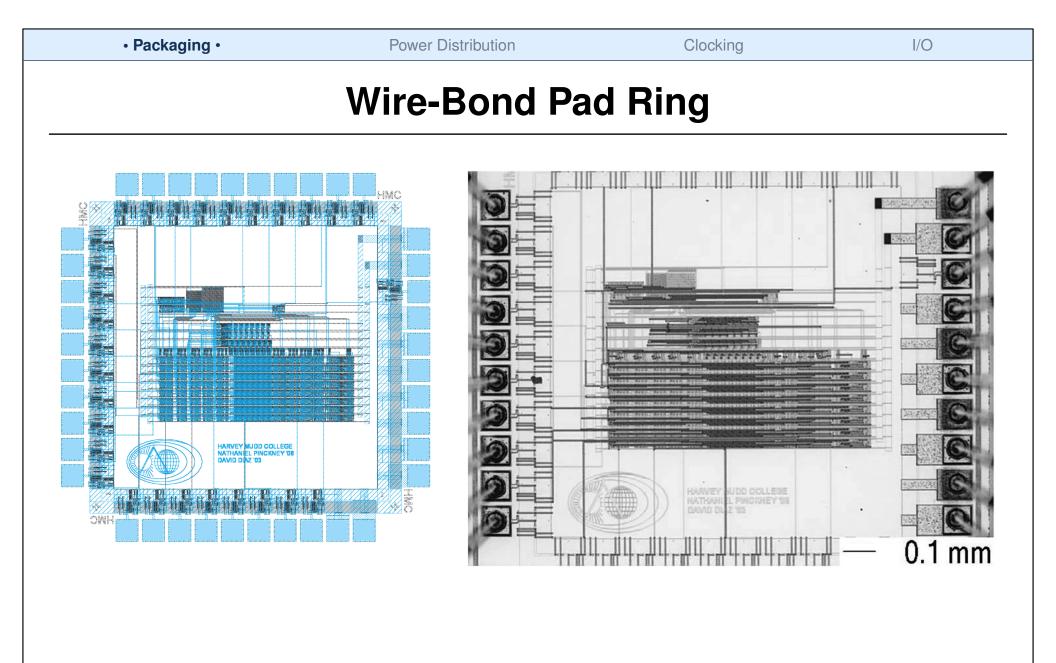

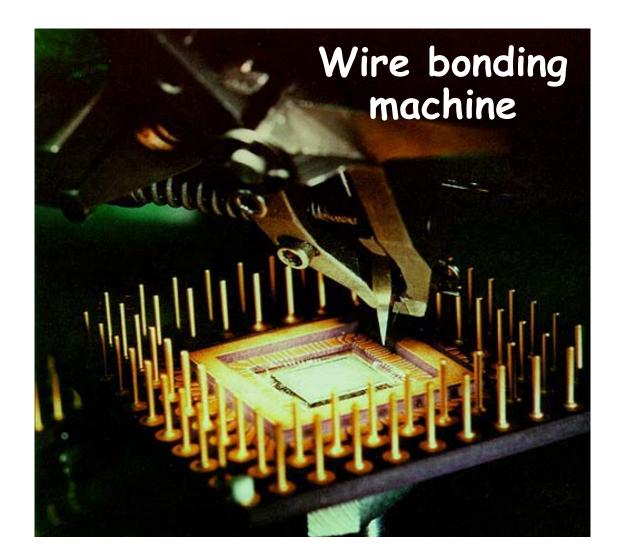

#### **Wire Bonding Process**

Usually ultrasonic welding connects wire to package and die pad

Bond wires can be aluminum or gold

Different thicknesses of bond wire tradeoff parasitic inductance and resistance versus density

Can wirebond to die pad pitches of around 100µm

Adapted from [Terman'02]

Adapted from [Weste'11]

I/O

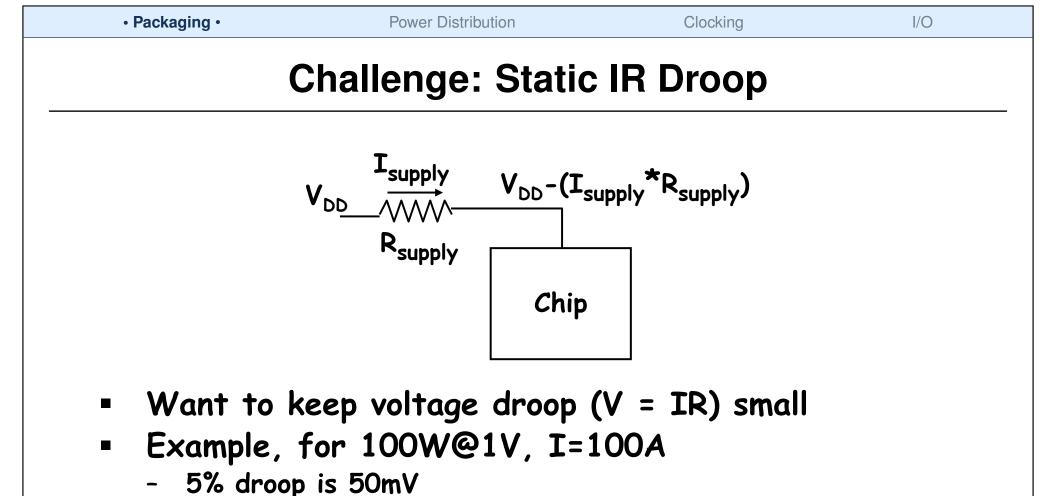

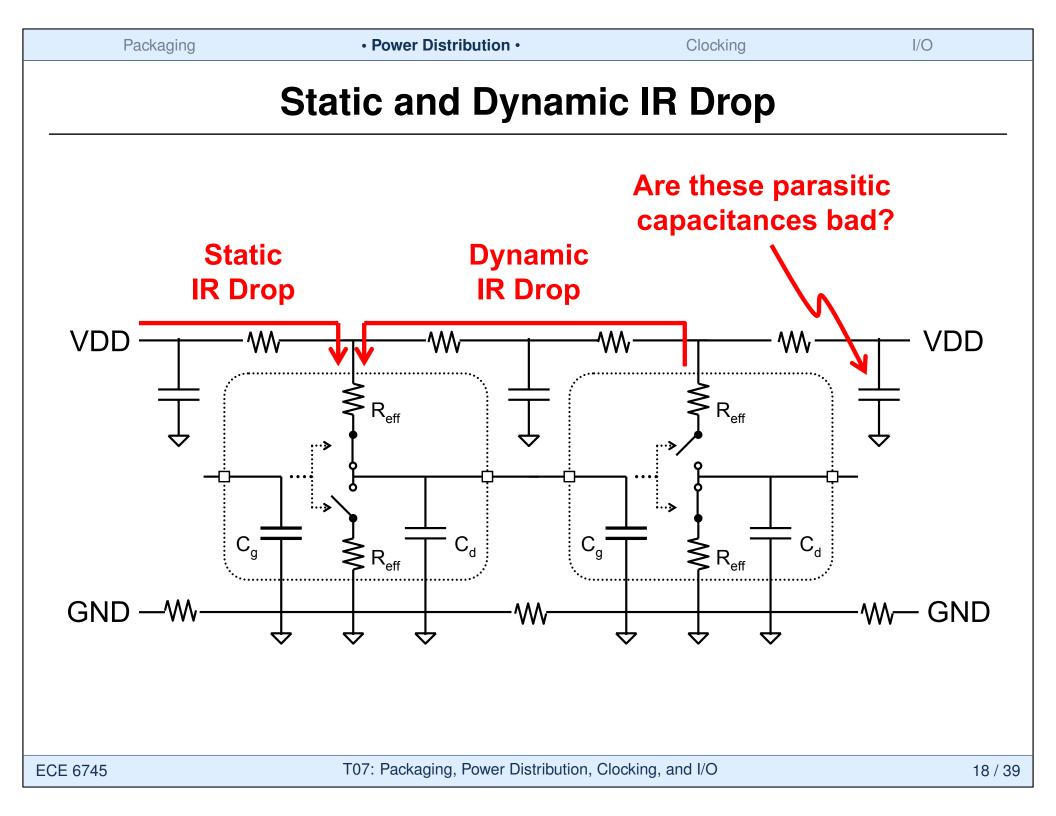

#### **Challenge: Power Delivery Scaling**

Power = Volts  $\times$  Amps

- CPU power consumption is increasing

- 2x per technology generation

- Supply voltages are dropping

- have to control electric field strength as transistors shrink

- keep power from growing even faster

- Power is going up, voltage is going down = current rising fast

- ▷ 100W at 1V implies 100A of current

Want very low resistance on-chip power network

Need very short fat wires to board power regulator

- At 100A, need effective supply resistance < 0.0005  $\Omega$

Dissipate 5W heat just in power supply leads

Use multiple parallel Vdd/GND pins

Adapted from [Terman'02]

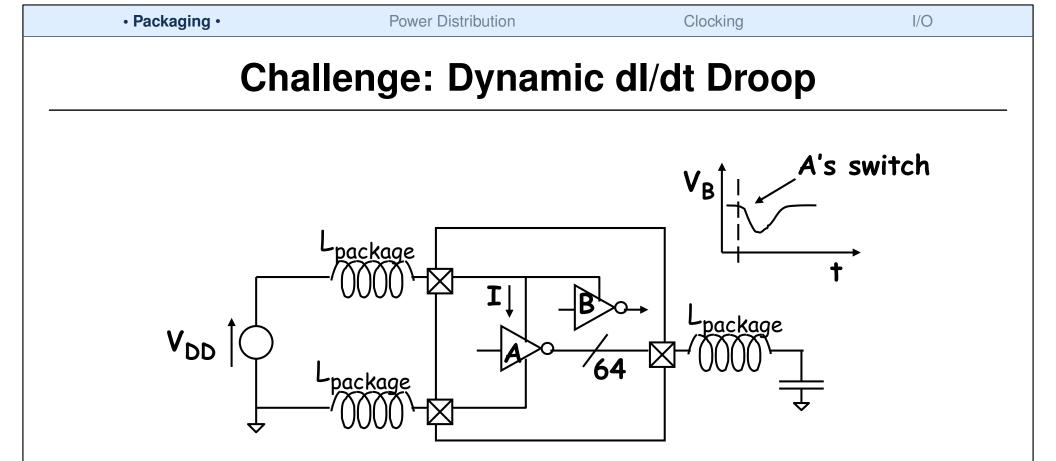

- A large number of output drivers A switching high try to pull current through the power supply inductance, causing the internal power rail connected to gate B to droop (V=LdI/dt)

- Gates driven by B may switch incorrectly.

Adapted from [Terman'02]

| Packaging | Power Distribution • | Clocking | I/O |

|-----------|----------------------|----------|-----|

|           | Agenda               |          |     |

|           |                      |          |     |

|           |                      |          |     |

| Packaging |                      |          |     |

| Power Dis | tribution            |          |     |

|           |                      |          |     |

| Clocking  |                      |          |     |

|           |                      |          |     |

| 1/0       |                      |          |     |

|           |                      |          |     |

I/O

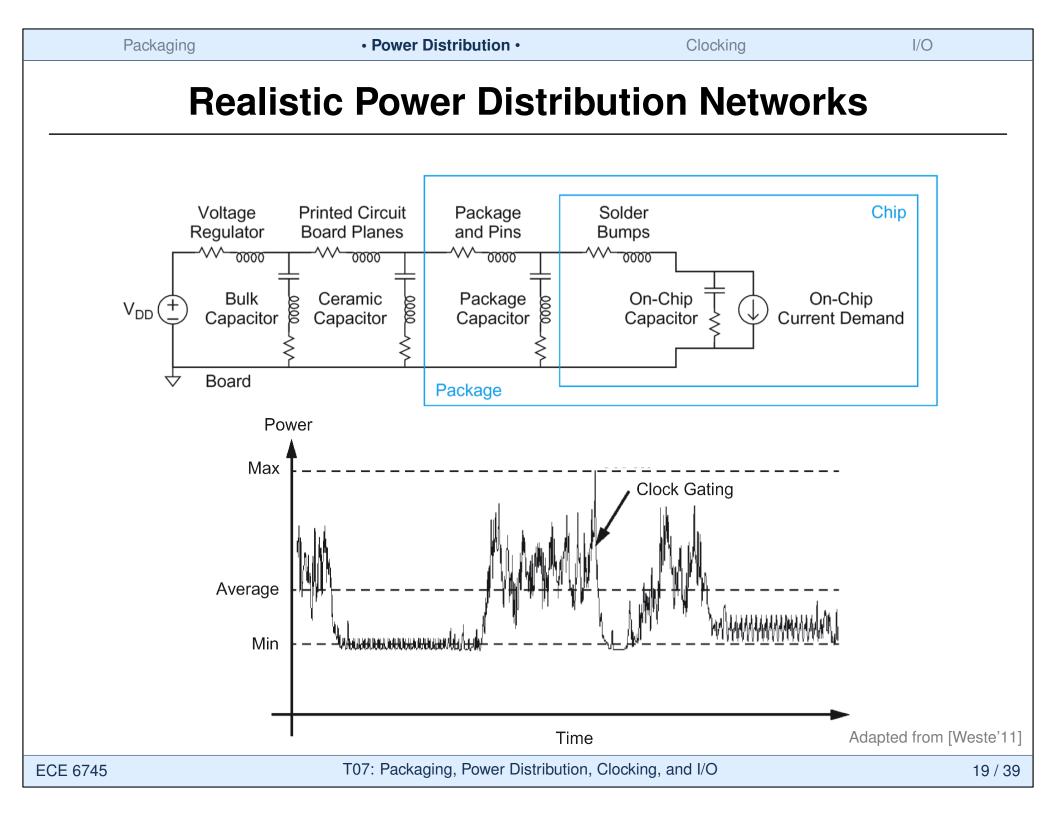

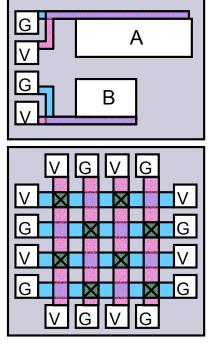

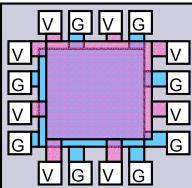

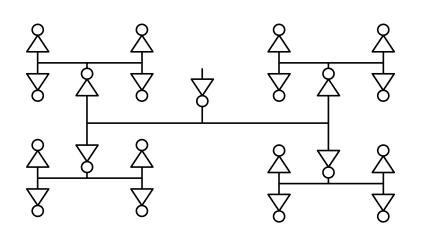

#### **Various Approaches to Power Distribution**

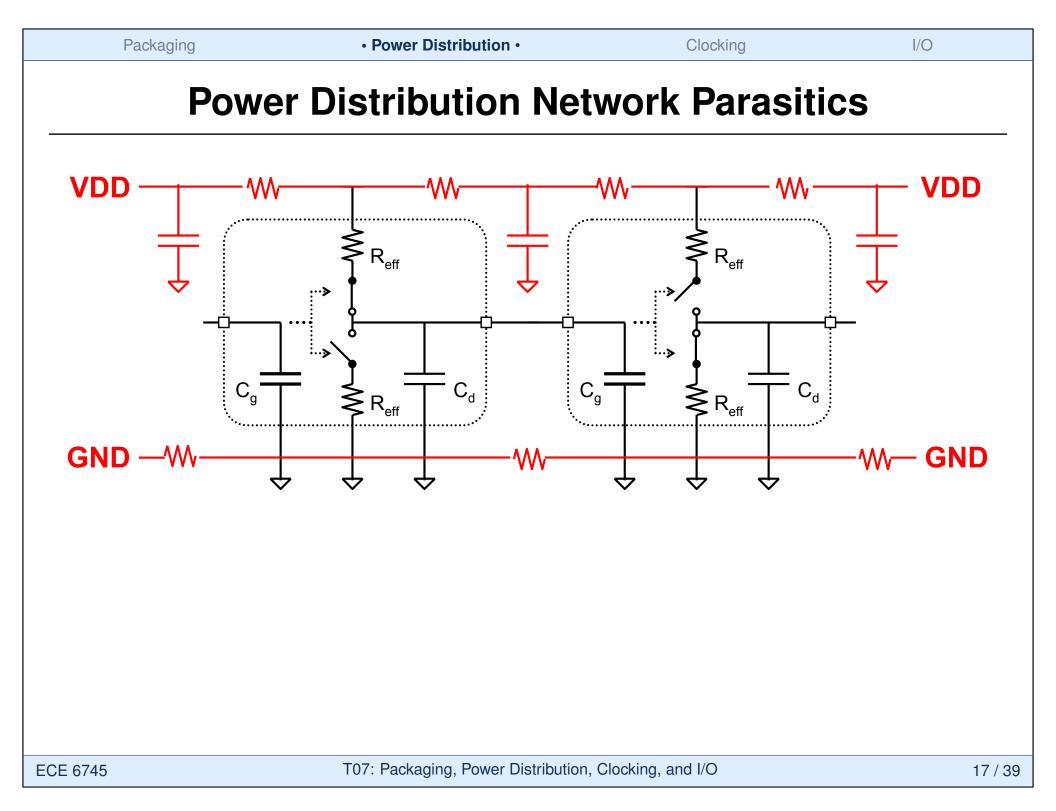

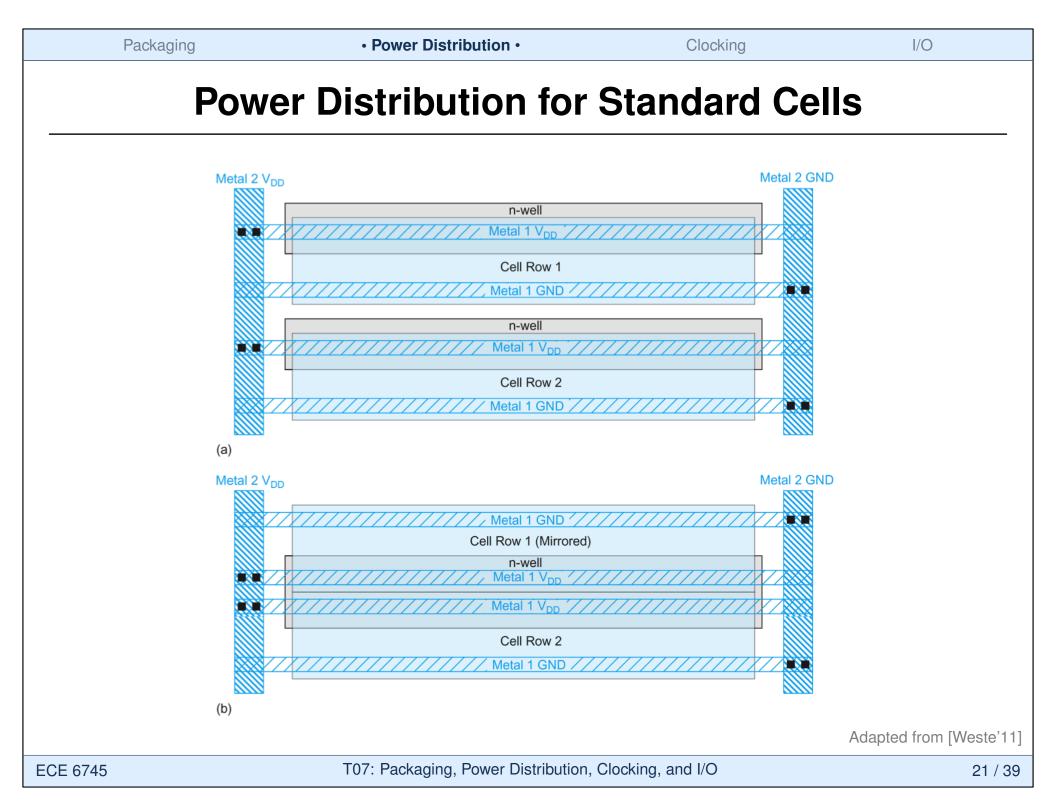

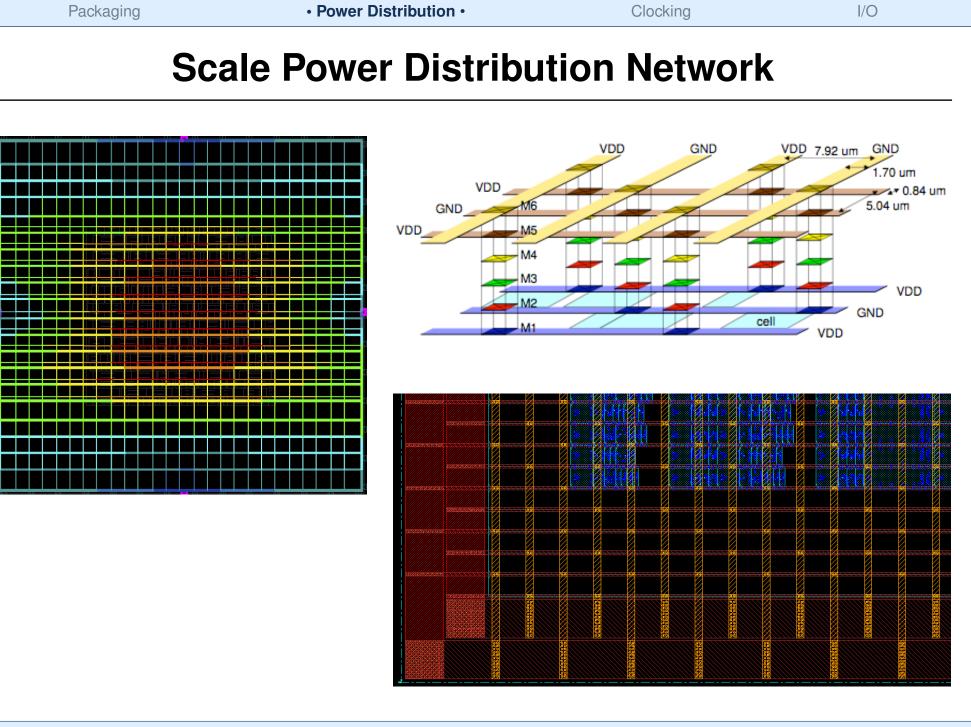

Routed power distribution on two stacked layers of metal (one for VDD, one for GND). OK for low-cost, low-power designs with few layers of metal.

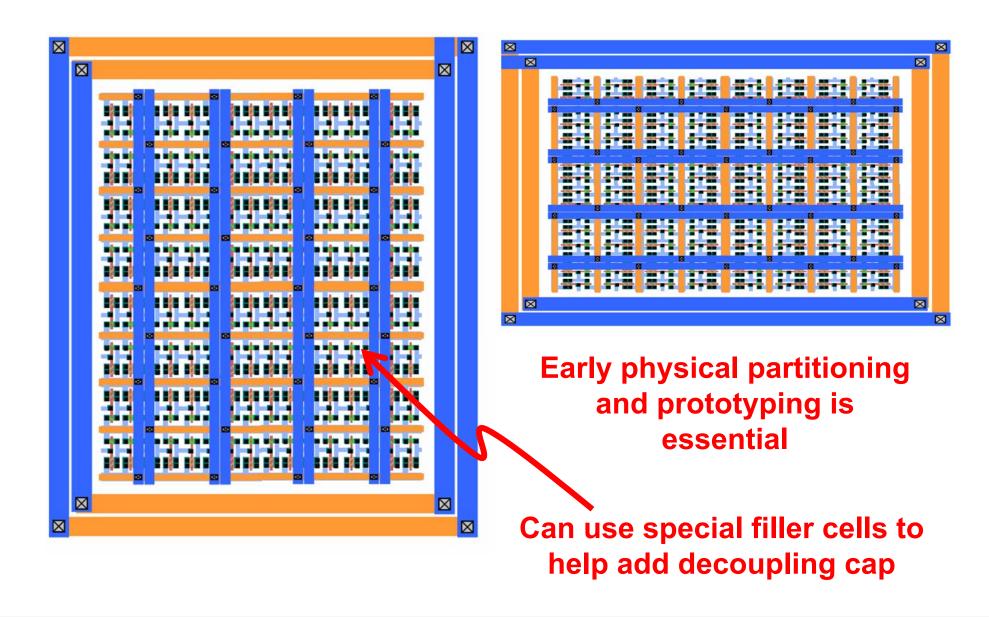

Power Grid. Interconnected vertical and horizontal power bars. Common on most high-performance designs. Often well over half of total metal on upper thicker layers used for VDD/GND.

Dedicated VDD/GND planes. Very expensive. Only used on Alpha 21264. Simplified circuit analysis. Dropped on subsequent Alphas.

I/O

#### **Modular Power Distribution Networks**

T07: Packaging, Power Distribution, Clocking, and I/O

| Packaging | Power Distribution | Clocking      · | I/O |

|-----------|--------------------|-----------------|-----|

|           | Agenc              | la              |     |

|           |                    |                 |     |

| Packaging |                    |                 |     |

| Power Dis | tribution          |                 |     |

| Clocking  |                    |                 |     |

| I/O       |                    |                 |     |

|           |                    |                 |     |

|           |                    |                 |     |

ECE 6745

T07: Packaging, Power Distribution, Clocking, and I/O

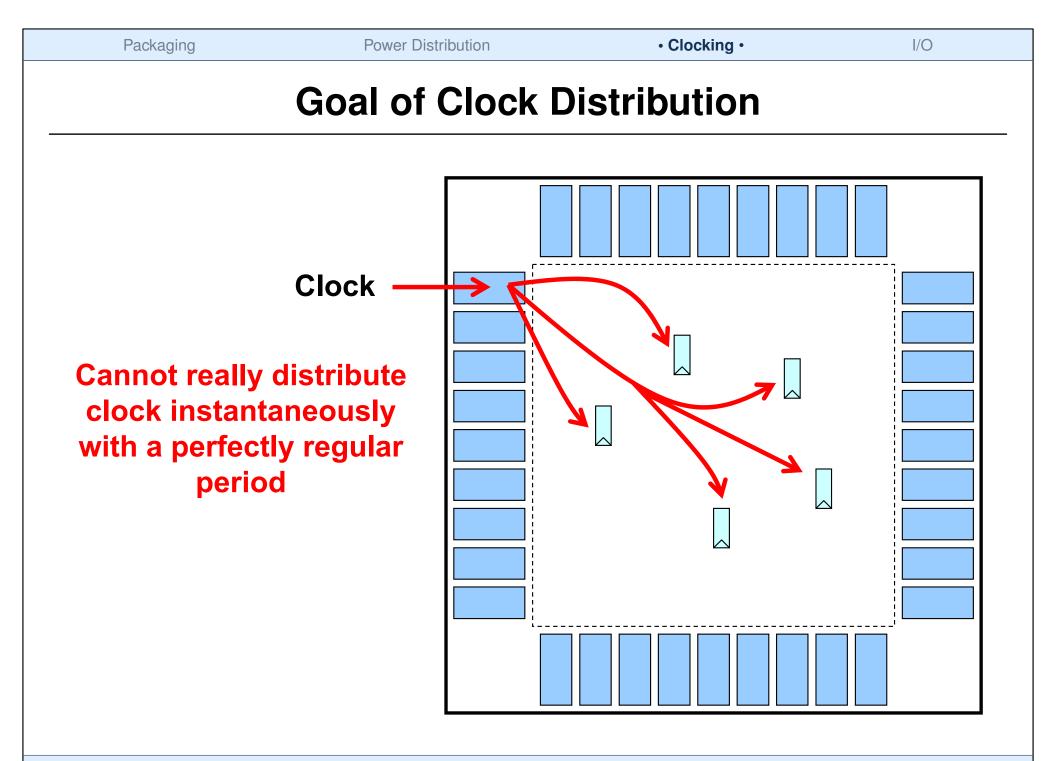

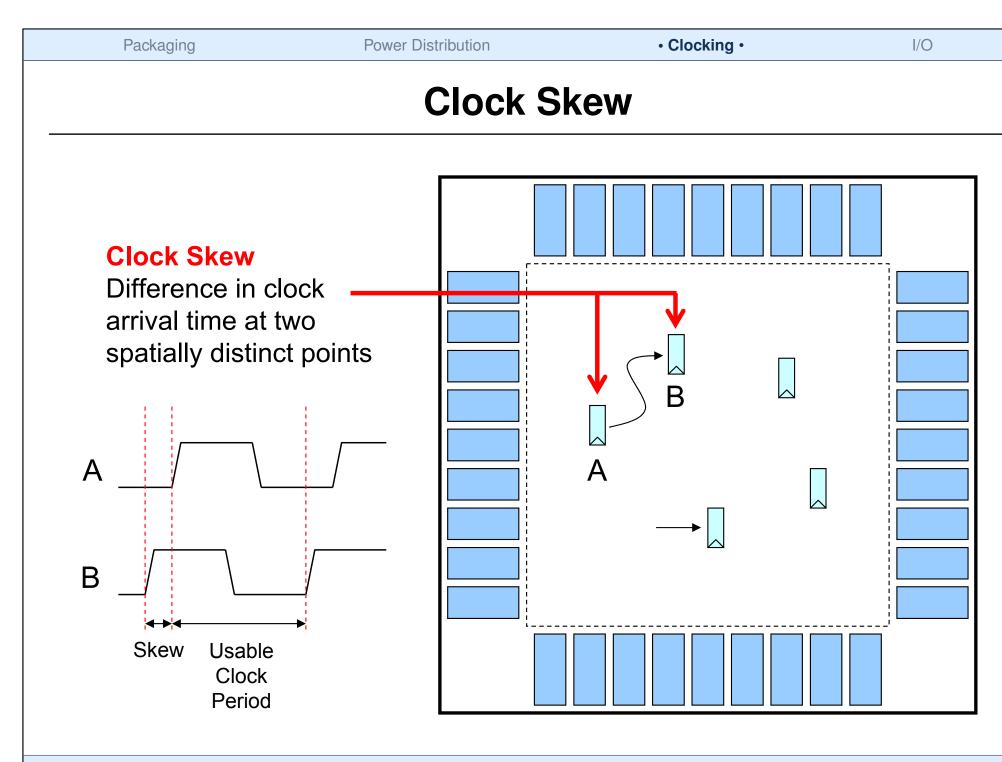

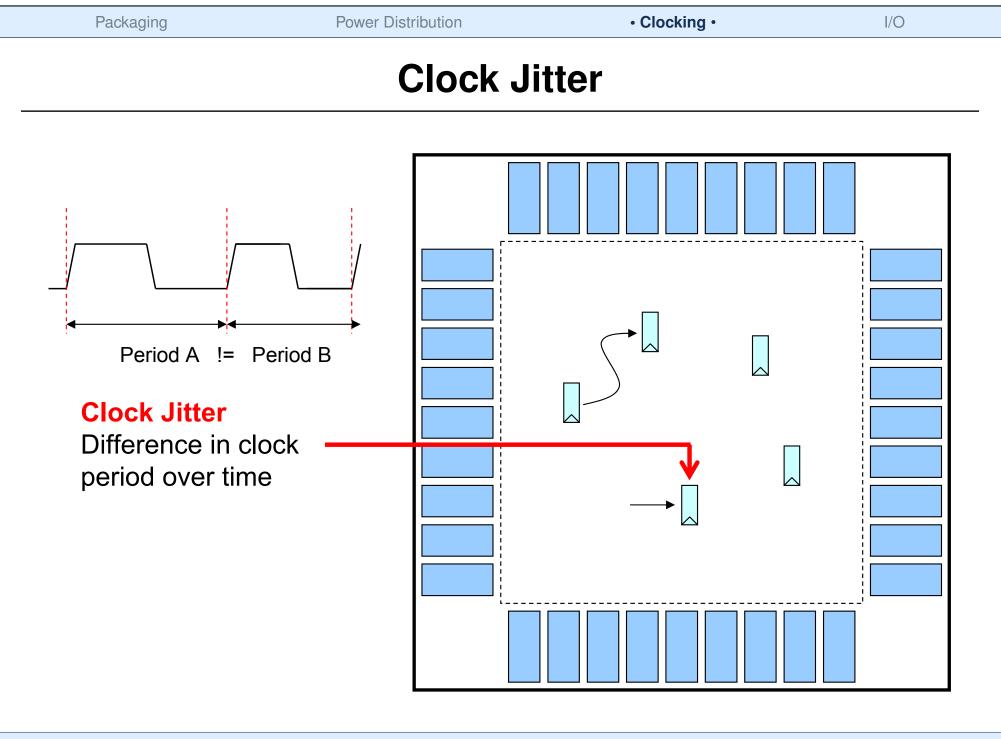

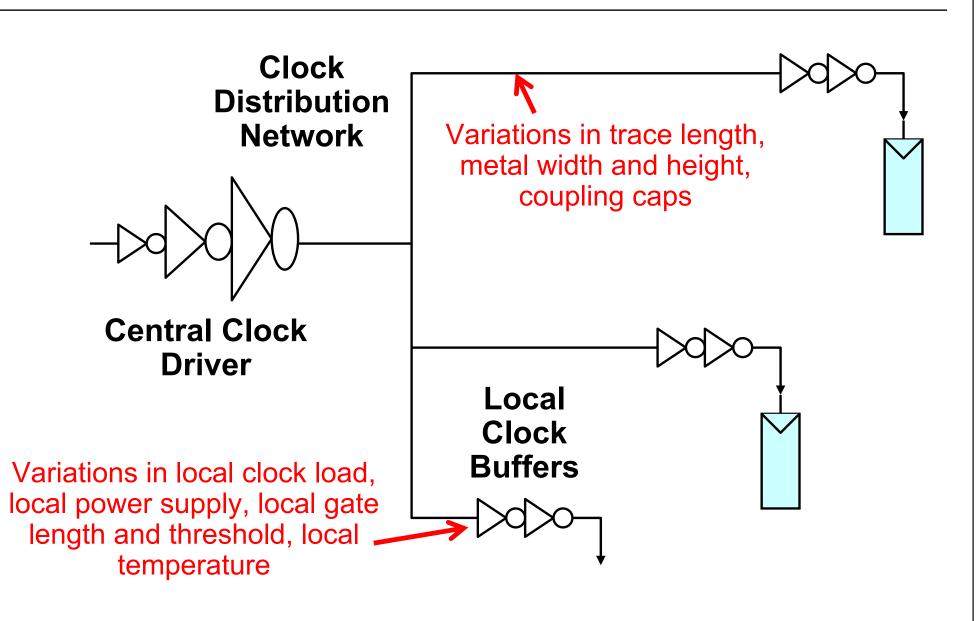

#### **Sources of Clock Skew and Jitter**

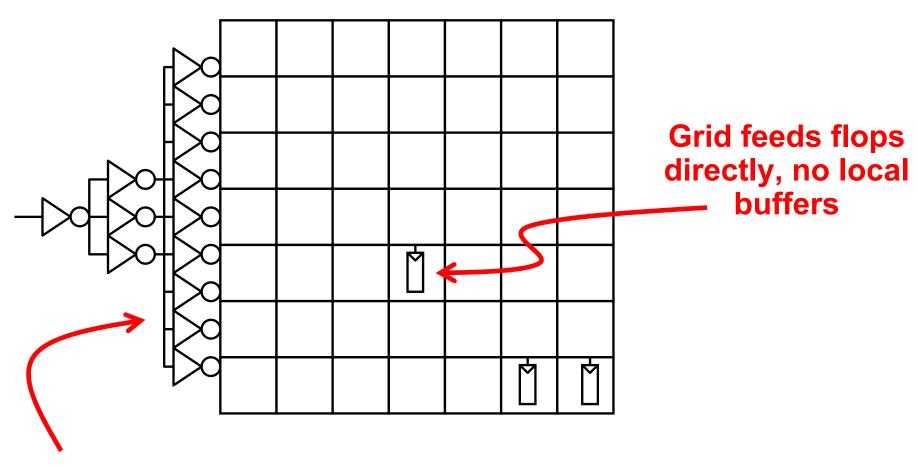

#### **Clock Grids: Low Skew but High Power**

Clock driver tree spans height of chip Internal levels shorted together

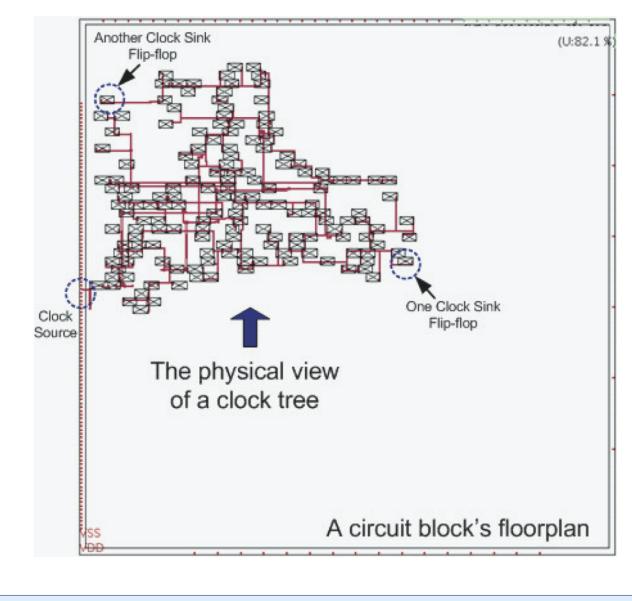

#### **Clock Trees: More skew but Less Power**

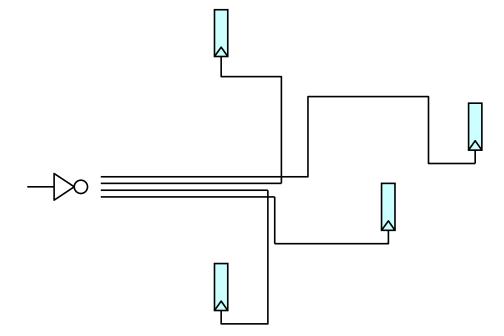

**H-Tree**

**RC-Tree**

I/O

Recursive pattern to distribute signals uniformly with equal delay over area Each branch is individually routed to balance RC delay

Power Distribution

Clocking

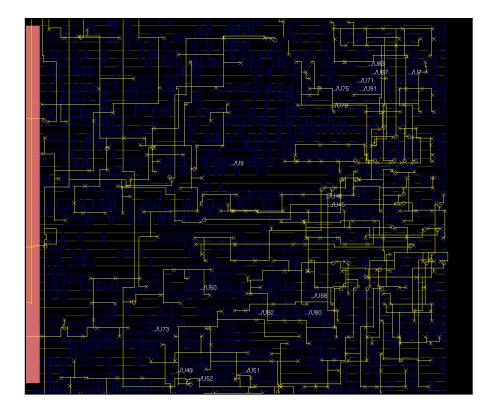

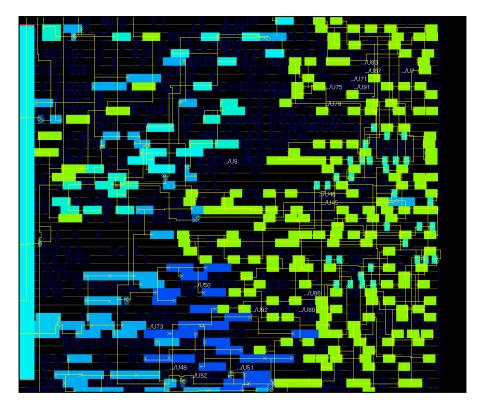

#### **Clock Tree Synthesis**

# CAD tools generate balanced RC trees

Static analysis to measure clock skew and factor it into static timing analysis

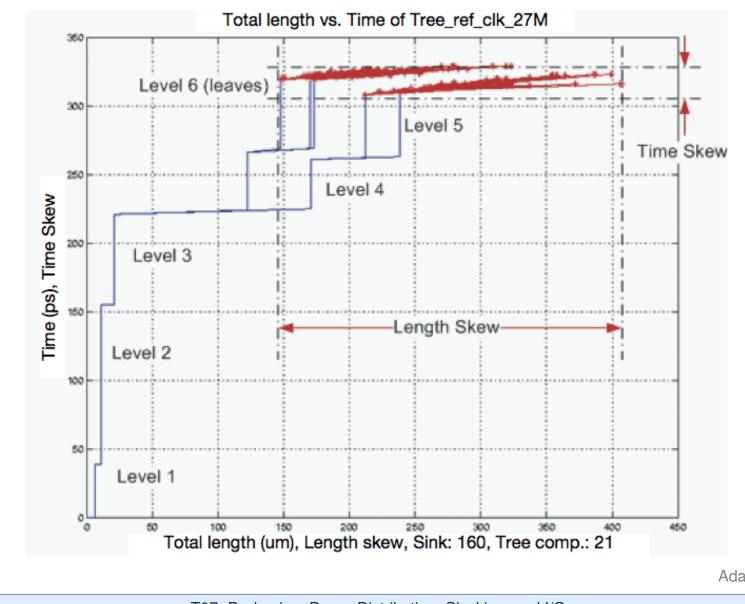

#### **Example Skew/Jitter Analysis**

Adapted from [Xiu'08]

#### **Example Skew/Jitter Analysis**

ECE 6745

T07: Packaging, Power Distribution, Clocking, and I/O

Adapted from [Xiu'08]

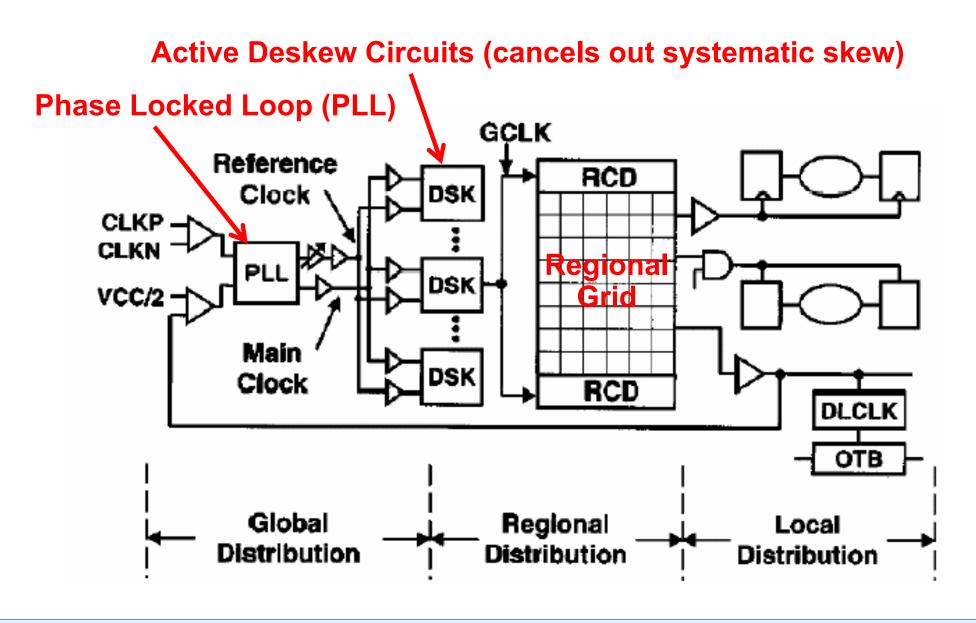

#### **Active Deskewing Circuits in Intel Itanium**

| Packaging  | Power Distribution | Clocking | • I/O • |  |

|------------|--------------------|----------|---------|--|

|            | Agenda             |          |         |  |

|            |                    |          |         |  |

|            |                    |          |         |  |

| Packaging  |                    |          |         |  |

|            |                    |          |         |  |

| Power Dist | Power Distribution |          |         |  |

|            |                    |          |         |  |

| Clocking   |                    |          |         |  |

|            |                    |          |         |  |

| I/O        |                    |          |         |  |

|            |                    |          |         |  |

|            |                    |          |         |  |

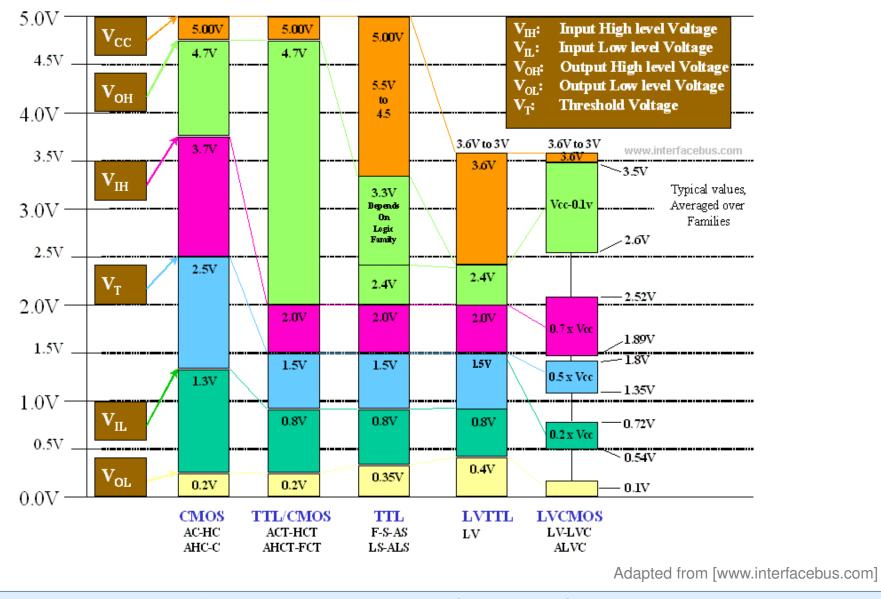

#### **Single-Ended I/O Standards**

T07: Packaging, Power Distribution, Clocking, and I/O

### **High-Speed Serial I/Os**

- Pins are an expensive part of a system

- Physical cost of adding pin to package

- ▷ Size of package increases with more pins and on-pkg routing to pin

- Bonding cost per pin

- Size of motherboard depends on package size

- More pins complicates board-level routing

- Board testing time grows with number of pins

- Reliability is function of number of solder connections

- Trend towards high-speed serial I/O

- As computing performance grows, pins become system bottleneck

- Want maximum bandwidth from available pins

- ▷ Current SerDes run at 3–6 Gb/s per link at <200 mW

#### Acknowledgments

- [www.interface.com] "Chart of Low Voltage IC Switching." http://www.interfacebus.com/Chart-of-Low-Voltage-IC-Switching.png

- [Terman'02] C. Terman and K. Asanović, MIT 6.371 Introduction to VLSI Systems, Lecture Slides, 2002.

- [Weste'11] N. Weste and D. Harris, "CMOS VLSI Design: A Circuits and Systems Perspective," 4th ed, Addison Wesley, 2011.

- [Xiu'08] L. Xiu, "VLSI Circuit Design Methodologies," Wiley-IEEE Press, 2008.