# ECE 6745 Complex Digital ASIC Design Topic 3: CMOS Circuits

**Christopher Batten**

School of Electrical and Computer Engineering Cornell University

http://www.csl.cornell.edu/courses/ece6745

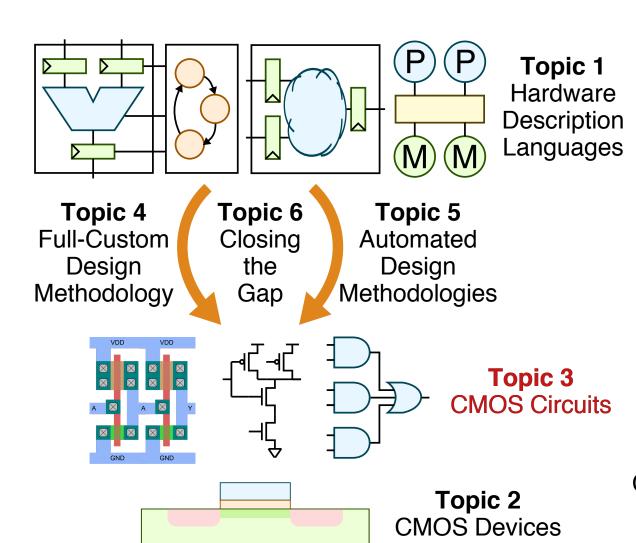

#### Part 1: ASIC Design Overview

**Topic 8**Testing and Verification

Topic 7

Clocking, Power Distribution,

Packaging, and I/O

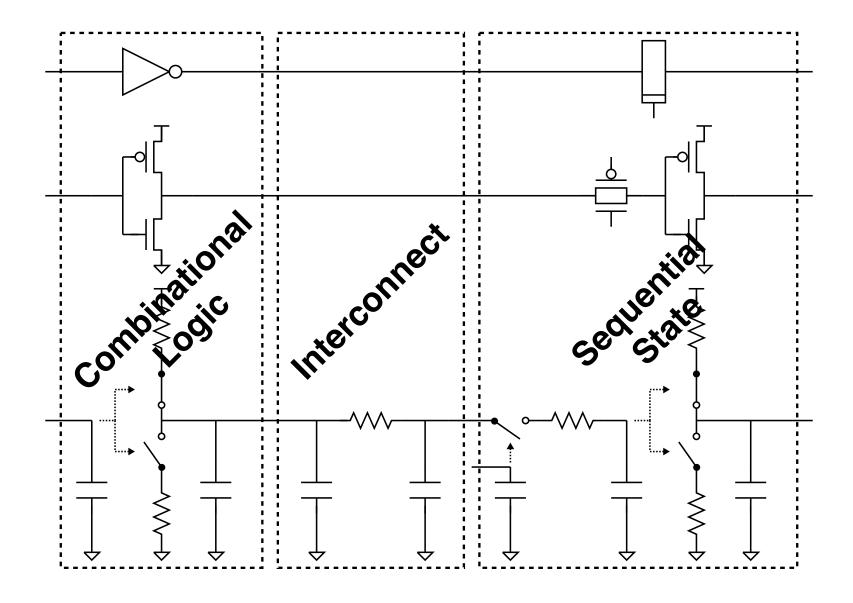

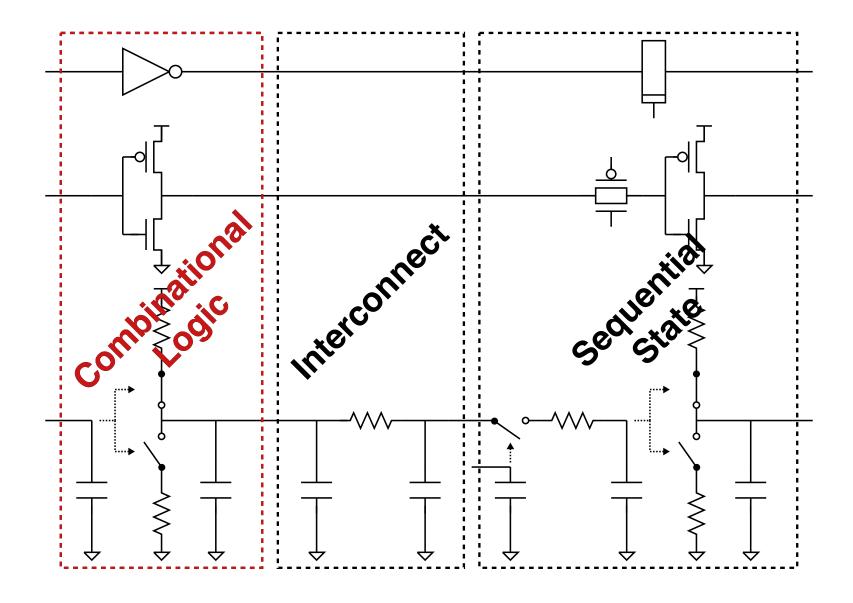

#### **CMOS Logic, State, Interconnect**

ECE 6745 T03: CMOS Circuits 3 / 28

#### **CMOS Logic, State, Interconnect**

ECE 6745 T03: CMOS Circuits 4 / 28

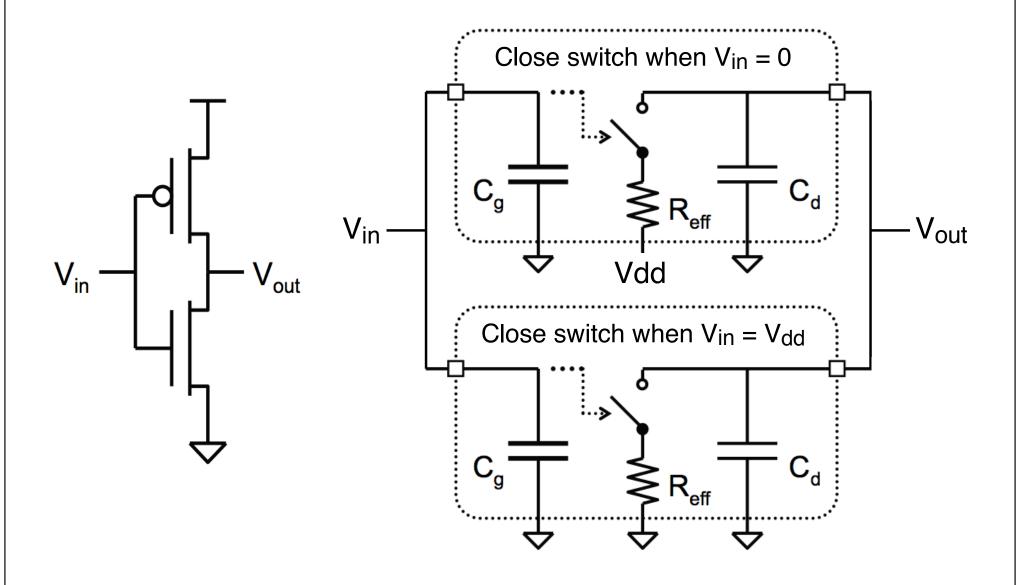

#### **CMOS Inverter Simple RC Model**

ECE 6745 T03: CMOS Circuits 5 / 28

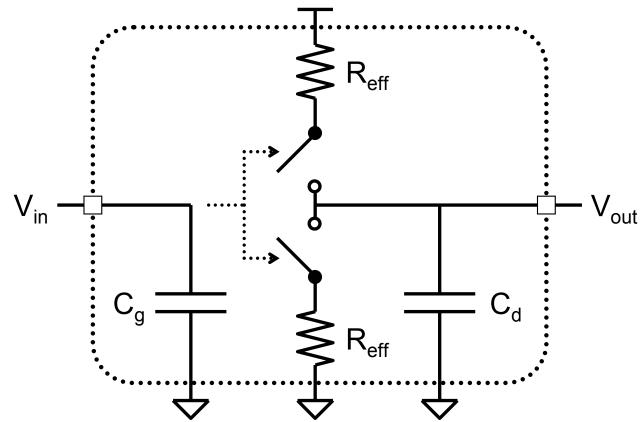

# **CMOS Inverter Simple RC Model**

$$\begin{aligned} R_{\text{eff}} &= R_{\text{eff,N}} = R_{\text{eff,P}} \\ C_{\text{g}} &= C_{\text{g,N}} + C_{\text{g,P}} \\ C_{\text{d}} &= C_{\text{d,N}} + C_{\text{d,P}} \end{aligned}$$

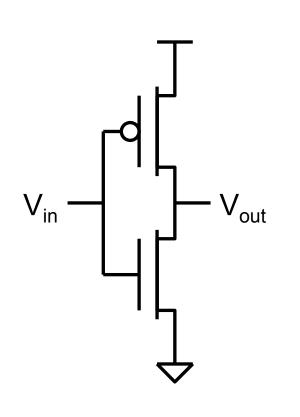

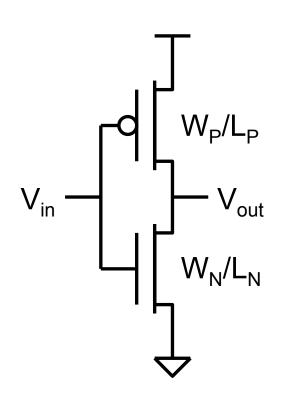

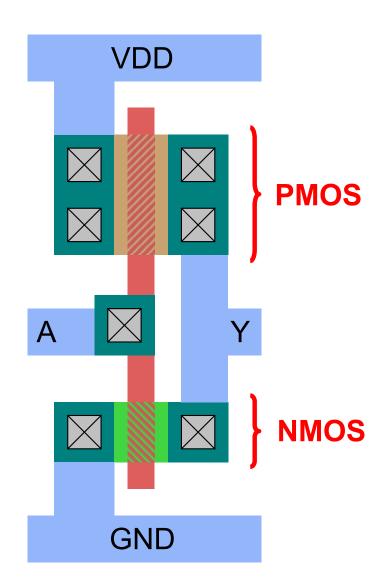

# **CMOS Inverter Layout**

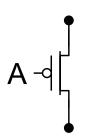

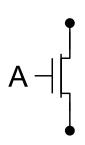

#### **CMOS Inverter**

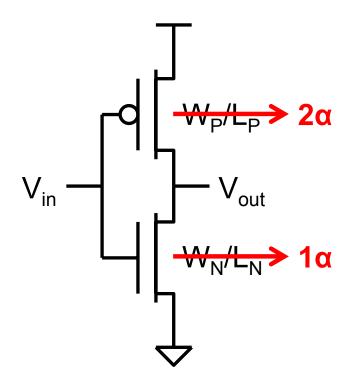

Let's make the following assumptions

- 1. All transistors are minimum length

- 2. All gates should have equal rise/fall times. Since PMOS are twice as slow as NMOS they must be twice as wide to have the same effective resistance

- 3. Normalize all transistor widths to minimum width NMOS

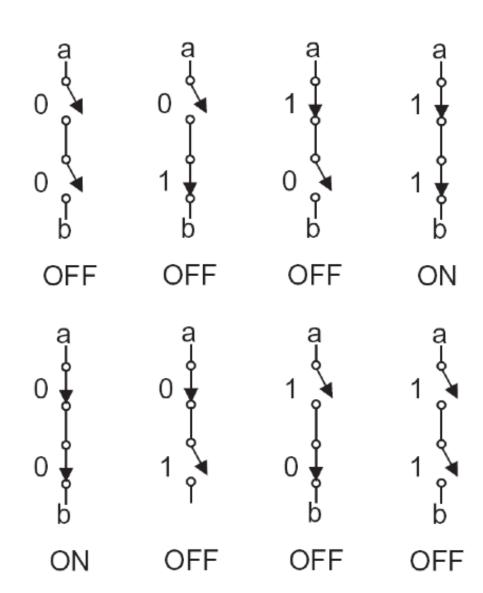

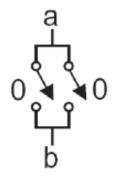

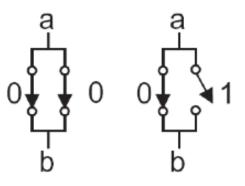

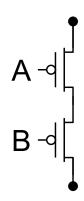

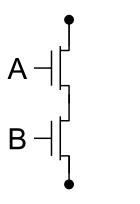

#### **Series Transistors**

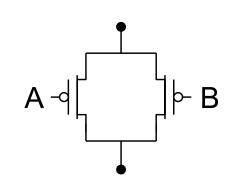

#### **Parallel Transistors**

OFF

ON

ON

ON

ON

ON

ON

**OFF**

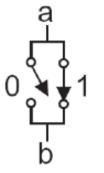

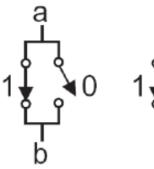

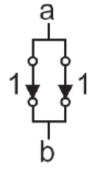

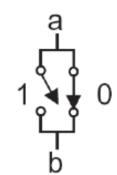

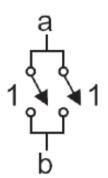

#### Series/Parallel Transistor Networks are Natural Duals

Conducts if A=0

Conducts if A=0 OR B=0

Conducts if A=0 AND B=0

Conducts if A=1

Conducts if A=1 AND B=1

Conducts if A=1 OR B=1

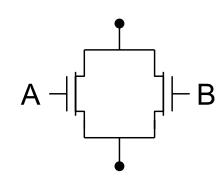

#### **CMOS Static Logic Style**

For every set of input logic values, either pullup or pulldown network makes connection to VDD or GND

- If both connected, power rails would be shorted together

- If neither connected, output would float (tristate logic)

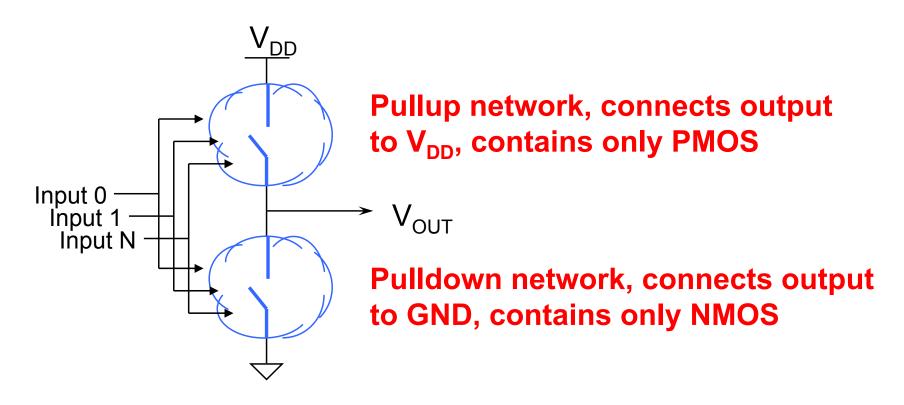

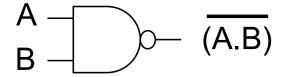

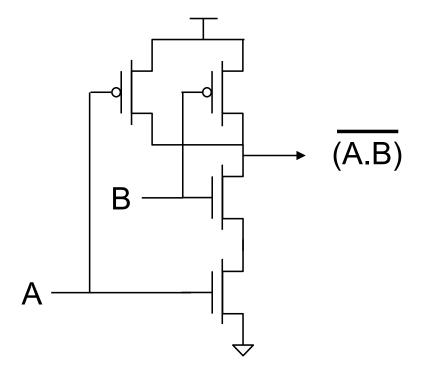

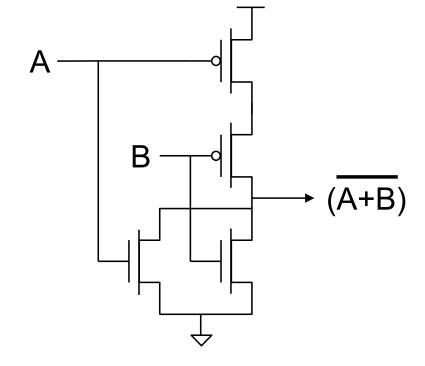

# NAND/NOR Static CMOS Logic Gates

#### **NAND** Gate

#### **NOR Gate**

$$\begin{array}{c} A \\ B \end{array} \longrightarrow (\overline{A+B})$$

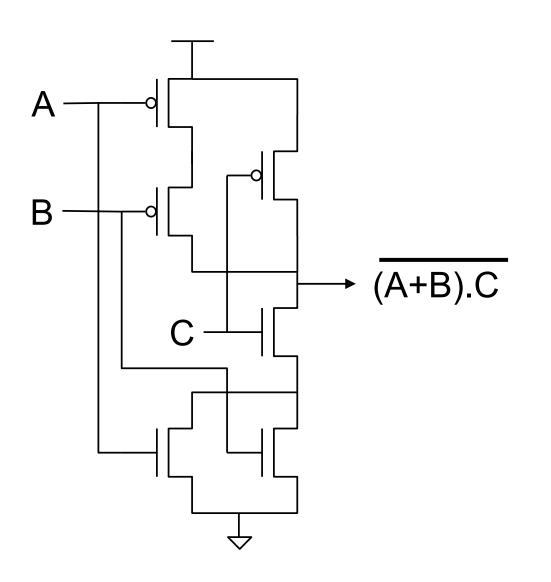

# **Approach for Designing More Complex Gates**

- ► Goal is to create a logic function  $f(x_1, x_2, ...)$

- We can only implement inverting logic with one CMOS stage

- Implement pulldown network

- $\triangleright$  Write  $PD = \overline{f(x_1, x_2, ...)}$

- Use parallel NMOS for OR of inputs

- Use series NMOS for AND of inputs

- Implement pullup network

- $ightharpoonup Write <math>PU = f(x_1, x_2, ...) = g(\overline{x_1}, \overline{x_2}, ...)$

- Use parallel PMOS for OR of inverted inputs

- Use series PMOS for AND of inverted inputs

#### **Complex Logic Gate Example**

$$f = (A + B) \cdot C$$

$$PD = (A + B) \cdot C$$

$$PU = \overline{(A + B) \cdot C}$$

$$= \overline{(A + B) + \overline{C}}$$

$$= (\overline{A} \cdot \overline{B}) + \overline{C}$$

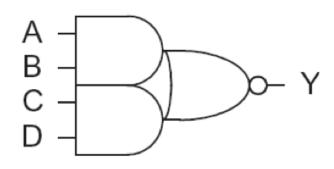

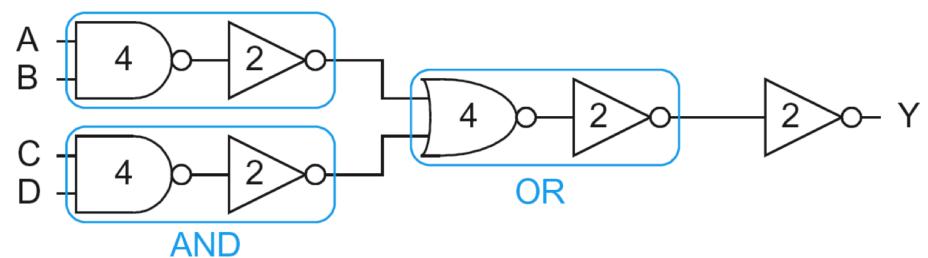

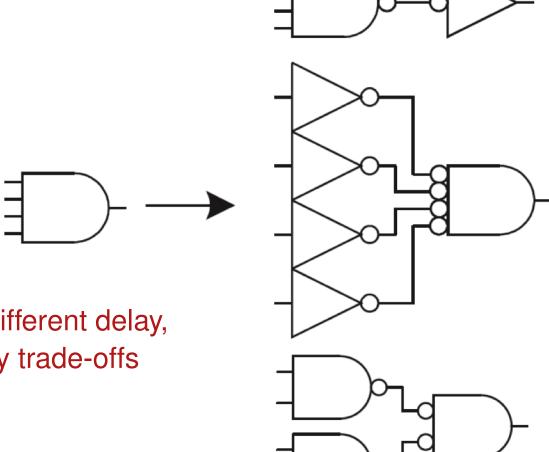

# Single- vs. Multi-Stage Static CMOS Logic

#### Multiple Stages of Static CMOS Logic

Each design has different delay, area, and energy trade-offs

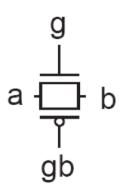

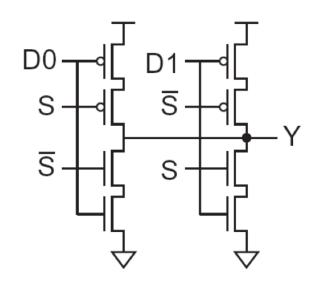

# **CMOS Pass-Transistor Logic Style**

nMOS

$$g = 0$$

$s \rightarrow -d$

$$\begin{array}{ccc}

\text{Input} & g = 1 & \text{Output} \\

0 & \longrightarrow & \text{strong 0}

\end{array}$$

pMOS

$$g = 0$$

1  $\longrightarrow$  strong 1

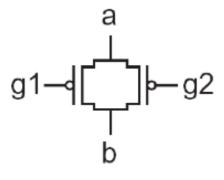

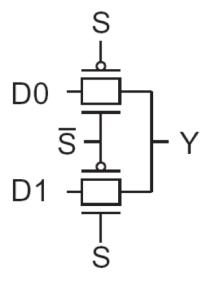

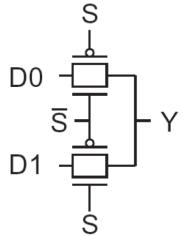

# **CMOS Transmission Gate Multiplexer**

$$g = 0$$

,  $gb = 1$

Output

$$g = 1$$

,  $gb = 0$

$0 \longrightarrow strong 0$

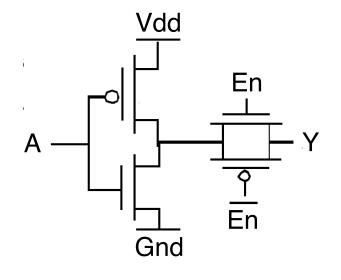

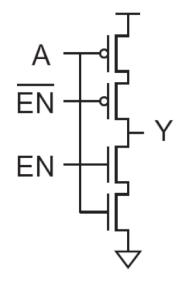

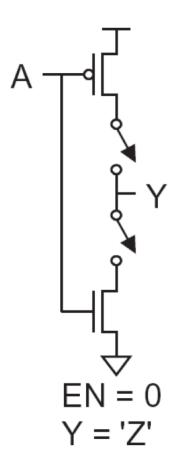

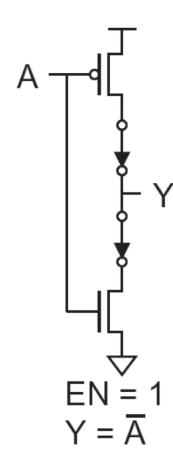

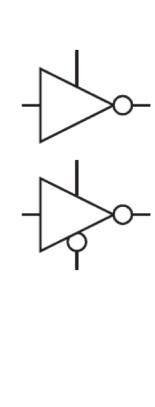

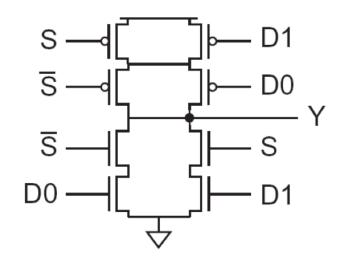

#### **CMOS Tri-State Buffers**

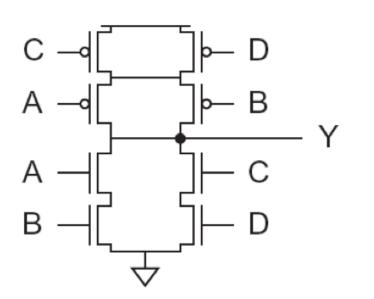

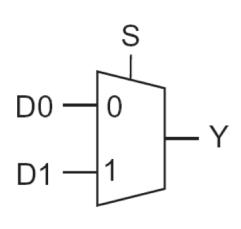

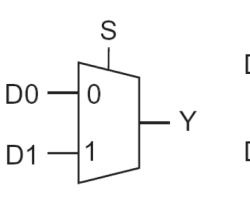

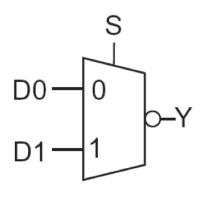

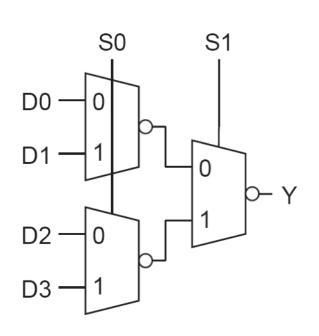

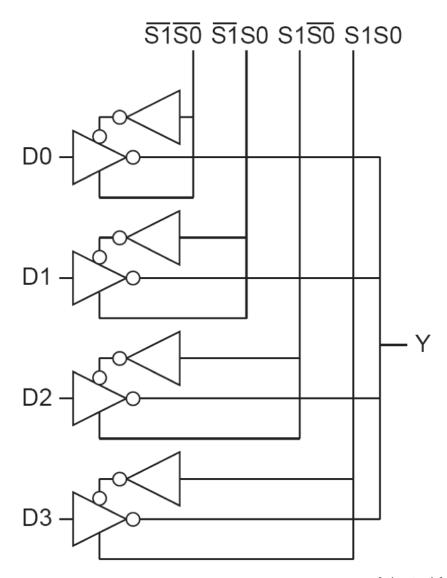

#### **Various Multiplexer Implementations**

Each design has different delay, area, and energy trade-offs

Simple first-order analysis can help suggest some of these trade-offs

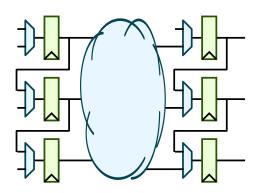

# **Larger Tri-State Multiplexers**

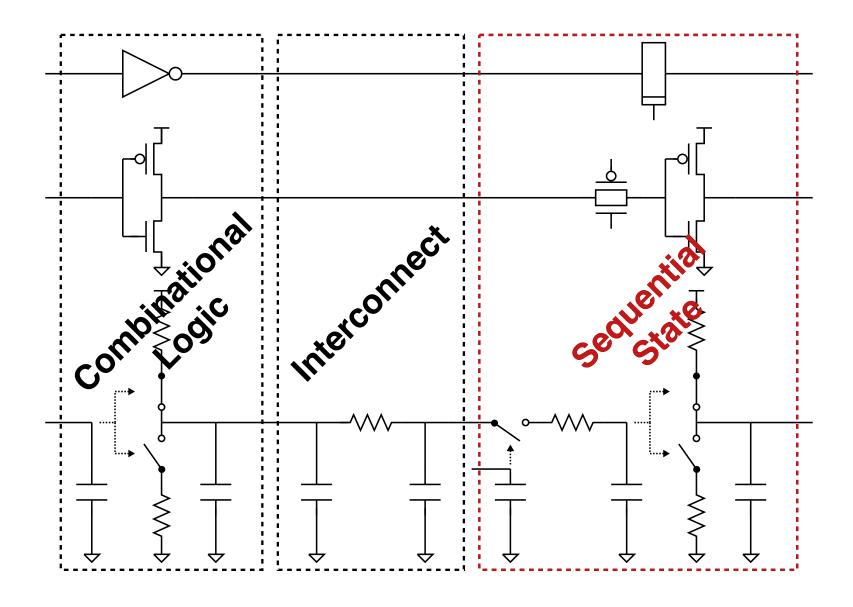

#### **CMOS Logic, State, Interconnect**

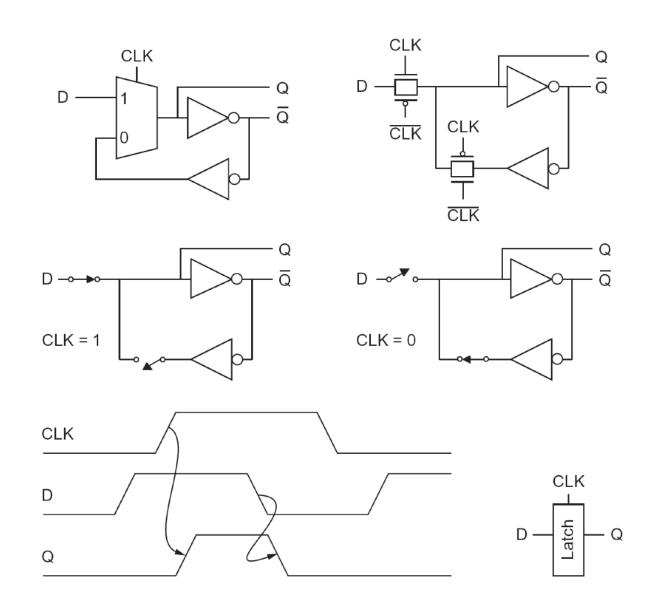

# **Level-High Latch**

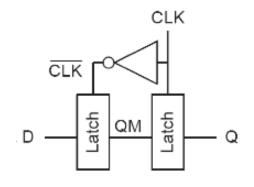

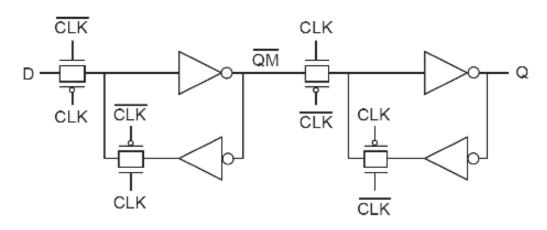

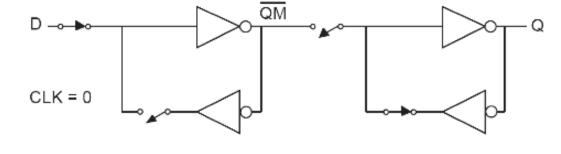

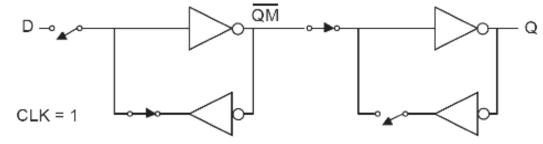

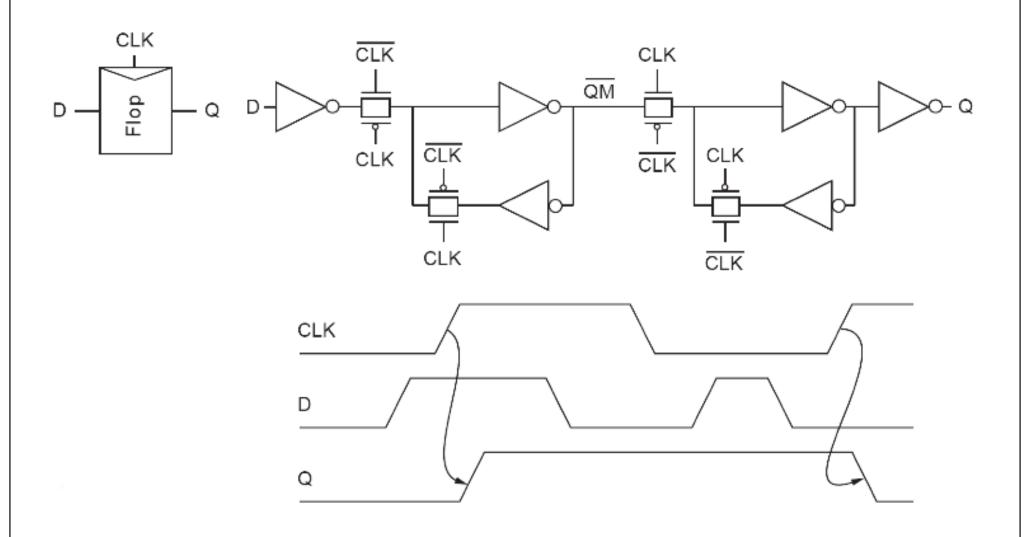

#### Positive-Edge Triggered Flip-Flop

#### Positive-Edge Triggered Flip-Flop

#### **Take-Away Points**

- We have reviewed basic CMOS circuit implementations

- Combinational Logic: static CMOS, pass-transistor, tri-state buffers

- Sequential State: latches, flip-flops

- In the next two sections, we will explore various methodologies which enable mapping designs written in a hardware-description language down into these circuits

- In the next part of the course, we will explore the details of how to quantitatively evaluate the cycle time, area, and energy of these circuits

#### **Acknowledgments**

► [Weste'11] N. Weste and D. Harris, "CMOS VLSI Design: A Circuits and Systems Perspective," 4th ed, Addison Wesley, 2011.