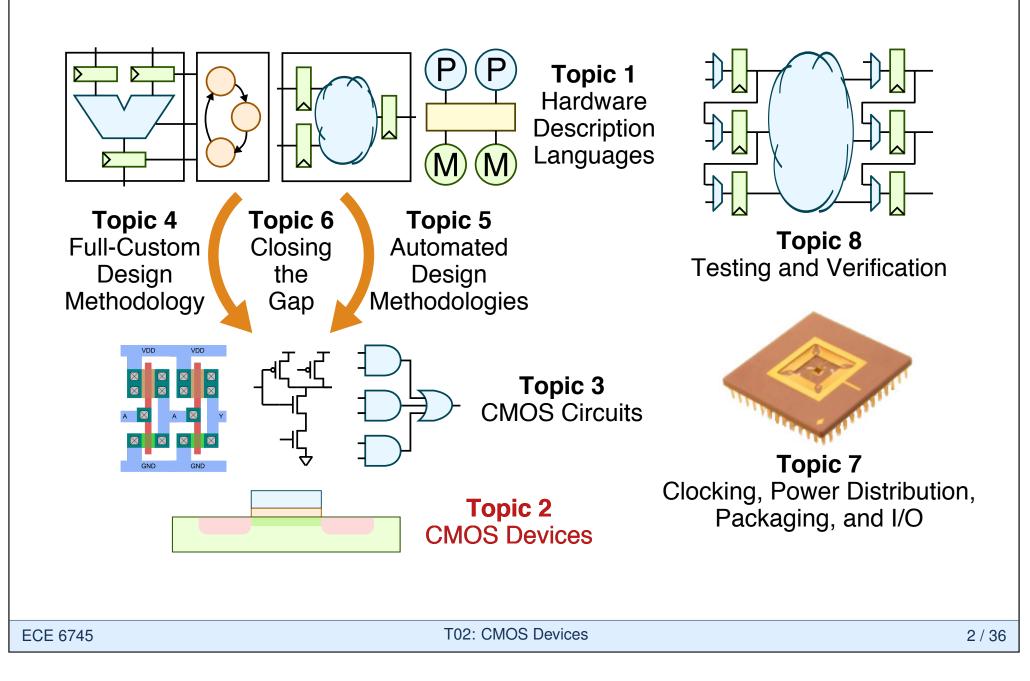

# ECE 6745 Complex Digital ASIC Design Topic 2: CMOS Devices

**Christopher Batten**

School of Electrical and Computer Engineering Cornell University

http://www.csl.cornell.edu/courses/ece6745

Simple Wire RC Model

**MOSFET Fabrication**

#### Part 1: ASIC Design Overview

| Simple Transistor RC Model | Simple Wire RC Model | MOSFET Fabrication |

|----------------------------|----------------------|--------------------|

|                            | Agenda               |                    |

|                            |                      |                    |

|                            |                      |                    |

| Simple Transistor          | RC Model             |                    |

|                            |                      |                    |

| Simple Wire RC N           | /lodel               |                    |

|                            |                      |                    |

| CMOS Fabrication           | า                    |                    |

|                            |                      |                    |

**MOSFET** Fabrication

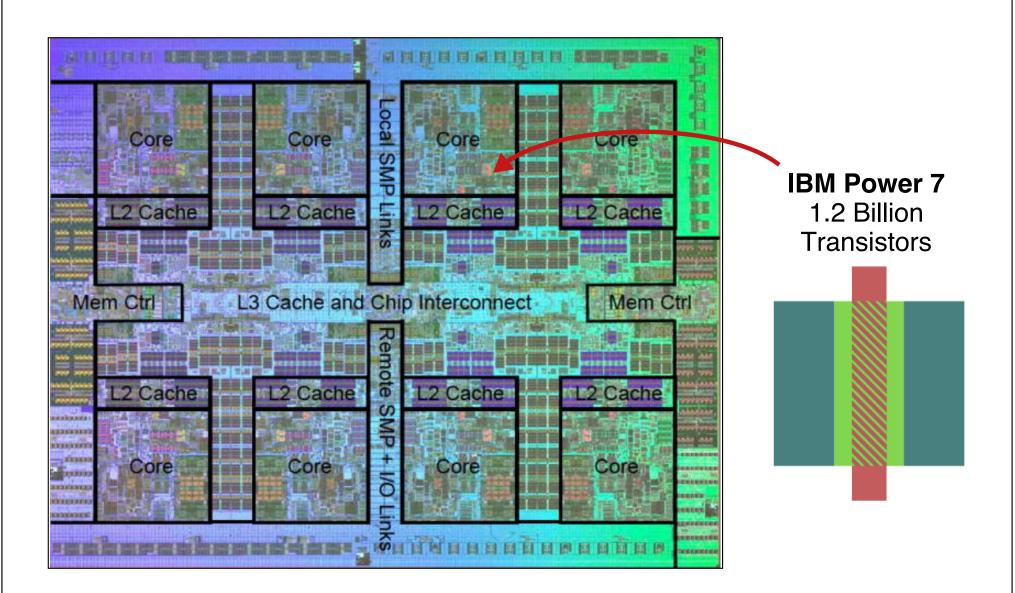

#### **Fundamental Building Block: MOSFET Transistor**

**MOSFET** Fabrication

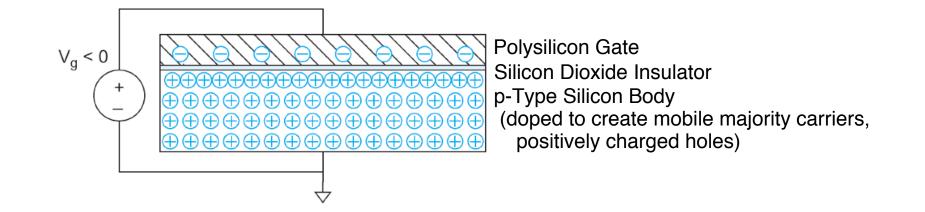

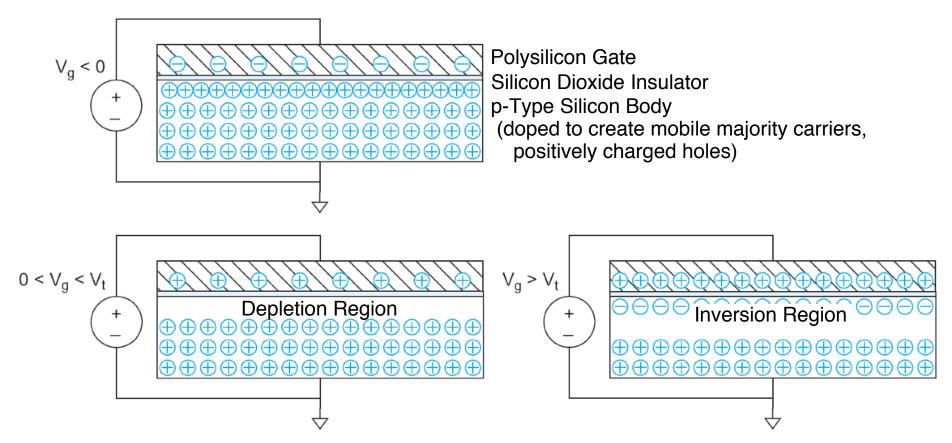

#### "Metal"-Oxide-Semiconductor Structure

#### Accumulation: Battery puts negative charge on gate, attracts positively-charged majority carriers in p-type silicon body

**MOSFET Fabrication**

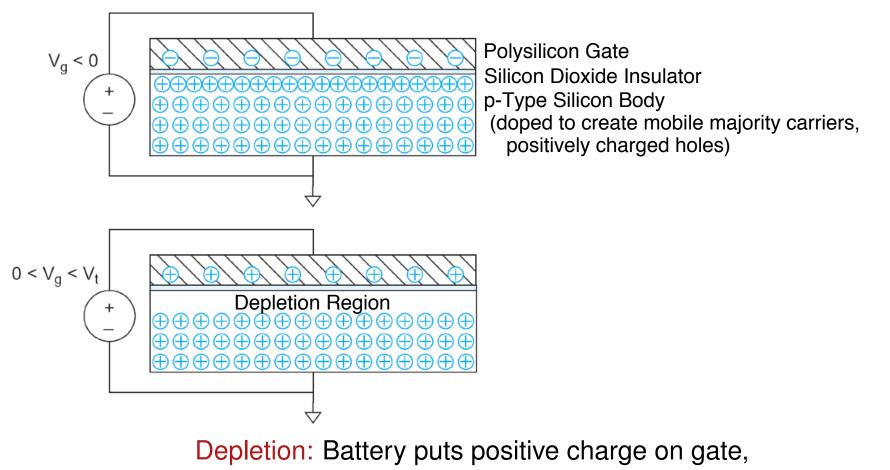

#### "Metal"-Oxide-Semiconductor Structure

pushes positively-charged carriers away from surface, uncovers some negatively-charged dopant atoms in substrate

**MOSFET Fabrication**

#### "Metal"-Oxide-Semiconductor Structure

Inversion: Battery puts more positive charge on gate, instead of pushing holes even further away, draws free electrons to surface. Where did electrons come from? No electron donors in p-type silicon; electron/hole pairs always being generated by thermal excitation – electrons caught by efield in depletion region Adapted from [Weste'11]

**MOSFET** Fabrication

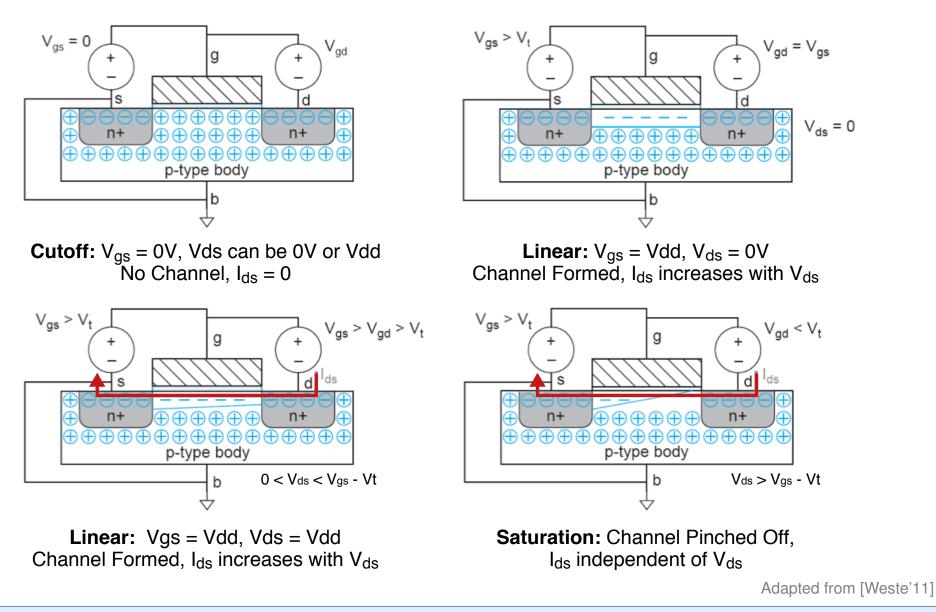

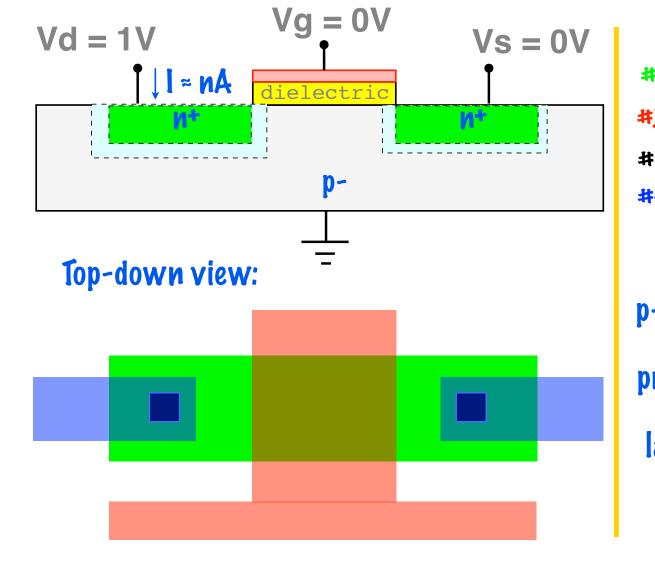

#### **NMOS Transistor**

**MOSFET Fabrication**

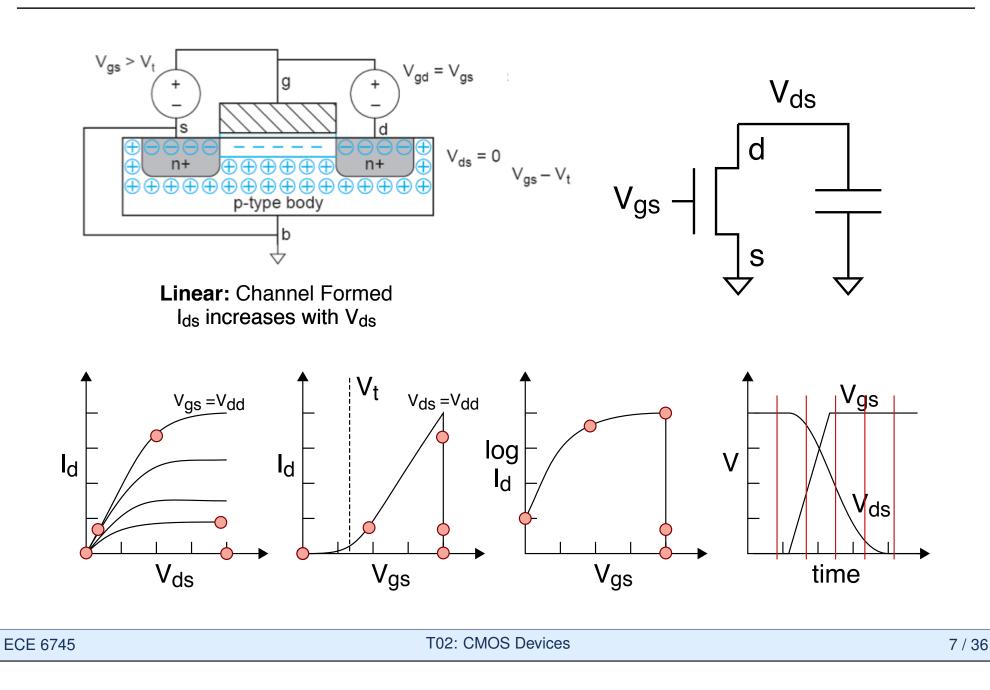

#### Simple NMOS Circuit

**MOSFET Fabrication**

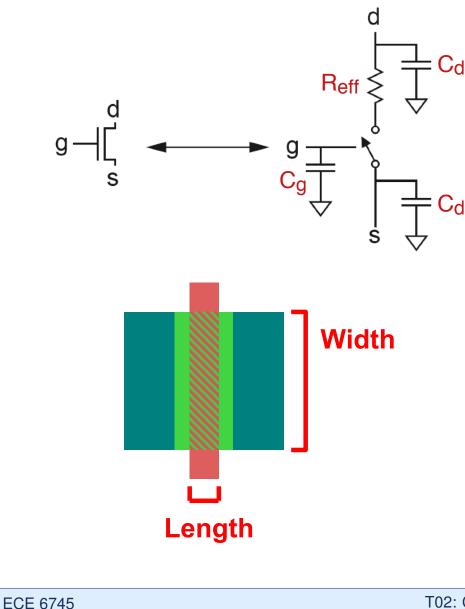

#### **Key Qualitative Characteristics of MOSFET Transistors**

- V<sub>t</sub> sets when transistor turns on, impacts leakage current

- $\blacktriangleright I_d \propto \mu \times (W/L)$

- $\blacktriangleright \ \mu_n > \mu_p \implies R_{N,eff} < R_{P,eff}$

- $\blacktriangleright C_g \propto (W \times L)$

- $\blacktriangleright$   $C_d \propto W$

- $\uparrow W = \downarrow R_{eff} = \uparrow I_d = \uparrow \\ C_d, C_g$

- $\blacktriangleright \uparrow L = \uparrow R_{eff} = \downarrow I_d = \uparrow C_g$

| Simple Transistor RC Model | Simple Wire RC Model   · | MOSFET Fabrication |

|----------------------------|--------------------------|--------------------|

|                            | Agenda                   |                    |

| Simple Transistor          | RC Model                 |                    |

| Simple Wire RC N           | /lodel                   |                    |

| CMOS Fabrication           | 1                        |                    |

Simple Wire RC Model •

**MOSFET** Fabrication

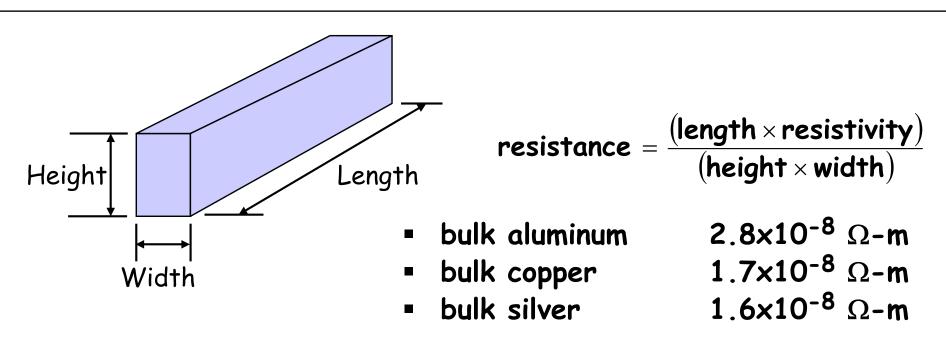

#### Wire Resistance

- Thickness fixed in given manufacturing process

- Resistances quoted as  $\Omega$ /square

- TSMC 0.18μm 6 Aluminum metal layers

M1-5 0.08 Ω/square (0.5 μm × 1mm wire = 160 Ω)

M6 0.03 Ω/square (0.5 μm × 1mm wire = 60 Ω)

$R_{sq}$  = resistivity / height resistance =  $R_{sq}$  × (length / width) Adapted from [Terman'02]

ECE 6745

**MOSFET Fabrication**

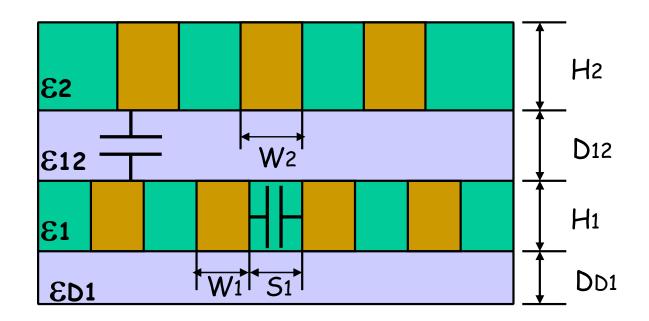

#### **Wire Capacitance**

- Capacitance depends on geometry of surrounding wires and relative permittivity, E<sub>r</sub>, of dielectric

- silicon dioxide,  $SiO_2 \varepsilon_r = 3.9$

- silicon flouride, SiOF  $\varepsilon_r = 3.1$

- SiLK<sup>TM</sup> polymer,  $\varepsilon_r = 2.6$

Adapted from [Terman'02]

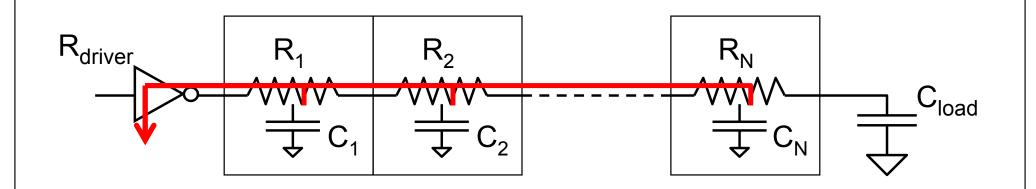

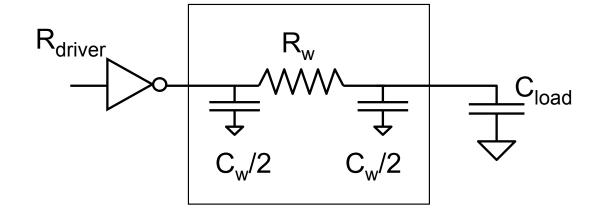

#### **Key Qualitative Characteristics of Wires**

Because both wire resistance and wire capacitance increase with length, wire delay grows quadratically with length

| Simple Transistor RC Model | Simple Wire RC Model | MOSFET Fabrication • |

|----------------------------|----------------------|----------------------|

|                            | Agenda               |                      |

|                            |                      |                      |

|                            |                      |                      |

| Simple Transistor F        | RC Model             |                      |

|                            |                      |                      |

| Simple Wire RC Mo          | odel                 |                      |

|                            |                      |                      |

| CMOS Fabrication           |                      |                      |

|                            |                      |                      |

|                            |                      |                      |

MOSFET Fabrication •

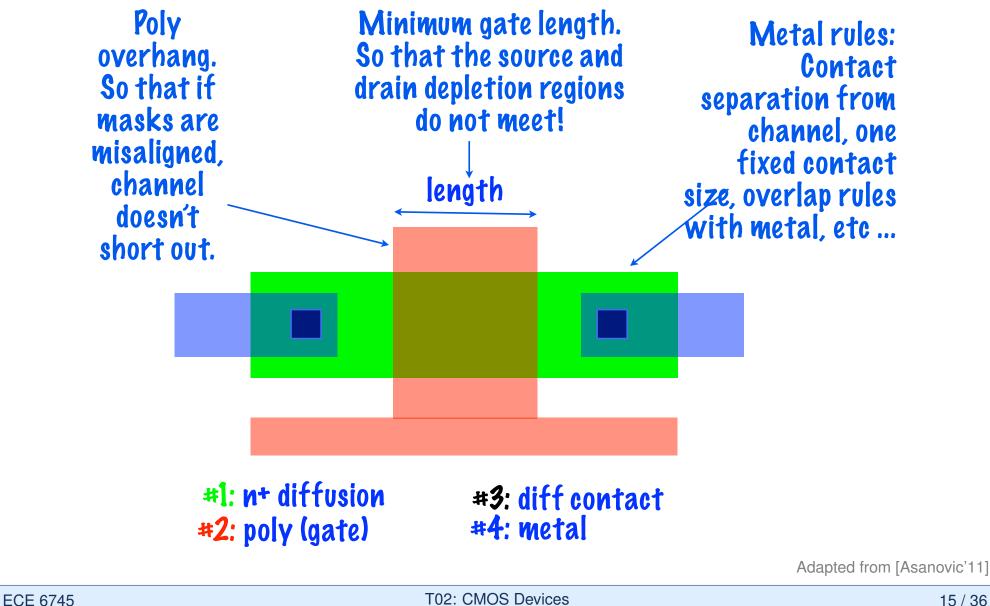

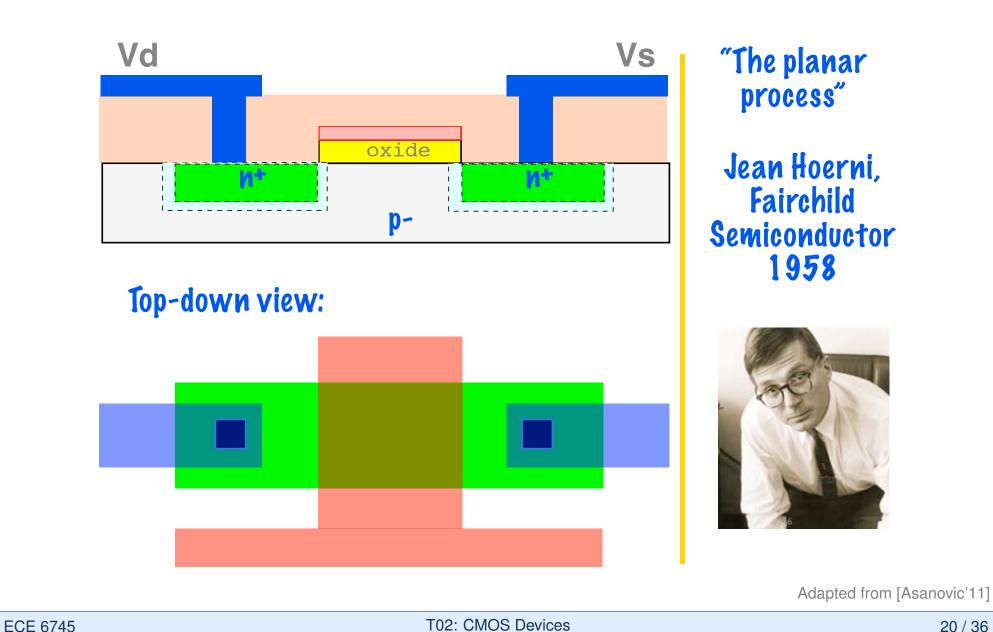

#### Mask Set for NMOS Transistor (circa 1986)

Masks #1: n+ diffusion #2: poly (gate) #3: diff contact #4: metal

Layers to do p-Fet not shown. Modern processes have 6 to 10 metal layers (or more) (in 1,986: 2).

Adapted from [Asanovic'11]

MOSFET Fabrication •

#### **Design Rules for Masks (circa 1986)**

Simple Wire RC Model

MOSFET Fabrication •

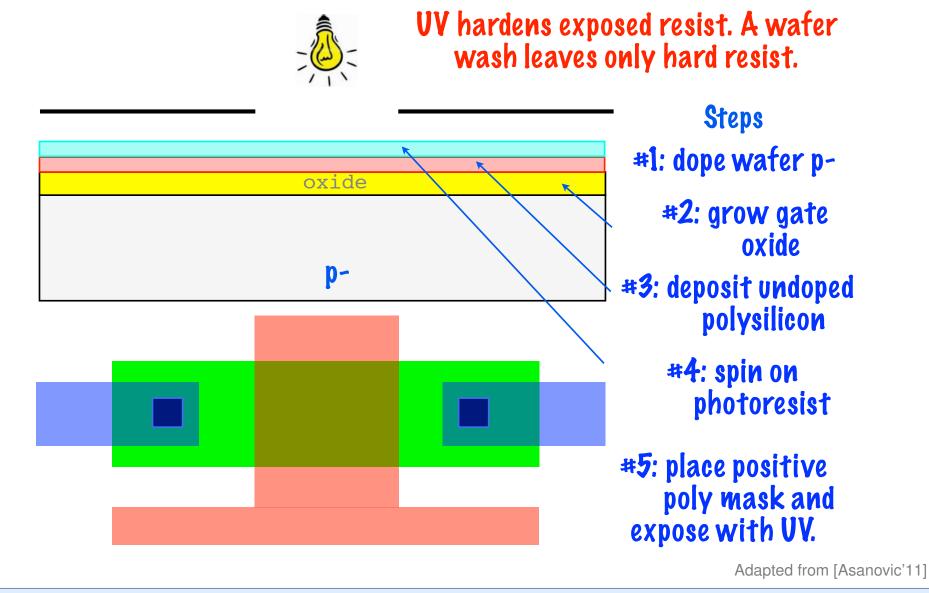

#### **Start With an Un-Doped Wafer**

Simple Wire RC Model

MOSFET Fabrication •

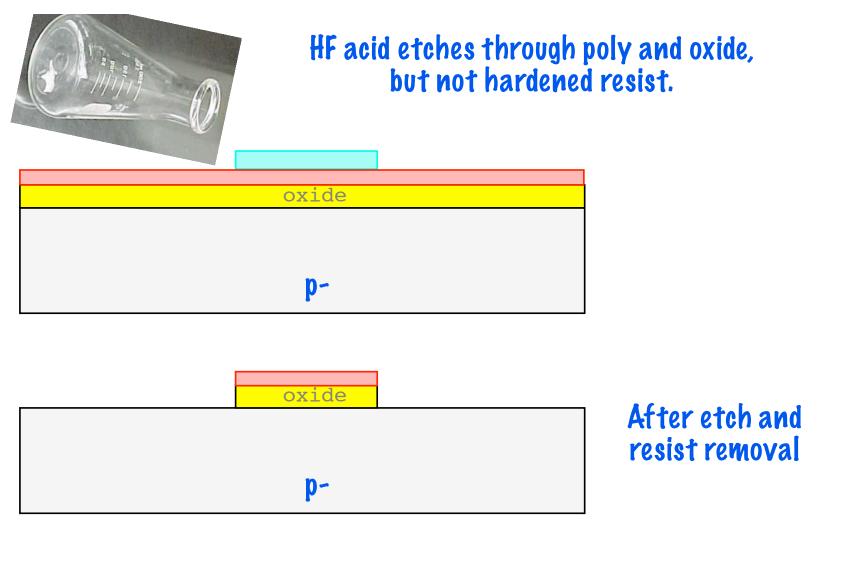

#### Wet Etch to Remove Unmasked Regions

Adapted from [Asanovic'11]

MOSFET Fabrication •

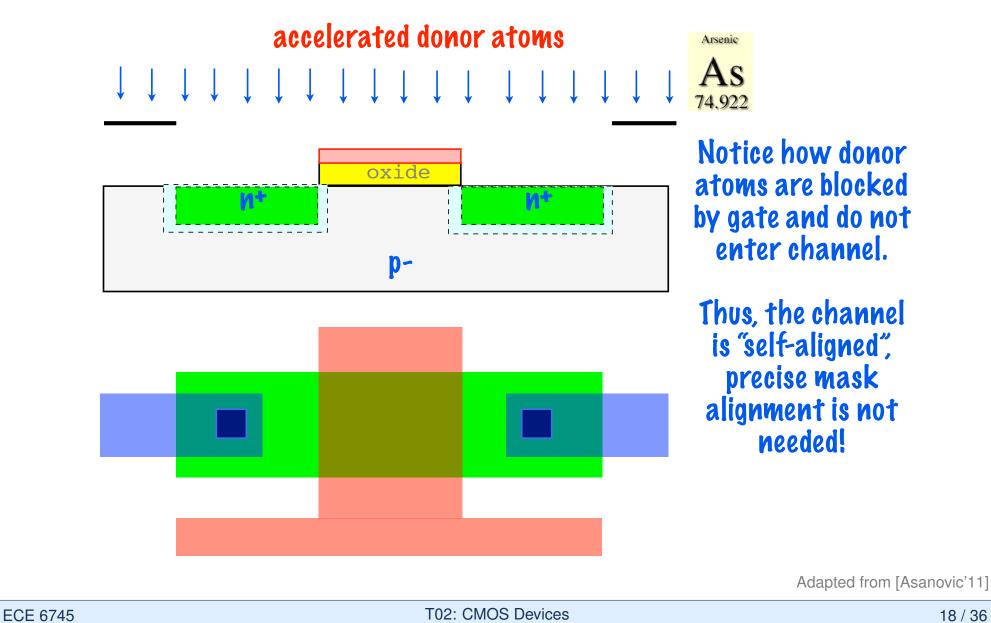

#### **Use Diffusion Mask to Implant N-Type**

Simple Wire RC Model

MOSFET Fabrication •

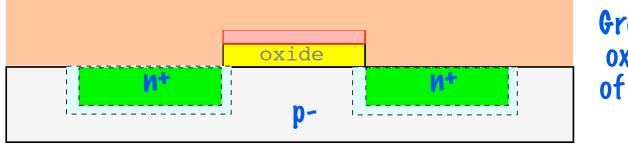

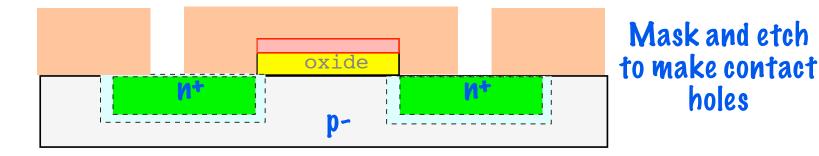

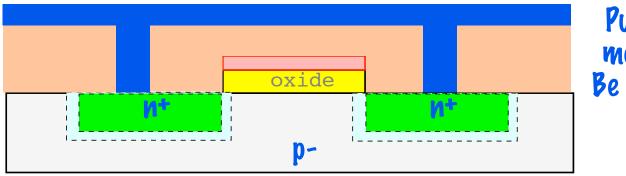

#### **Metallization Completes Device**

Grow a thick oxide on top of the wafer.

Put a layer of metal on chip. Be sure to fill in the holes!

Adapted from [Asanovic'11]

MOSFET Fabrication •

## **Final NMOS Transistor**

MOSFET Fabrication •

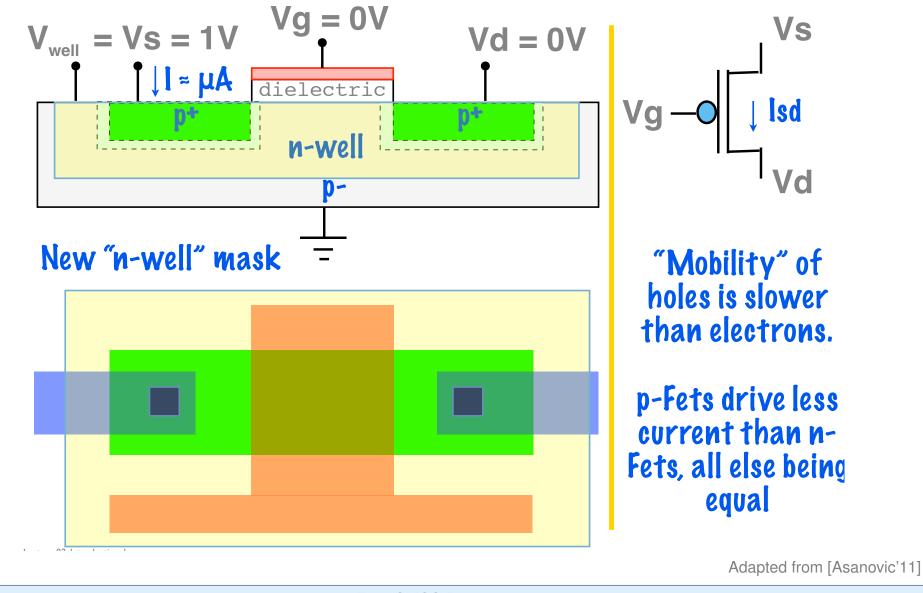

#### **PMOS Transistor is Dual of NMOS Transistor**

ECE 6745

MOSFET Fabrication •

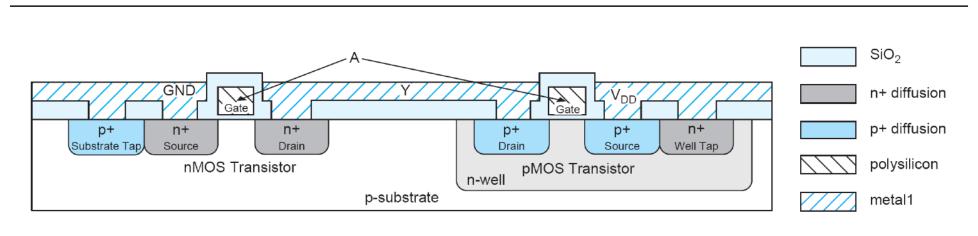

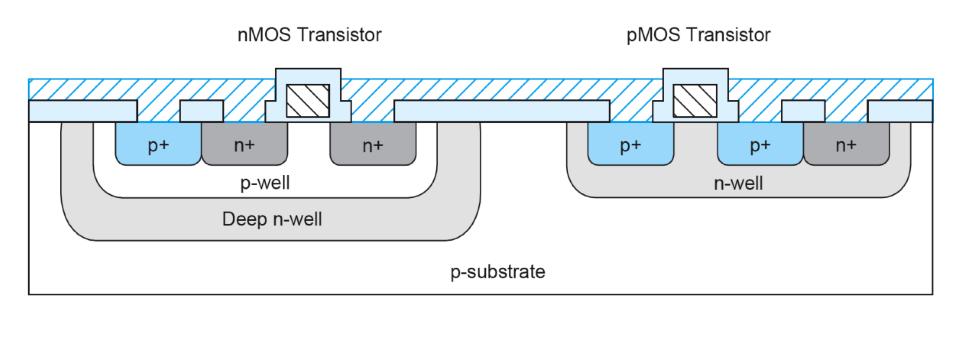

#### Single- and Triple-Well Processes

MOSFET Fabrication •

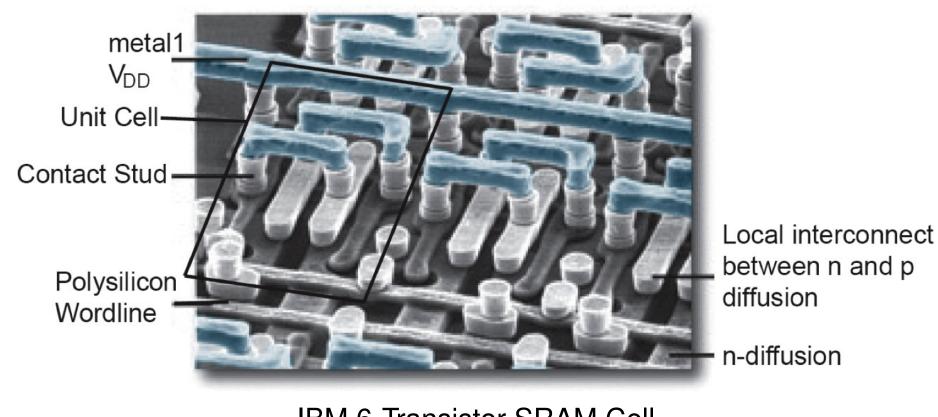

#### **Local Interconnect**

IBM 6-Transistor SRAM Cell

Simple Wire RC Model

MOSFET Fabrication •

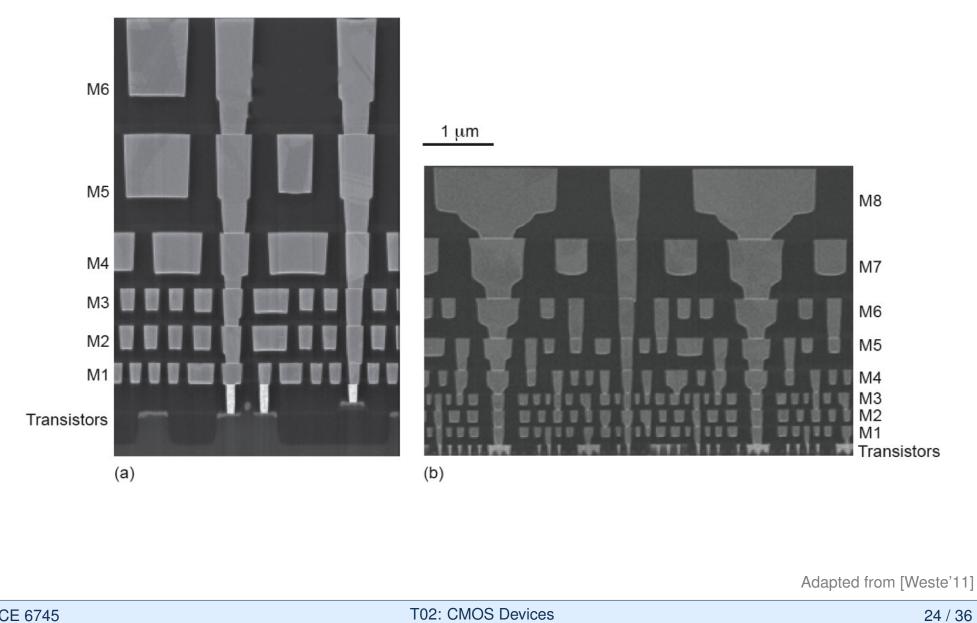

#### Intel Metal Stacks: 90nm and 45nm

MOSFET Fabrication •

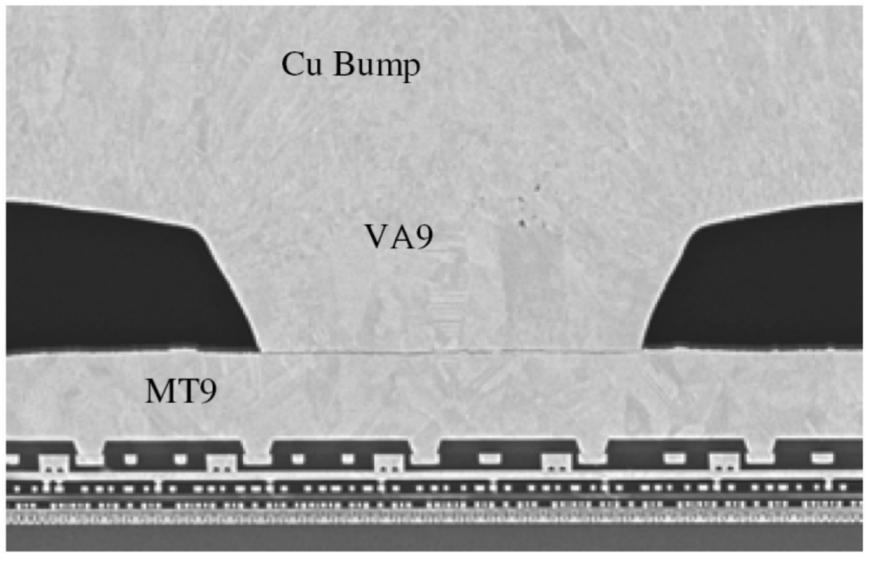

#### Intel Metal Stacks: 45nm with M9 and I/O Bump

#### Intel Metal Layer Dimensions in 45nm

| Layer     | t (nm) | w (nm) | s (nm) | pitch (nm) |

|-----------|--------|--------|--------|------------|

| M9        | 7µm    | 17.5µm | 13µm   | 30.5µm     |

| <b>M8</b> | 720    | 400    | 410    | 810        |

| M7        | 504    | 280    | 280    | 560        |

| M6        | 324    | 180    | 180    | 360        |

| M5        | 252    | 140    | 140    | 280        |

| M4        | 216    | 120    | 120    | 240        |

| M3        | 144    | 80     | 80     | 160        |

| M2        | 144    | 80     | 80     | 160        |

| M1        | 144    | 80     | 80     | 160        |

Simple Wire RC Model

MOSFET Fabrication •

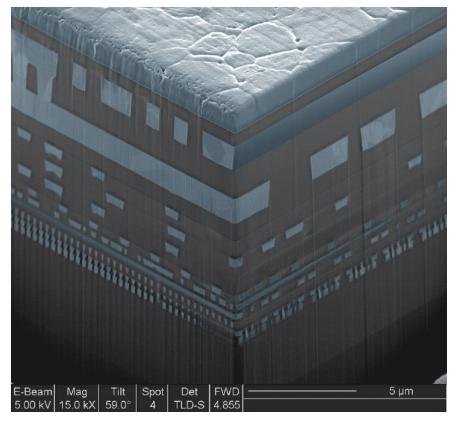

#### **IBM Metal Stacks**

IBM 11-layer Copper Metal Stack

IBM 6-layer Copper Metal Stack

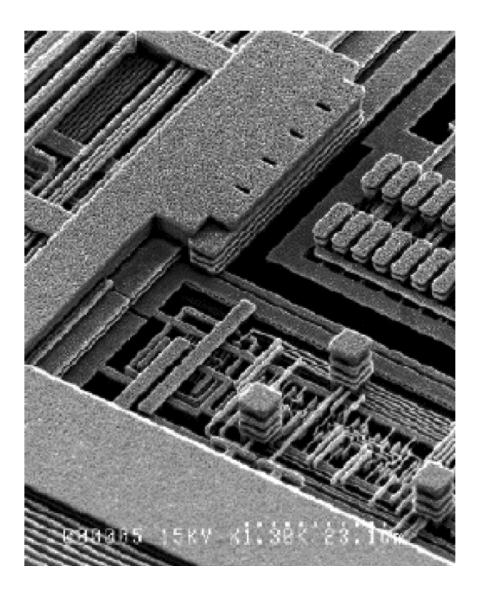

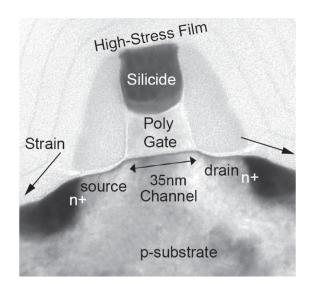

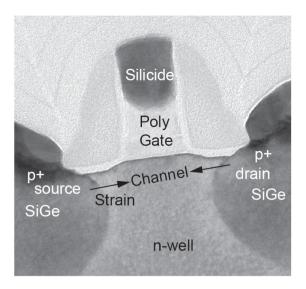

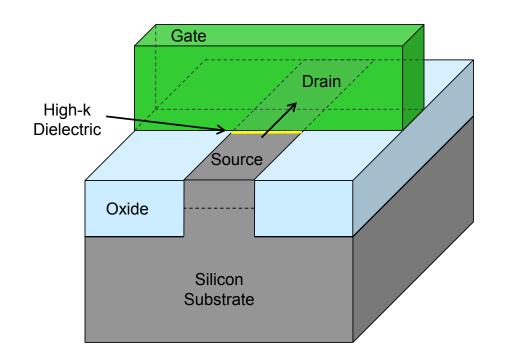

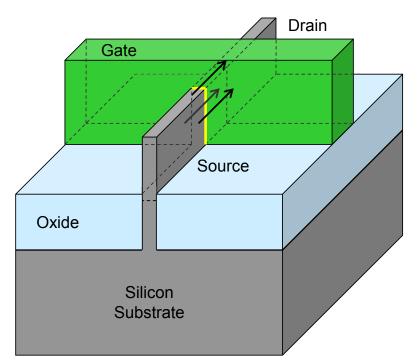

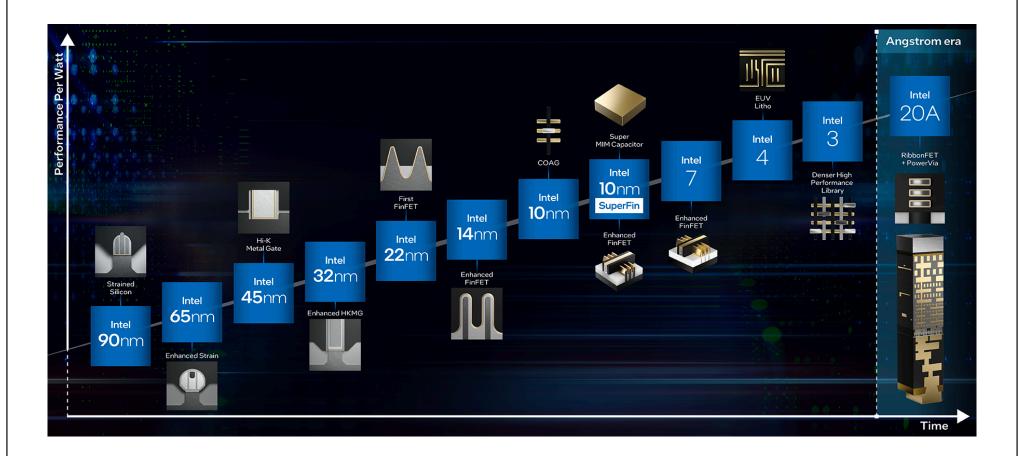

#### **Process Enhancements**

- High-K Dieletrics and Metal Gates Replacing silicon dioxide gate dielectric with a high-K material allows increased vertical electric field without increasing gate leakage

- Strained Silicon Layer of silicon in which silicon atoms are stretched beyond their normal interatomic distance leading to better mobility

- Gate Engineering Multiple transistor designs with different threshold voltages to allow optimization of delay or power

Adapted from [Asanovic'11,Weste'11]

MOSFET Fabrication •

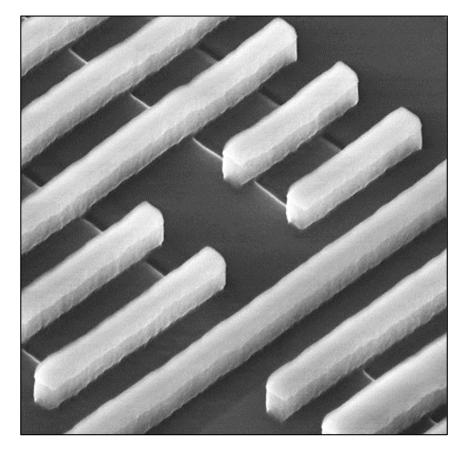

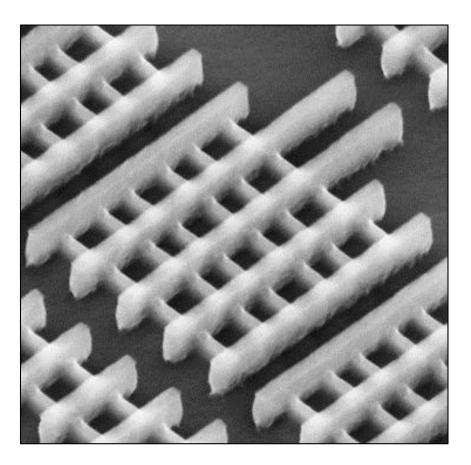

#### **FinFET Transistors**

2D planar transistors form a conducting channel in silicon region under the gate electrode

3D tri-gate transistors form conducting channels on three sides of a vertical fin structure

MOSFET Fabrication •

#### **FinFET Transistors**

#### 32 nm Planar Transistors 22 nm Tri-Gate Transistors

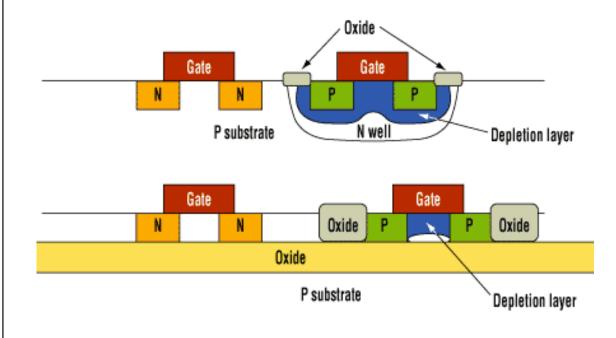

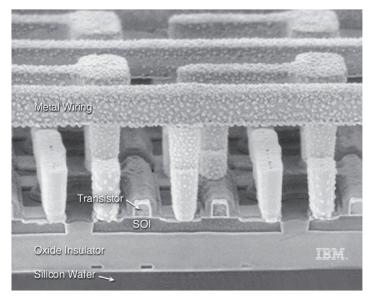

## Bulk vs. Silicon-on-Insulator Processing

- Eliminates parasitic capacitance between source/drain and the body  $\rightarrow$  lower energy, higher performance

- Lower subthreshold leakage, but threshold voltage varies over time

- 10–15% increase in total manufacturing cost due to substrate cost

Adapted from [Asanovic'11,Weste'11]

Simple Wire RC Model

MOSFET Fabrication •

Mask

OPC

0 Z

OPC

Mask overlaid

with micrograph

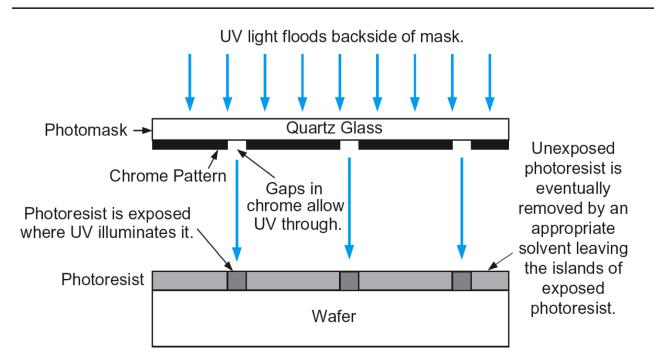

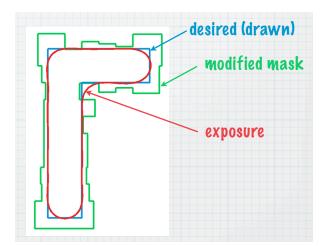

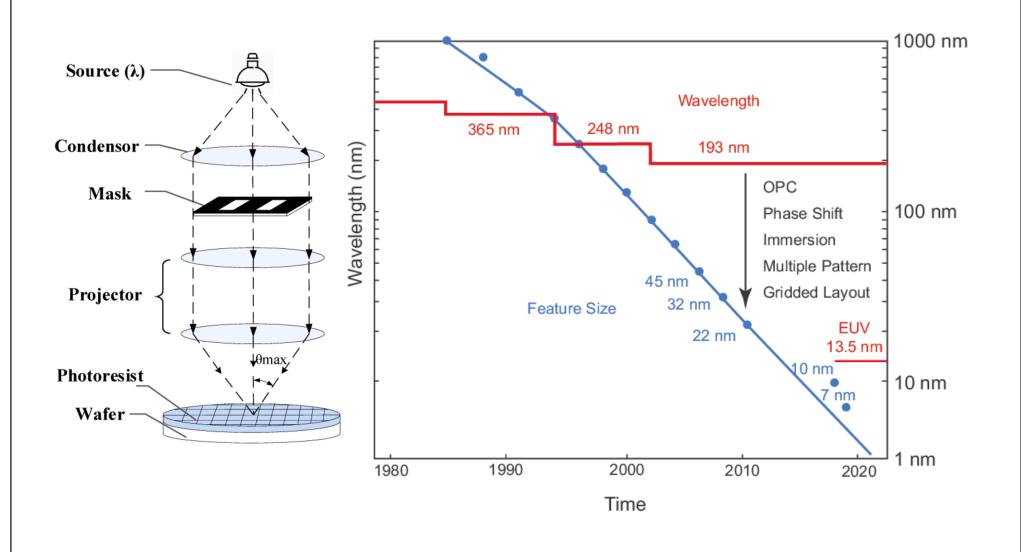

### Lithography

- Resolution of patterns far exceeds wavelength of light used for exposure which is usually 193 nm generated with an argon fluoride laser

- Sophisticated tricks used to pattern 10–100 µm features including immersion lithography, optical proximity correction, double patterning

Adapted from [Asanovic'11,Weste'11]

Ъ

Ň

Simple Wire RC Model

MOSFET Fabrication •

#### Extreme Ultraviolet Lithography

MOSFET Fabrication •

#### **Technology Scaling via Process Enhancements**

#### **Take-Away Points**

- Although a basic understanding of devices and fabrication is important for understanding technology constraints, mostly in this course we will focus on first-order RC models of CMOS logic, state, and interconnect

- In the next topic of this part of the course, we will briefly introduce CMOS circuits using these devices

- Combinational Logic: static CMOS, pass-transistor, tri-state buffers

- Sequential State: latches, flip-flops

- In the next part of the course, we will explore the details of how to quantitatively evaluate the cycle time, area, and energy of these digital circuits

#### Acknowledgments

- [Weste'11] N. Weste and D. Harris, "CMOS VLSI Design: A Circuits and Systems Perspective," 4th ed, Addison Wesley, 2011.

- [Terman'02] C. Terman and K. Asanović, "CMOS Technology," and "Wires, "MIT 6.371 Introduction to VLSI Systems, Lectures, 2002.

- [Asanovic'11] K. Asanović, J. Wawrzynek, and J. Lazzaro, "Introduction," UC Berkeley CS 250 VLSI Systems Design, Lecture, 2011.