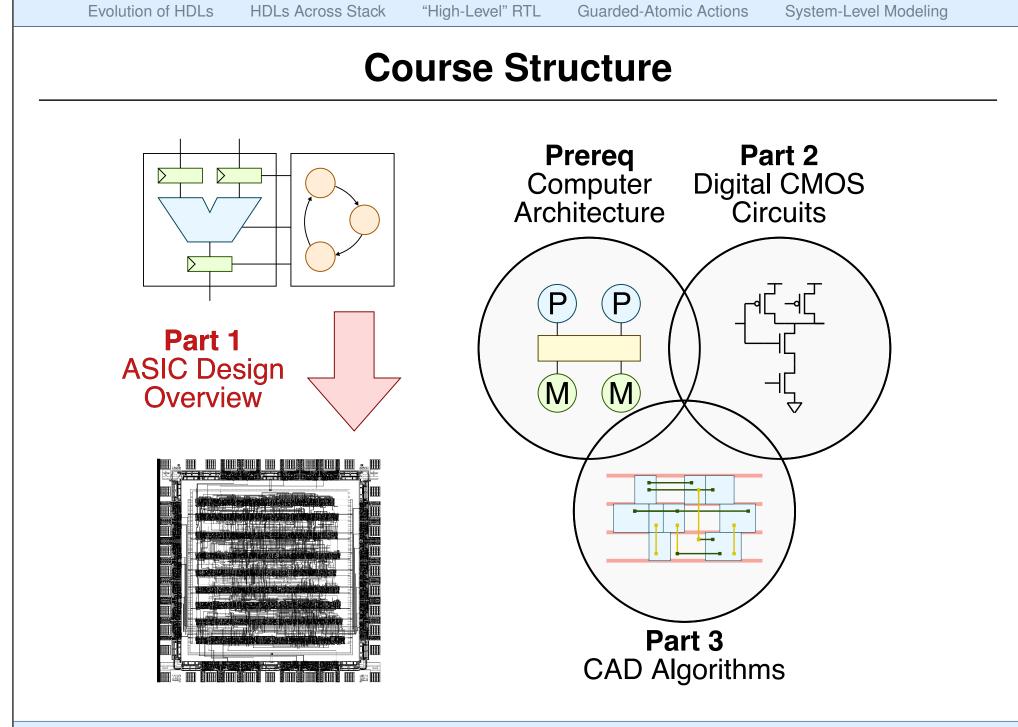

## ECE 6745 Complex Digital ASIC Design Topic 1: Hardware Description Languages

#### Christopher Batten

School of Electrical and Computer Engineering Cornell University

http://www.csl.cornell.edu/courses/ece6745

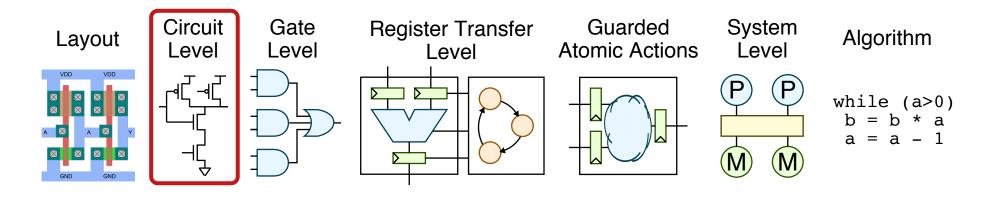

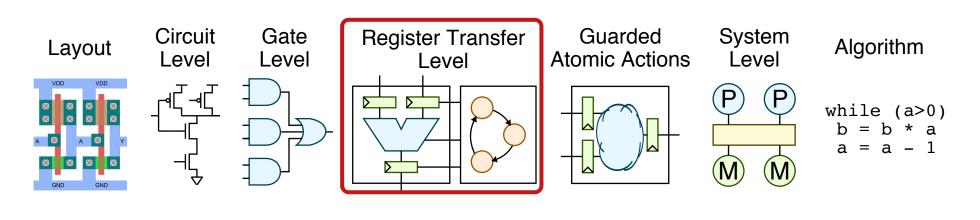

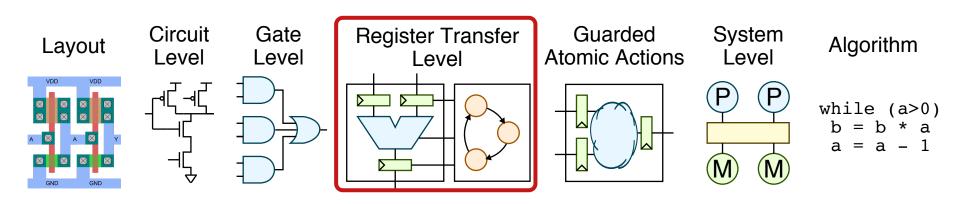

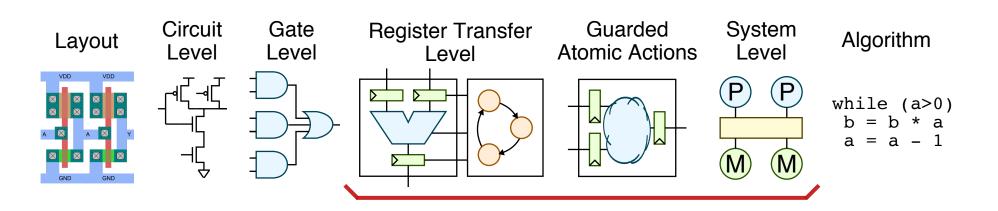

Evolution of HDLs HDLs Across Stack "High-Level" RTL Guarded-Atomic Actions System-Level Modeling

#### Part 1: ASIC Design Overview

#### Agenda

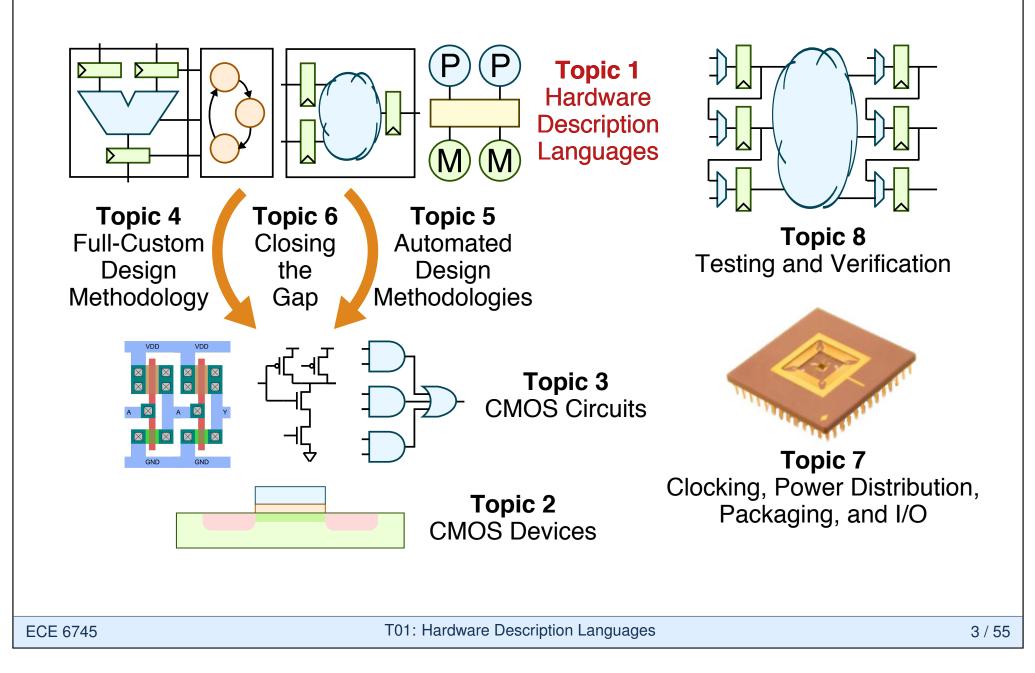

Evolution of Hardware Description Languages

Hardware Description Languages Across Stack

"High-Level" RTL with SystemVerilog

Guarded-Atomic Actions with Bluespec

System-Level Modeling with SystemC

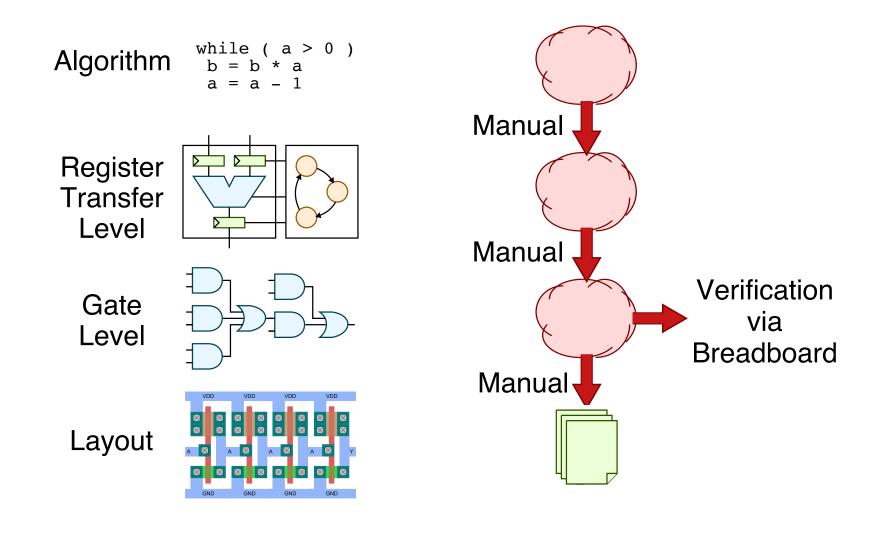

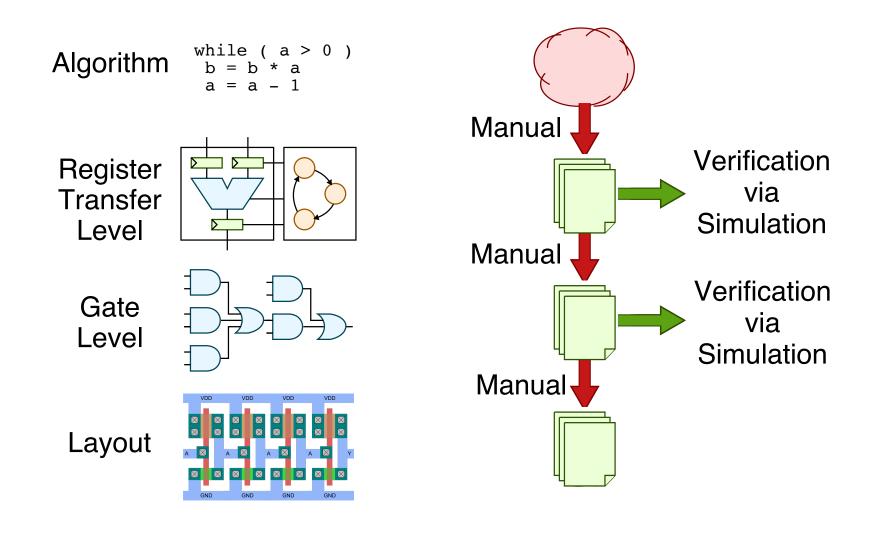

## Originally designers used manual translation and breadboards for verification

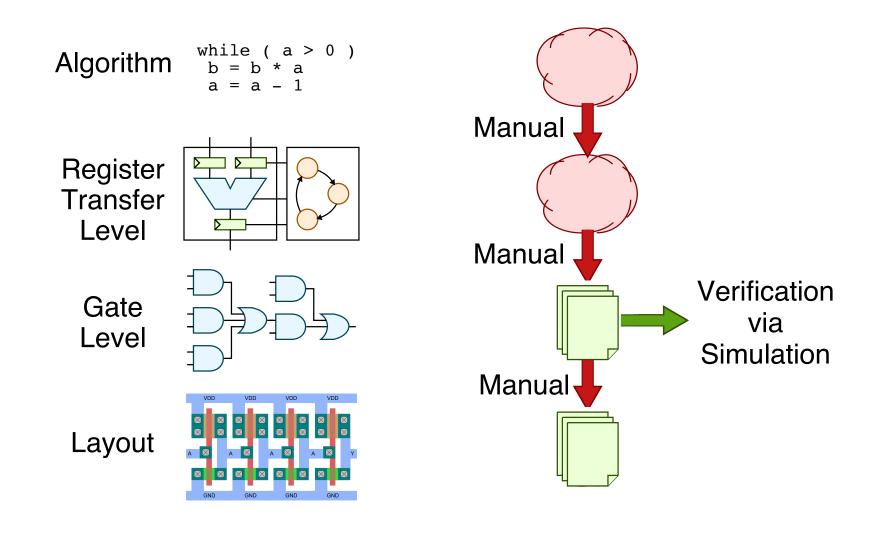

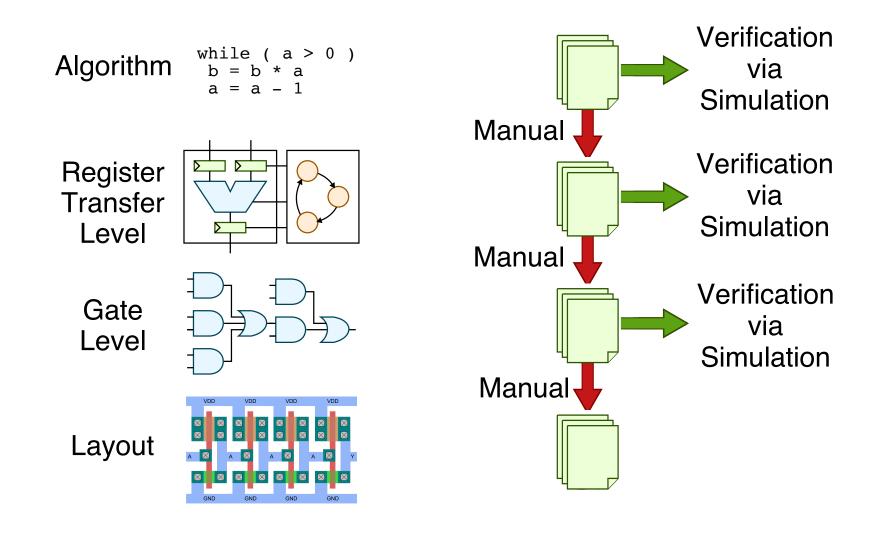

# Hardware description languages enabled gate-level verification via simulation

## Designers began to use HDLs for higher-level verification and design exploration

# High-level algorithmic models act as a precise and executable specification

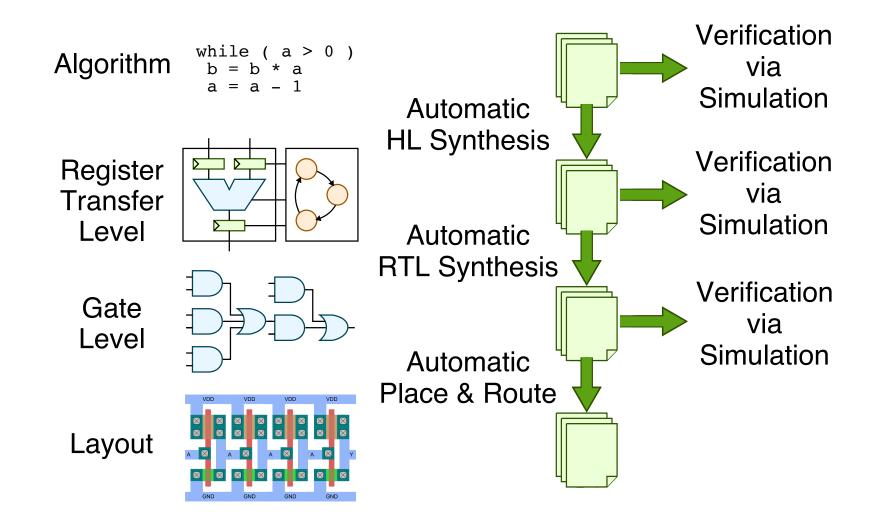

# Once designs were written in HDLs tools could be used for automatic translation

#### Hardware Verification Languages

- A separate or embedded language that is meant purely for verification as opposed to simulation or synthesis

- Includes high-level programming features to simplify writing test benches such as object-oriented constructs and random stimulus generation

- Includes special language constructs for writing complex assertions

- Example HVLs: e, OpenVera, PSL, SystemVerilog Verification Subset

- Example SystemVerilog assertions

- Assert that the read enable and write enable signals are never both true: assert ! (read\_en && write\_en);

- Assert that priority register in round-robin arbiter is one-hot: assert property (@(posedge clk) \$onehot(priority))

- Assert that acknowledge signal is true cycle after the request signal is true: assert property (@(posedge clk) req |-> ##[1] ack);

#### Agenda

### Evolution of Hardware Description Languages

#### Hardware Description Languages Across Stack

#### "High-Level" RTL with SystemVerilog

#### Guarded-Atomic Actions with Bluespec

System-Level Modeling with SystemC

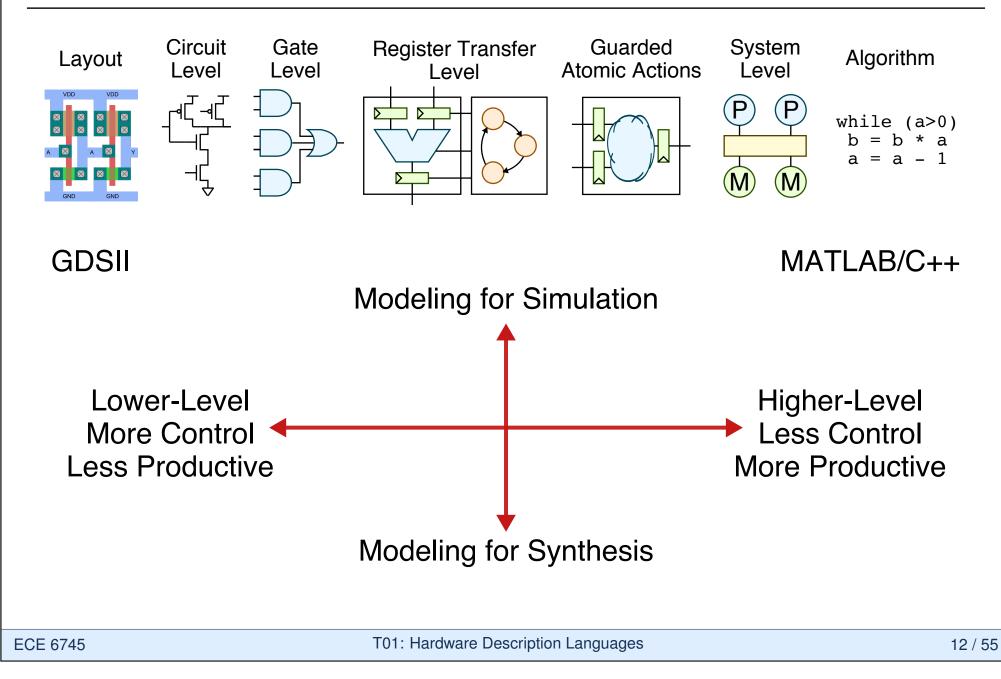

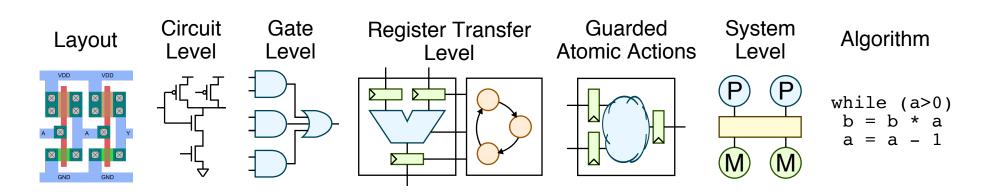

## **HDLs Across The Computer Engineering Stack**

#### **Circuit-Level Modeling with Spice**

CMOS NAND qate \* MP1 4 3 3 CMOSP W=28.0U L=2.0U AS=252P AD=252P 1 CMOSP W=28.0U L=2.0U AS=252P AD=252P MP2 4 2 3 3 5 CMOSN W=10.0U L=2.0U AS=90PAD=90P MN1 0 4 1 CMOSN W=10.0U L=2.0U AS=90P AD=90P MN2 5 2  $\left( \right)$  $\left( \right)$

```

* Input stimulus

VINA 2 0 PULSE(0 5 100ns 5ns 5ns 100n 200ns)

VINB 1 0 PULSE(0 5 205ns 5ns 5ns 200n 400ns)

VDD 3 0 DC 5.0

```

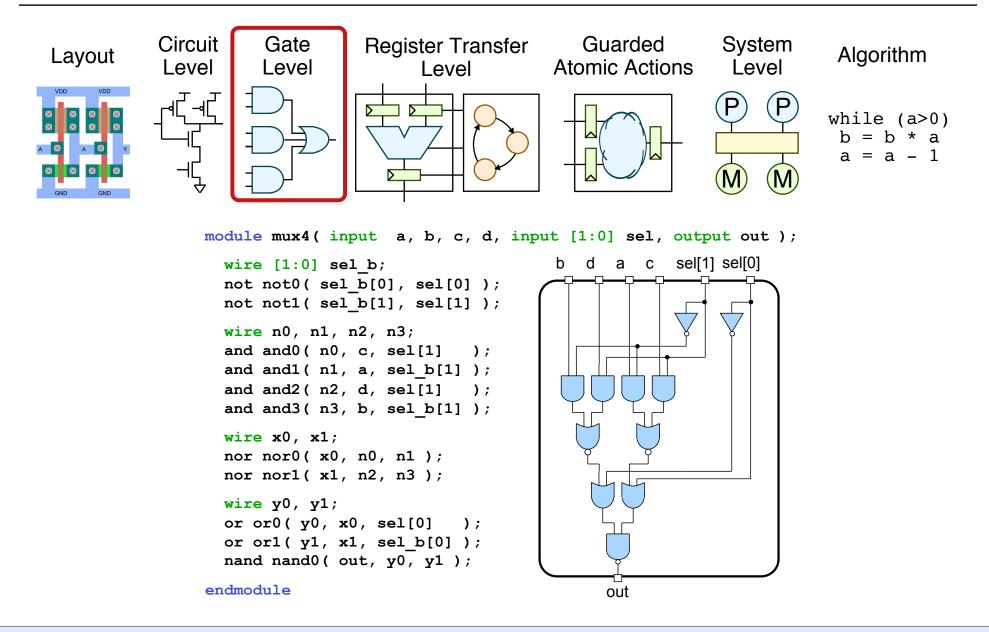

#### **Gate-Level Modeling with Verilog**

#### "Low-Level" RTL Modeling with Verilog

```

// Sequential State

```

```

always @ ( posedge clk ) begin

if ( sign_en ) begin

sign_reg <= sign_next;

end</pre>

```

```

if ( result_en ) begin

result_reg <= result_mux_out;

end</pre>

```

```

counter_reg <= counter_mux_out;

a_reg <= a_mux_out;

b_reg <= b_mux_out;

end

```

reg [63:0] result\_reg;

#### Simulation vs. Synthesis Mismatch

// Mux with assign statement // Mux with always block

```

wire [3:0] out

= ( sel == 0 ) ? a : b;

```

What happens if the sel signal contains an X?

```

req [3:0] out;

always @(*)

begin

```

```

if ( sel == 0 )

out = a;

else

out = b;

```

#### end

#### **Higher-Level HDLs**

How can we raise the level of abstraction to increase hardware design productivity?

- "High-Level" Register-Transfer-Level Modeling with SystemVerilog

- Guarded Atomic Actions with Bluespec

- System-Level Modeling with SystemC

#### Agenda

Evolution of Hardware Description Languages

Hardware Description Languages Across Stack

## "High-Level" RTL with SystemVerilog

**Guarded-Atomic Actions with Bluespec**

System-Level Modeling with SystemC

#### SystemVerilog: Struct and Union Types

| 8        | 24                          |           | 8                      |     | 24    | 24      | 24           | 24             | ŀ     |

|----------|-----------------------------|-----------|------------------------|-----|-------|---------|--------------|----------------|-------|

| JUMP     | addr                        |           | ADD                    | )   | rd    | rt      | rs           | 0              |       |

| 31 24    | 23                          | 0         | 31                     | 24  | 23 1  | 9 18 14 | 4 13 9       | 8              | 0     |

| // Decla | re JumpInstr str            | ucture    | // Dec                 | cla | are A | ddIns   | tr st        | ructur         | ce    |

| ypedef   | <pre>struct packed {</pre>  |           | typede                 | ef  | stru  | ct pa   | cked         | {              |       |

| logic    | [7:0] opcode;               |           | log:                   | ic  | [7:0  | ] opc   | ode;         |                |       |

| logic    | [23:0] addr                 |           |                        |     | -     | ] rd;   |              |                |       |

| } JumpIn | str;                        |           | <b>logic</b> [4:0] rt; |     |       |         |              |                |       |

|          |                             |           | log:                   | ic  | [4:0  | ] rs;   |              |                |       |

| // Insta | ntiate JumpInstr            | structure | log:                   | ic  | [8:0  | ] nul   | 1;           |                |       |

|          |                             |           | } Add                  | Ins | str;  |         |              |                |       |

| <u> </u> | r instr;                    |           |                        |     |       |         |              |                |       |

| -        | <pre>code = c_opcode_</pre> | jump;     | // Dec                 | cla | ire I | nstr    | union        |                |       |

| instr.ad | dr = addr;                  |           |                        |     |       |         |              |                |       |

|          |                             |           | typede                 |     |       | -       | ked {        |                |       |

| JumpInst |                             |           | -                      | -   |       | jump;   |              |                |       |

|          | code: c_opcode_j            | ump,      |                        |     | str   | add;    |              |                |       |

| ad       | dr: addr };                 |           | } Inst                 | tr; |       |         |              |                |       |

|          |                             |           | // Ins                 | sta | intia | te In   | str u        | nion           |       |

|          |                             |           | Instr                  | in  | str;  |         |              |                |       |

|          |                             |           |                        | .ju | imp.o | -       | = c_<br>= ad | opcode<br>ldr; | e_jun |

#### SystemVerilog: Tagged Union Types

| 8                                | 24                                                                             |  |  |  |  |

|----------------------------------|--------------------------------------------------------------------------------|--|--|--|--|

| JUMP                             | addr                                                                           |  |  |  |  |

| 31 24                            | 23 0                                                                           |  |  |  |  |

| // Decla                         | re Instr w/ common opcode                                                      |  |  |  |  |

| logic                            | <pre>struct packed { [23:0] addr strFields;</pre>                              |  |  |  |  |

| logic<br>logic<br>logic<br>logic | <pre>struct packed { [4:0] rd; [4:0] rt; [4:0] rs; [8:0] null; trFields;</pre> |  |  |  |  |

| JumpIn                           | <pre>union packed { strFields jump; trFields add; ields;</pre>                 |  |  |  |  |

| logic                            | <pre>struct packed { [7:0] opcode; ields fields;</pre>                         |  |  |  |  |

| 8                                         |                | 24    |       | 24           |       |

|-------------------------------------------|----------------|-------|-------|--------------|-------|

| ADD                                       | rd             | rt    | rs    | 0            |       |

| 31 24                                     | 23 19          | 18 14 | 13 9  | 8            | 0     |

| // Decla                                  | red I          | nstr  | tagge | ed unic      | n     |

| <pre>typedef JumpIn AddIns } Instr;</pre> | strFi<br>trFie | elds  | jump; |              |       |

| // Insta                                  | ntiat          | e Ins | tr ta | igged i      | inion |

| Instr in<br>= <b>tagg</b>                 |                | mp {  | addr: | addr         | };    |

| // Patte                                  | ern ma         | tchin | g     |              |       |

|                                           | add:           | CS=   | { sel | a, y<br>b, n |       |

#### SystemVerilog: Typed Ports and Type Parameters

```

// Structs, unions, tagged unions // Type parameter allows more

// can be used as ports

```

```

module InstrDecodeTable

input Instr instr,

output ControlSigs cs

// Use structure selectors

```

```

// to access instruction

// and control signal fields

```

endmodule

```

// expressive polymorphism

```

```

module Oueue

# (

parameter type ItemType

) (

input clk, reset

```

input eng val, output eng rdy, input ItemType eng item,

output deq val, input deq\_rdy output ItemType deq\_bits,

// Use \\$bits for size of item

#### endmodule

```

// Instantiate polymorphic queue

Queue#(Instr) queue( ... )

```

#### SystemVerilog: Port Bundle Interfaces

#### // Declare valrdy interface

#### endinterface

// Instantiate and use interface

ValRdyIfc channel; Producer producer(channel); Consumer consumer(channel);

#### // Using an interface

```

module Producer

(

input clk, reset,

ValRdyIfc.send_ifc send_ifc

)

```

#### // ...

```

always @( posedge clk )

begin

send_ifc.val = ...

send_ifc.msg = ...

end

```

#### endmodule

Evolution of HDLs HDLs Across Stack • "High-Level" RTL • Guarded-Atomic Actions System-Level Modeling

#### SystemVerilog: Method Interfaces

// Declare valrdy method interface // Using an method interface

```

interface ValRdyIfc;

logic val;

logic rdy;

logic [31:0] msq;

```

// ...

```

function send

(input logic [31:0] msg); logic done;

// ...

endfunction

```

```

function is send done

( output logic done );

// ...

endfunction

```

```

endinterface

```

```

module Producer

input clk, reset,

ValRdyIfc.send ifc send ifc

```

```

// ...

```

. . .

```

always @( posedge clk )

begin

send_ifc.send( msg );

send ifc.is send done( done );

if ( done )

```

end

endmodule

### SystemVerilog: Interfaces

#### Agenda

Evolution of Hardware Description Languages

Hardware Description Languages Across Stack

"High-Level" RTL with SystemVerilog

Guarded-Atomic Actions with Bluespec

System-Level Modeling with SystemC

#### **Designers Usually Use Weak Interfaces**

Example: Commercially available FIFO IP block

An error occurs if a push is attempted while the FIFO is full.

data\_in data\_out push\_req\_n full empty pop\_req\_n clk rstn

Thus, there is no conflict in a simultaneous push and pop when the FIFO is full. A simultaneous push and pop cannot occur when the FIFO is empty, since there is no pop data to prefetch. However, push data is captured in the FIFO.

A pop operation occurs when pop\_req\_n is asserted (LOW), as long as the FIFO is not empty. Asserting pop\_req\_n causes the internal read pointer to be incremented on the next rising edge of clk. Thus, the RAM read data must be captured on the clk following the assertion of pop\_req\_n.

These constraints are spread over many pages of the documentation...

Adapted from [Arvind'11]

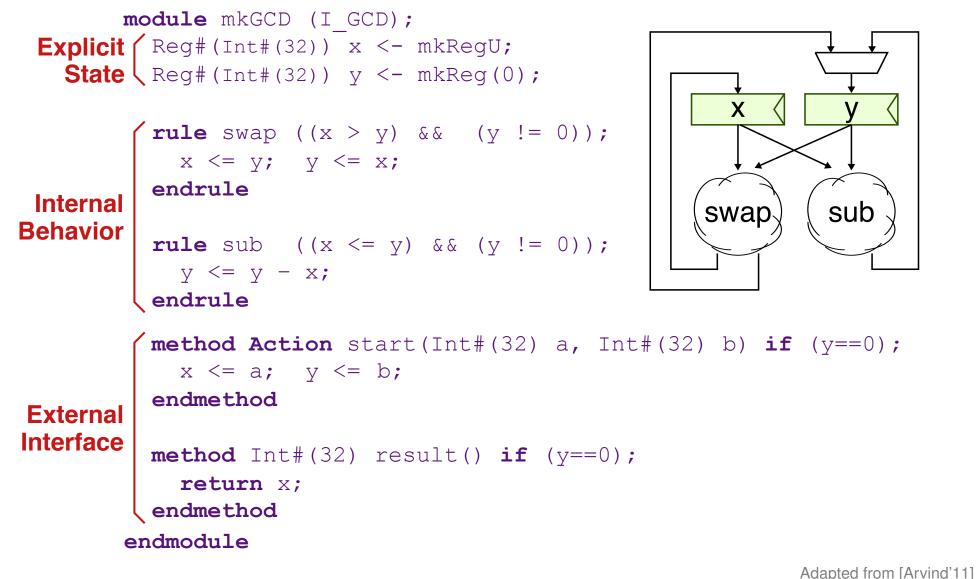

## Expressing Hardware with Guarded Atomic Actions in Bluespec

#### Guarded rules

- Hardware expressed as collection of rules that execute atomically and in a well-defined serialized sequence

- Allows thinking of pieces of the design in isolation

- Compiler manages scheduling of rules to increase performance

- Guarded method interfaces

- Formalizes composition

- Compiler manages connectivity (muxing and control logic)

- Powerful type and static elaboration facilities

- Significant amount of compile-time static checking

- Permits parameterization of designs at all levels

## **Guarded Atomic Action Execution Model**

#### Semantics

- Actions execute in a serialized order

- Actions execute in isolation

#### Repeatedly

- Select a rule to execute (highly non-deterministic)

- Compute the new state values

- Update the state

#### Implementation concerns

- But doesn't executing one rule at a time mean our implementation will be very slow?

- Can we schedule multiple rules concurrently without violating one-rule-at-a-time semantics?

#### State and Rules Organized into Modules

- All state is explicit (no inferred latches or flip-flops)

- Behavior is expressed in terms of guarded rules within each module that atomically update state internal to that module

- Rules can manipulate state in other modules only via their guarded method interfaces

#### GCD Using Euclid's Algorithm

|    | Х  | У  | op     |   |

|----|----|----|--------|---|

| 1. | 25 | 15 | swap   |   |

| 2. | 15 | 25 | sub    |   |

| 3. | 15 | 10 | swap   |   |

| 4. | 10 | 15 | sub    |   |

| 5. | 10 | 5  | swap   |   |

| 6. | 5  | 10 | sub    |   |

| 7. | 5  | 5  | sub    |   |

| 8. | 5  | 0  | return | Х |

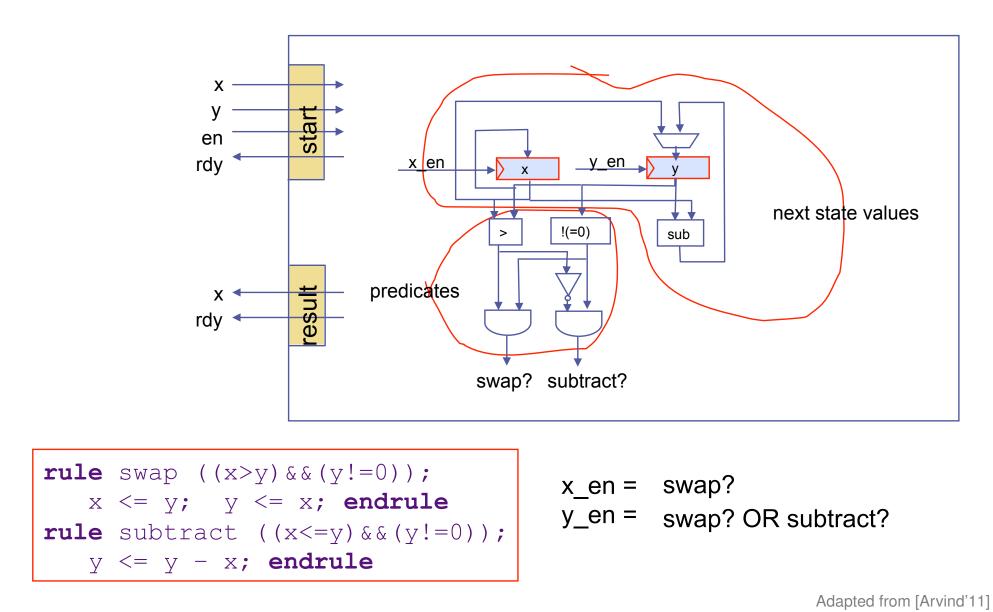

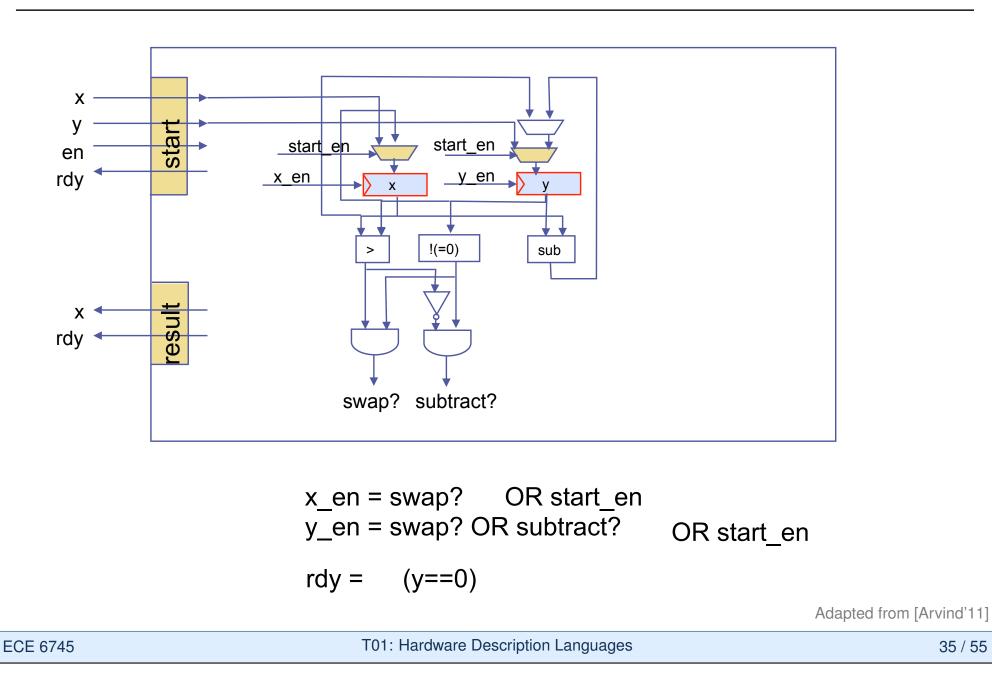

#### **GCD** Implementation in Bluespec

31 / 55

#### **GCD** Alternative Implementation

```

y op

Х

module mkGCD (I GCD);

1. 25 15 swapsub

\operatorname{Reg}#(Int#(32)) x <- mkRegU;

2. 15 10 swapsub

Req#(Int#(32)) y < - mkReq(0);

3.10 5 swapsub

Combined

rule swapsub ((x > y) \& (y != 0));

4. 5 5 sub

Rule

x \leq y; y \leq x - y;

5. 5 0 return x

endrule

rule sub ((x <= y) && (y != 0));

y \ll y - x;

endrule

method Action start(Int#(32) a, Int#(32) b) if (y==0);

x <= a; v <= b;

endmethod

method Int#(32) result() if (y==0);

return x;

endmethod

endmodule

```

ECE 6745

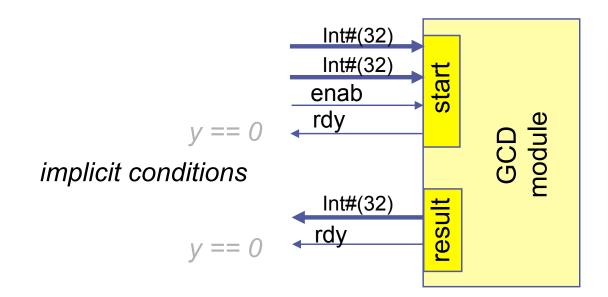

#### **Generated GCD Hardware: Interface**

- Module can easily be made polymorphic as in SystemVerilog

- Many different implementations can provide the same interface

#### **Generated GCD Hardware: Rules**

#### **Generated GCD Hardware: Rules and Methods**

35 / 55

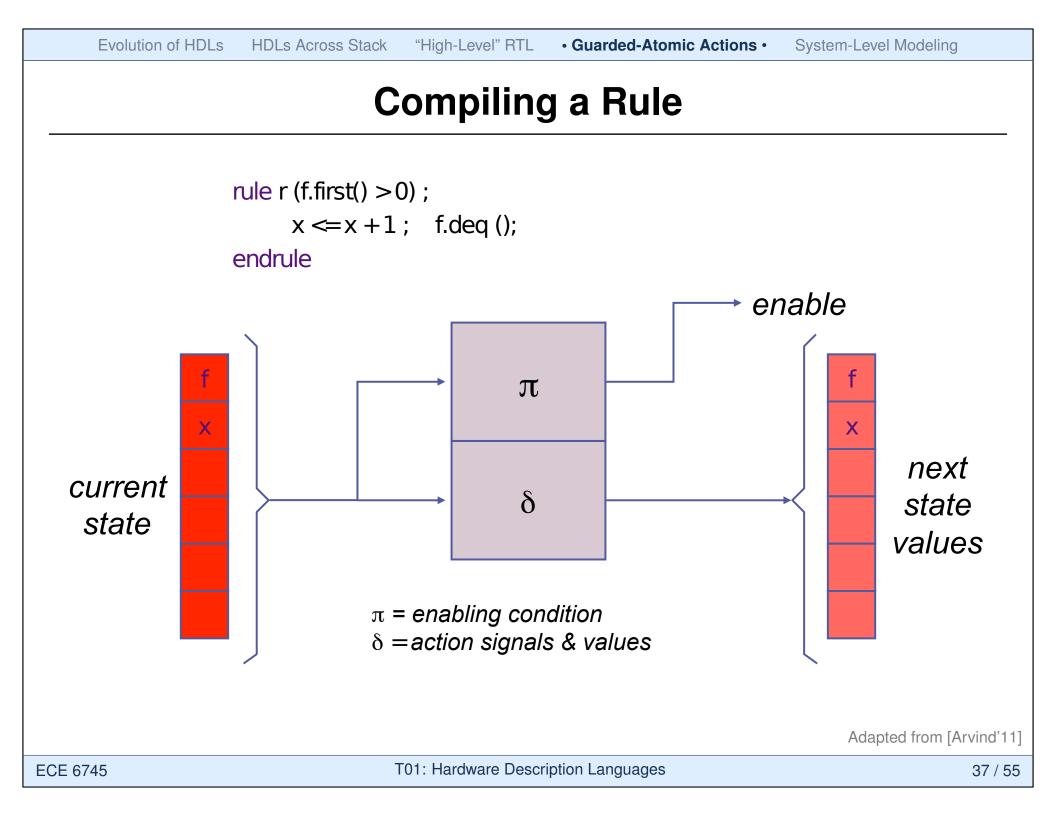

#### A Systematic Approch to GAA Synthesis

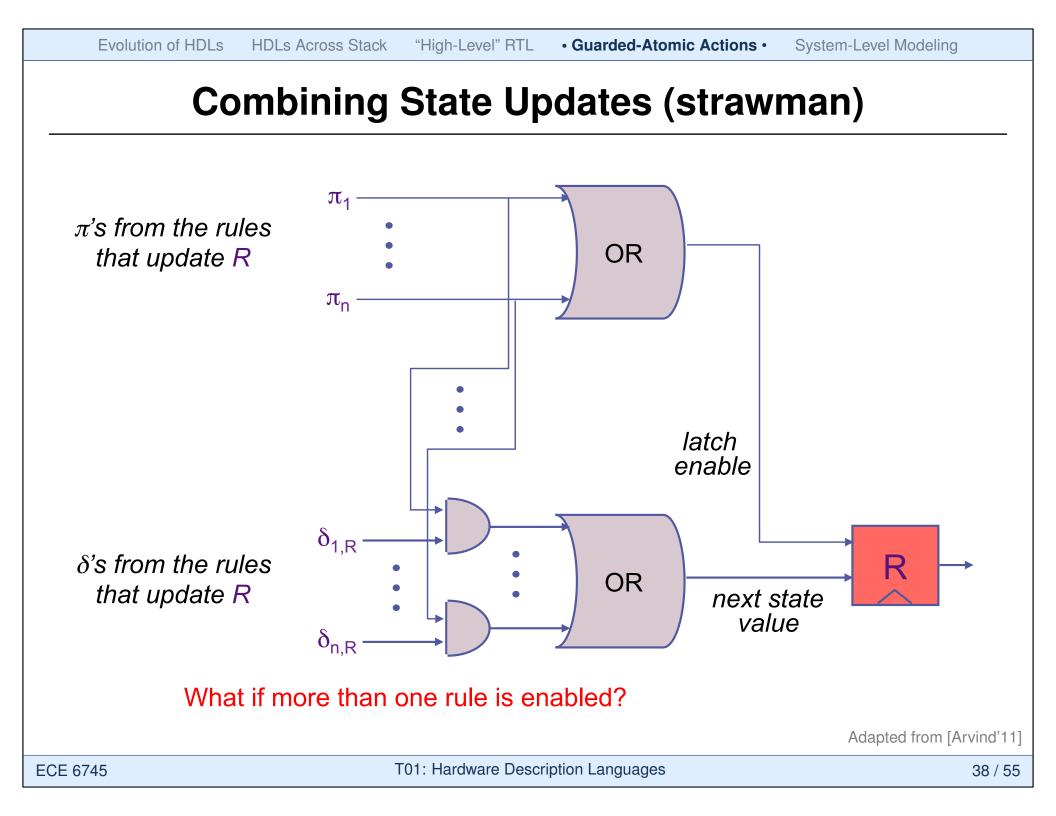

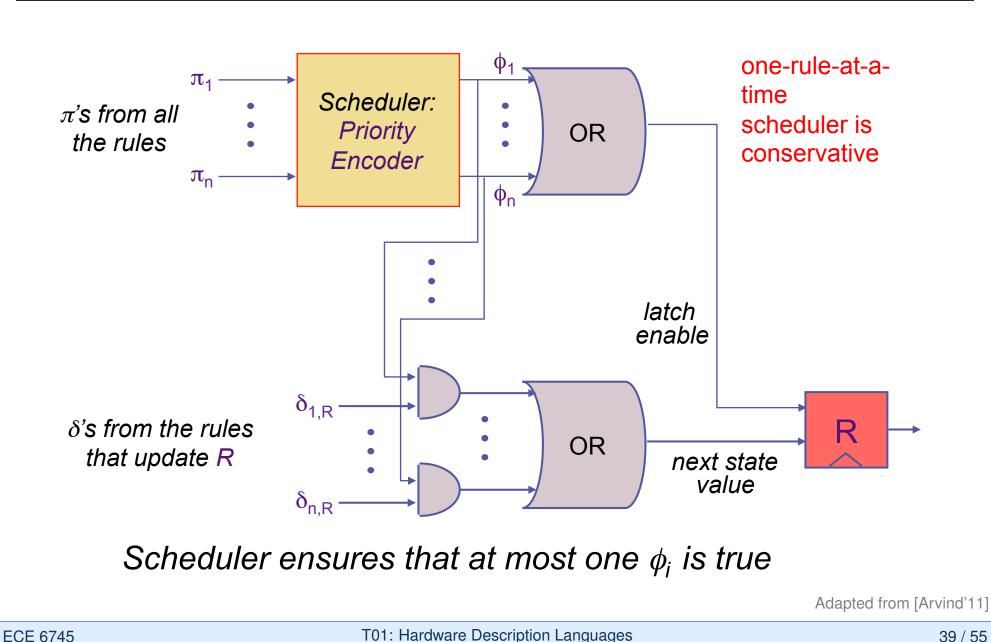

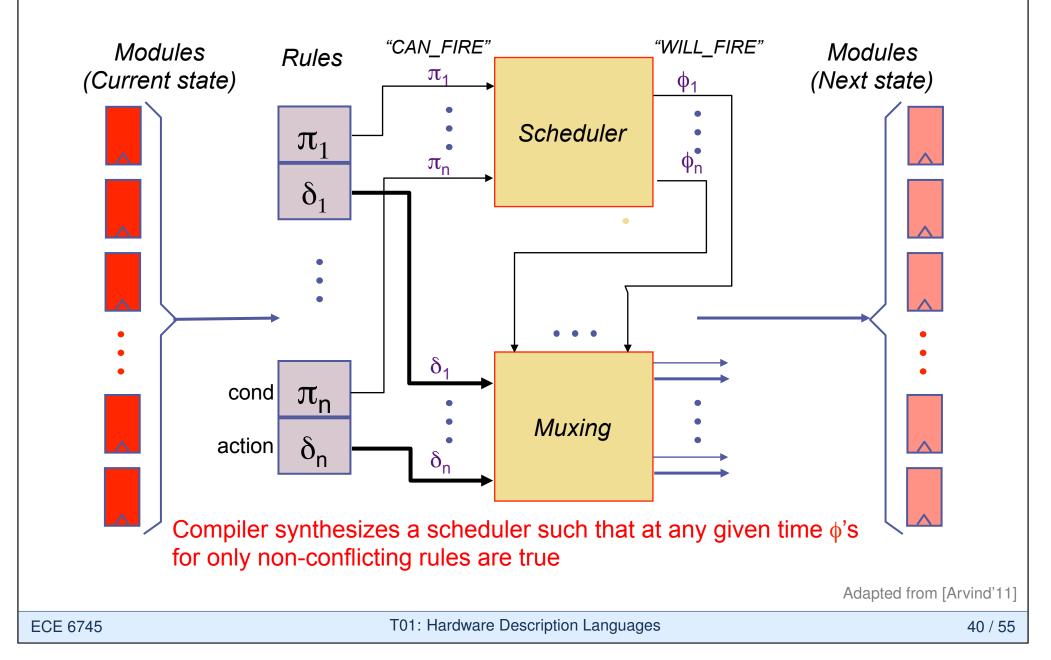

A rule may be decomposed into two parts  $\pi(s)$  and  $\delta(s)$  such that

$$s_{next} = if \pi(s) then \delta(s) else s$$

$\pi(s)$  is the condition (predicate) of the rule, a.k.a. the "CAN\_FIRE" signal of the rule.  $\pi$  is a conjunction of explicit and implicit conditions

$\delta(s)$  is the "state transformation" function, i.e., computes the next-state values from the current state values

Adapted from [Arvind'11]

# **Combining State Updates**

# **Scheduling and Control Logic**

## Agenda

Evolution of Hardware Description Languages

Hardware Description Languages Across Stack

"High-Level" RTL with SystemVerilog

Guarded-Atomic Actions with Bluespec

System-Level Modeling with SystemC

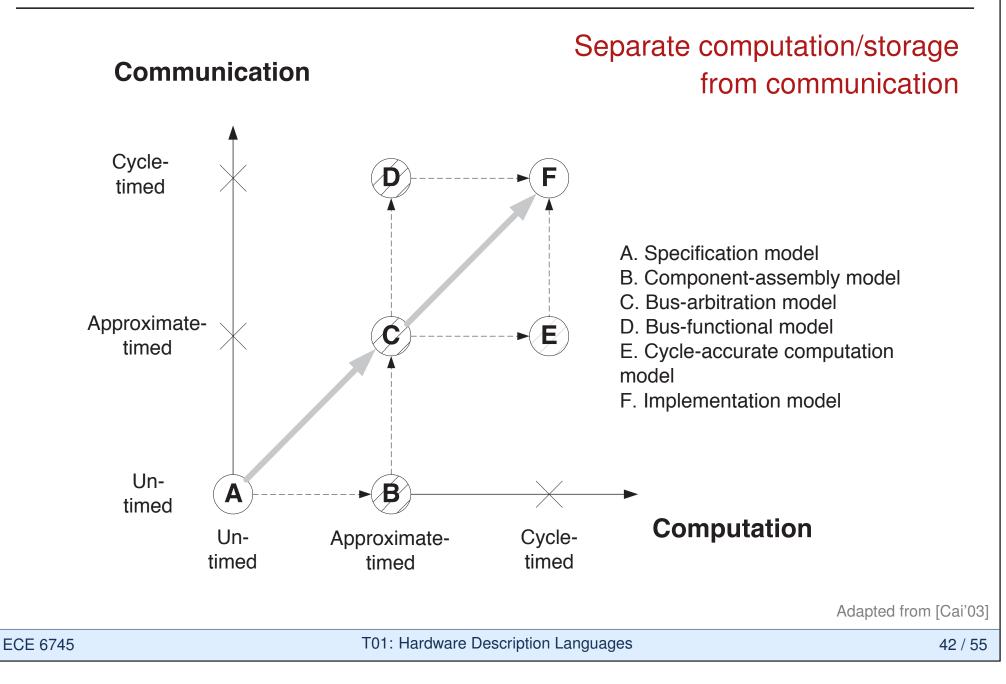

# **System-Level Modeling**

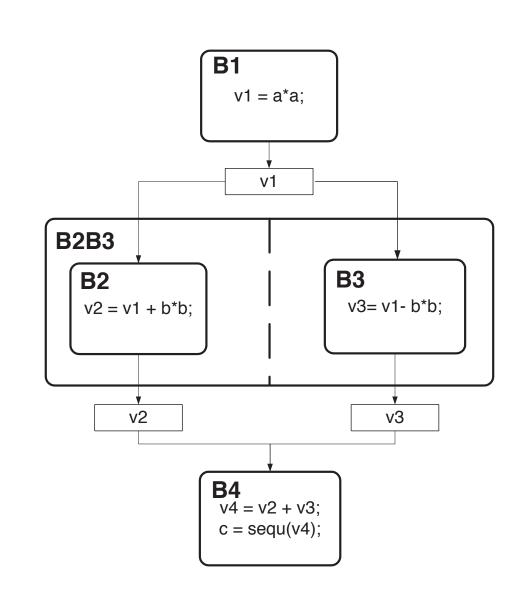

# **Specification Model**

- Describes system functionality without any implementation details

- Computation modeled as abstract concurrent processes

- Communication modeled with standard software variables

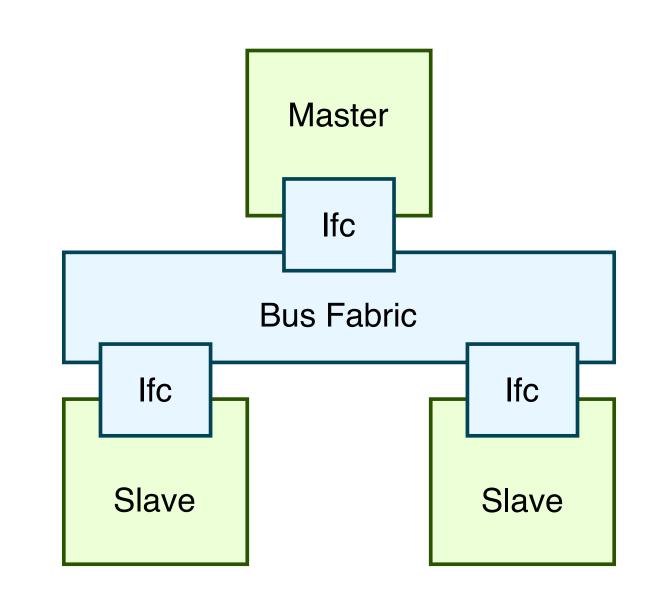

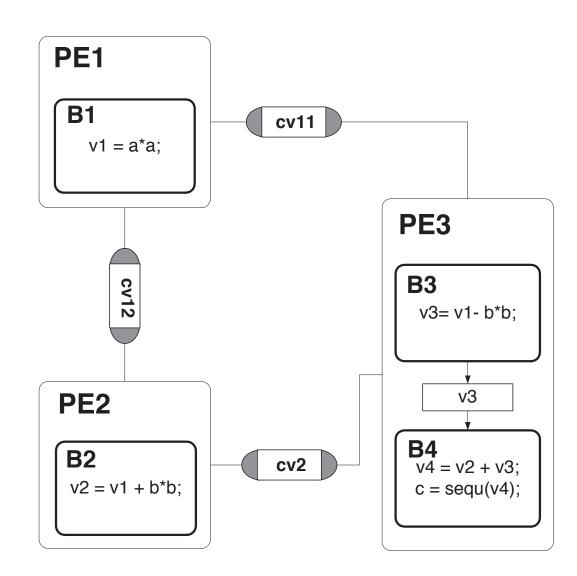

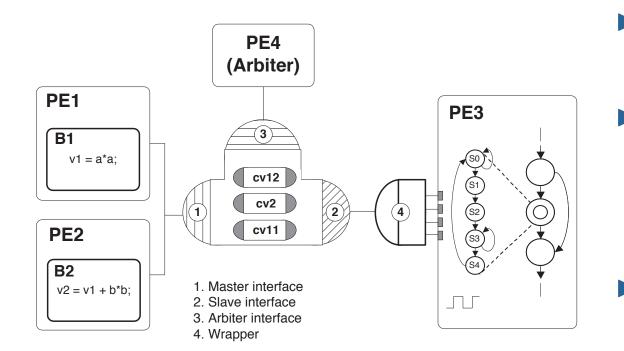

# **TLM: Component-Assembly Model**

- Approximately estimate execution time of PEs using first-order models

- Explicitly capture process-to-PE mapping

- Use dedicated point-to-point channels to interconnect computation and storage PEs

- No modeling of bus or protocol details

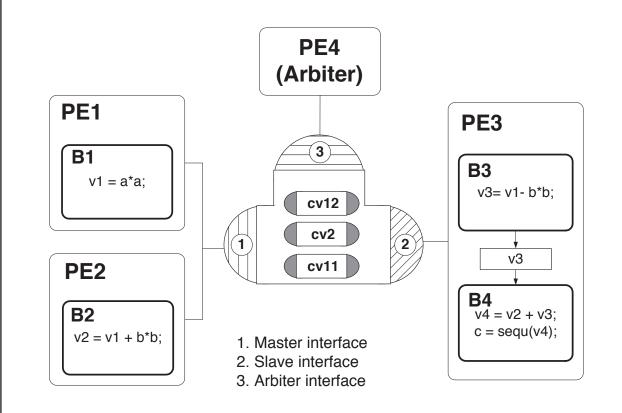

# **TLM: Bus-Arbitration Model**

- Approximately estimate execution time of PEs using first-order models

- Explicitly capture channel-to-bus mapping

- Still communicate through abstract channels, but also estimate bus performance with first-order arbitration models

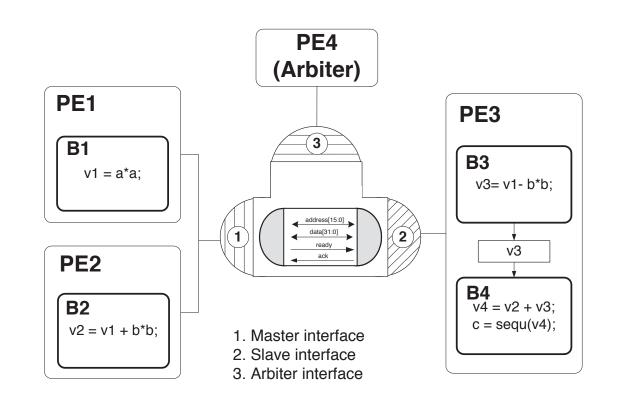

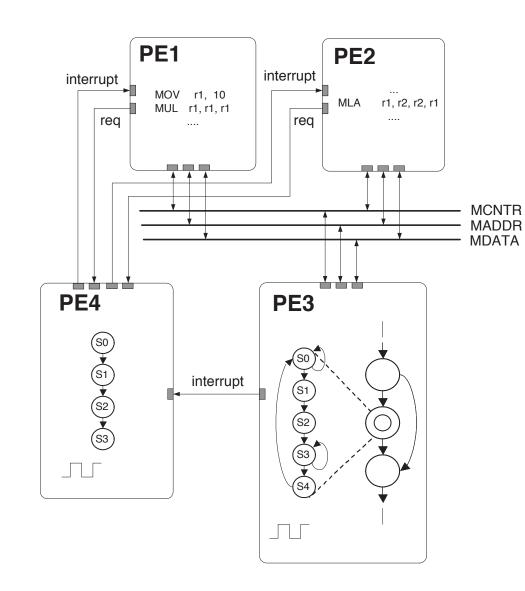

## **TLM: Bus-Functional Model**

- Approximately estimate execution time of PEs using first-order models

- Cycle-accurate RTL model of bus protocol

## **TLM: Cycle-Accurate Computation Model**

- Cycle-accurate RTL model of (some) PEs

- Adapters interface

lower-level RTL

interface to higher-level

bus-arbitration model

- Still communicate through abstract channels, but also estimate bus performance with first-order arbitration models

### **Register-Transfer-Level Model**

Cycle-accurate RTL models of both computation/storage and communication

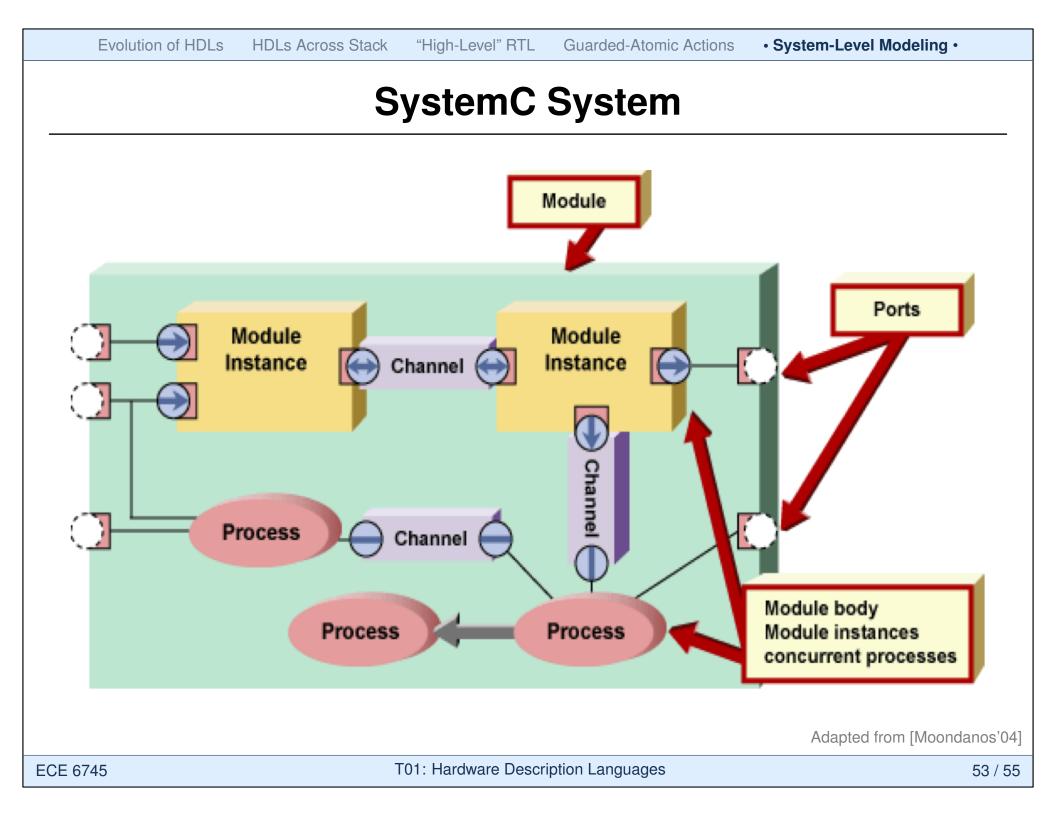

## SystemC Framework

### **Methodology-Specific Libraries**

Master/Slave Lib, Verification Lib, Static Dataflow

#### **Primitive Channels**

Signal, Mutex, Semaphore, FIFO

### Core Language

Modules Ports Processes Interfaces Channels

### Data Types

4-Valued Logic Types 4-Valued Logic Vectors Bits and Bit Vectors Fixed-Point Types C++ User-Defined Types

### **Event-Driven Simulation Kernel**

### C++ Language Standard

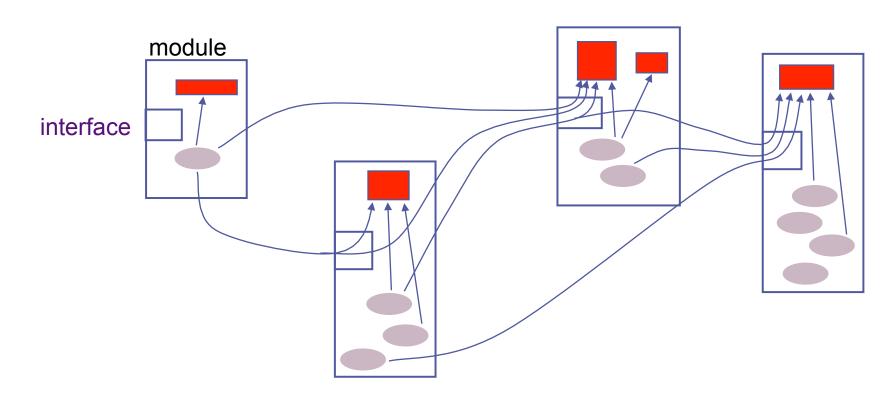

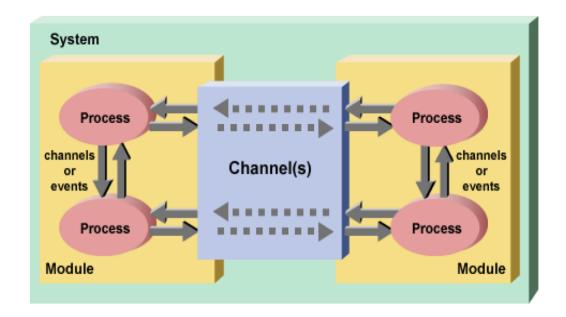

# SystemC Modules, Processes, Channels

- Separate computation from communication

- Computation: implemented with Processes in Modules

- Communication: implemented in Channels

- Interface method calls

- Collection of a fixed set of communication Methods is called an Interface

- Channels implement one or more Interfaces

- Modules can be connected via their Ports to those

Channels which implement the corresponding Interface

Adapted from [Moondanos'04]

# SystemC Producer-Consumer Example

```

struct Producer : public sc_module

{

// Ports

sc out<bool> clk;

sc out<int> value;

SC HAS PROCESS (Producer);

Producer( sc module name name ) : sc module(name)

{

// Declares compute as a thread

SC THREAD (compute);

void compute()

for ( int i = 0; i < 10; ++i ) {

clk.write(false); // toggle clk

wait( 5, SC_NS ); // wait for 5 nanoseconds

clk.write(true); // toggle clk

value.write(i); // write value to channel

wait( 5, SC_NS ); // wait for 5 nanoseconds

};

```

# SystemC Producer-Consumer Example

```

struct Consumer : public sc module

{

// Ports

sc in<bool> clk;

sc_in<int> value;

SC HAS PROCESS (Consumer);

Consumer( sc module name name ) : sc module(name)

// Declares receive() as a process triggered

// on clk value changes

SC_METHOD (receive);

sensitive << clk;</pre>

void receive()

// If clk is changing from false to true

if ( clk.posedge() )

std::cout << 'Received:..' << value.read() << std::endl;</pre>

};

```

# **Take-Away Points**

Hardware description languages involve a four-way tension

- Low-level languages offer more control but less productivity

- High-level languages offer less control but more productivity

- Simulation features for modeling function and test harnesses

- Synthesis features for modeling actual hardware

- Hardware description languages are (slowly) moving towards including higher abstractions to improve productivity such as

- Types, Interfaces (SystemVerilog)

- Guarded Atomic Rules, Guarded Method Interfaces (Bluespec)

- Transaction-Level Modeling (SystemC)

## **Acknowledgments**

- [Arvind'11] Arvind, "Introduction to Bluespec," MIT 6.375 Complex Digital Systems, Lecture, 2011.

- [Cai'03] L. Cai and D. Gajski, "Transaction Level Modeling: An Overview," Int'l Conf. on Hardware/Software Codesign and System Synthesis, Oct. 2003.

- [Moondanos'04] J. Moondanos, "SystemC Tutorial," UC Berkeley EE 249 Embedded System Design, Guest Lecture, 2004.