# ECE 5745 Complex Digital ASIC Design Course Overview

**Christopher Batten**

School of Electrical and Computer Engineering Cornell University

http://www.csl.cornell.edu/courses/ece5745

Technology

# **Complex Digital ASIC Design**

- Course goal, structure, motivation

- What is the goal of the course?

- Why should students want to take this course?

- How is the course structured?

- Activity: Evaluation of Integer Multiplier

- ASIC Design Case Studies

- Example design-space exploration

- > Example real ASIC chips

ASIC Design Case Studies

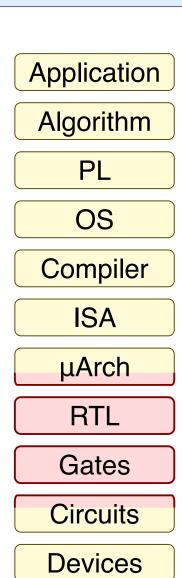

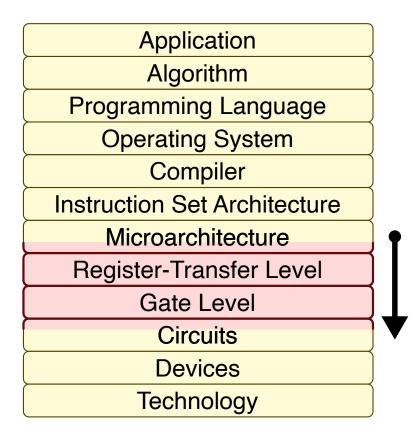

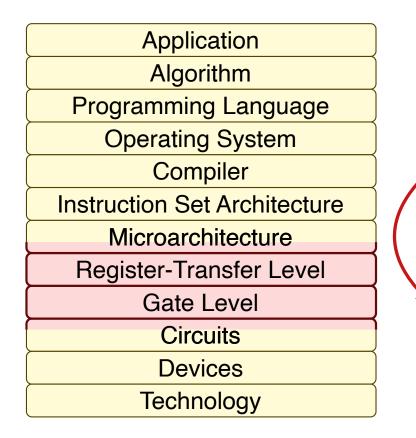

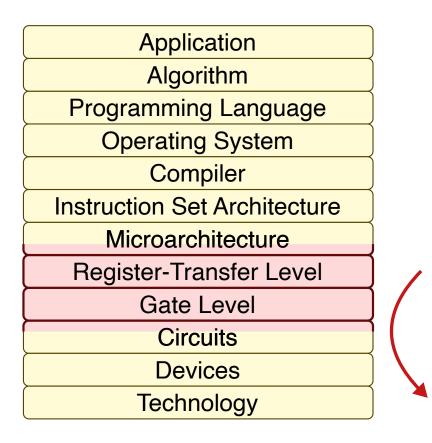

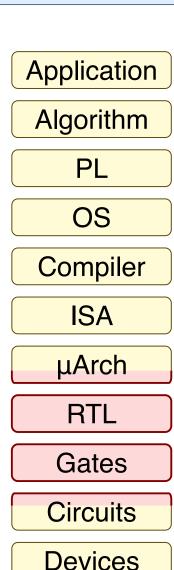

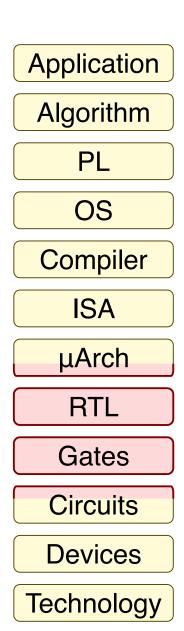

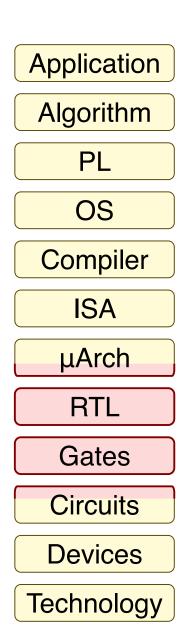

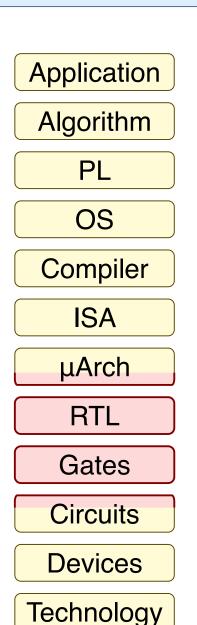

## The Computer Systems Stack

| Application                  |

|------------------------------|

| Algorithm                    |

| Programming Language         |

| Operating System             |

| Compiler                     |

| Instruction Set Architecture |

| Microarchitecture            |

| Register-Transfer Level      |

| Gate Level                   |

| Circuits                     |

| Devices                      |

| Technology                   |

|                              |

In its broadest definition, computer architecture is the design of the abstraction/implementation layers that allow us to execute information processing applications efficiently using available manufacturing technologies

## What is Computer Architecture?

#### **Application Requirements**

- Provide motivation for building system

- SW/HW interface expressive yet productive

Computer architects provides feedback to guide application and technology research directions

#### **Technology Constraints**

- Restrict what can be done efficiently

- New technologies make new arch possible

In its broadest definition, computer architecture is the design of the abstraction/implementation layers that allow us to execute information processing applications efficiently using available manufacturing technologies

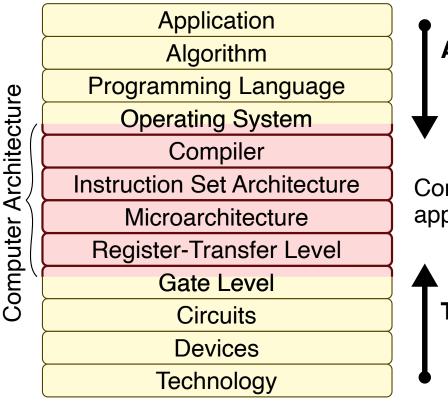

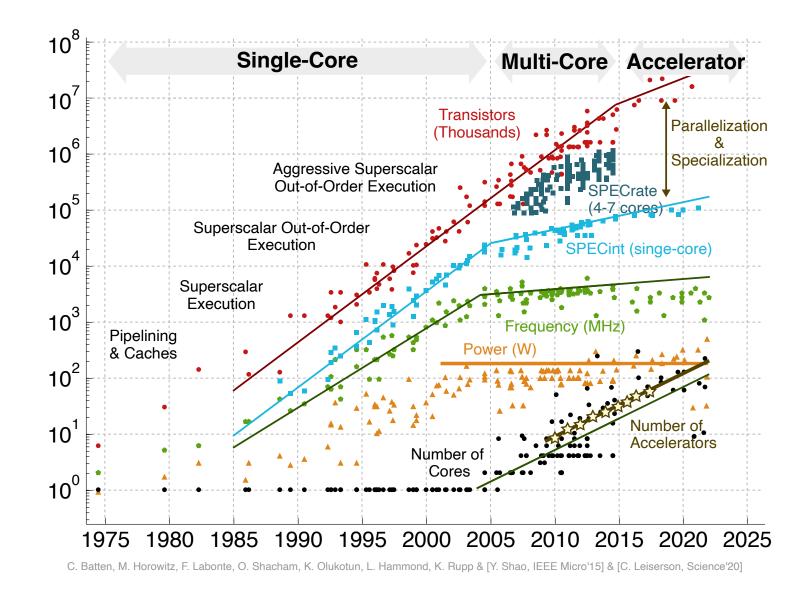

C. Batten, M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, K. Rupp & [Y. Shao, IEEE Micro'15] & [C. Leiserson, Science'20]

## **Key Metrics in Computer Architecture**

- Primary Metrics

- Execution time (cycles/task)

- Energy (Joules/task)

- Cycle time (ns/cycle)

- ⊳ Area (µm<sup>2</sup>)

- Secondary Metrics

- Performance (ns/task)

- Average power (Watts)

- Peak power (Watts)

- ▷ Cost (\$)

- Design complexity

- Reliability

- Flexibility

Discuss qualitative first-order analysis from ECE 4750 on board

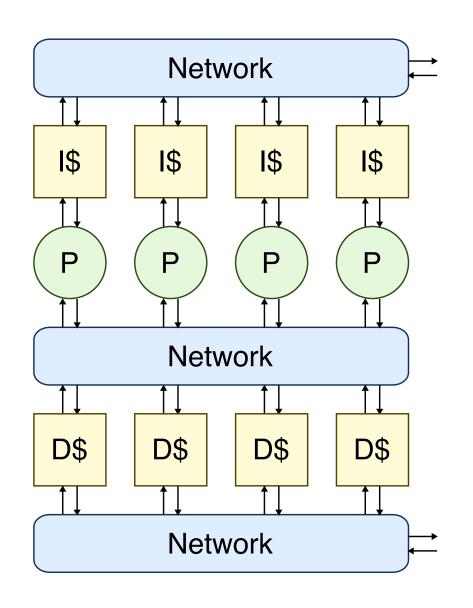

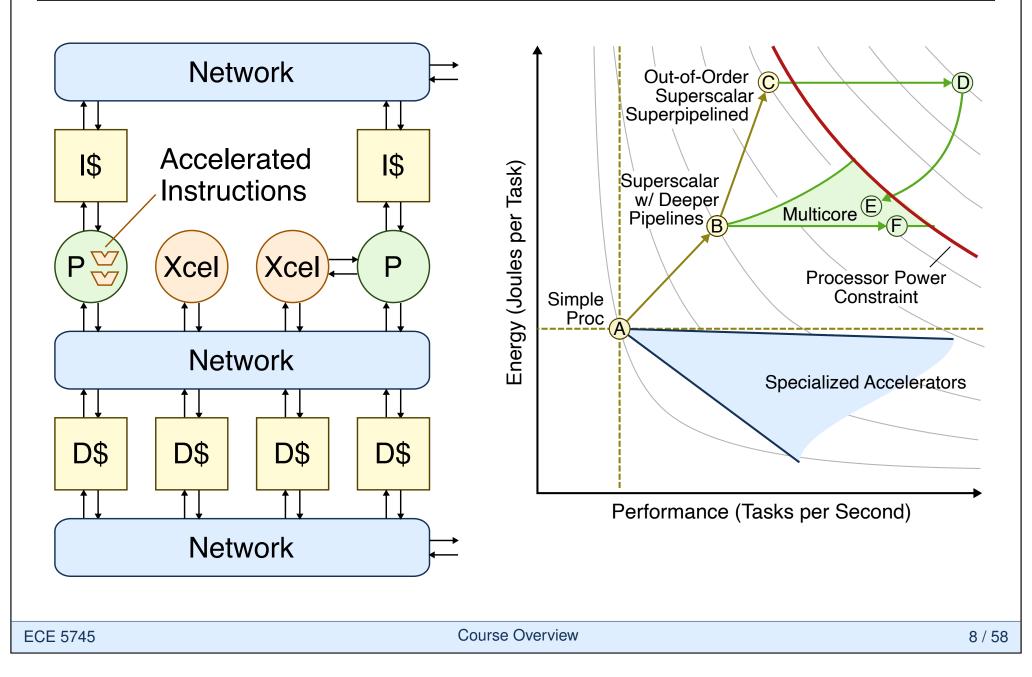

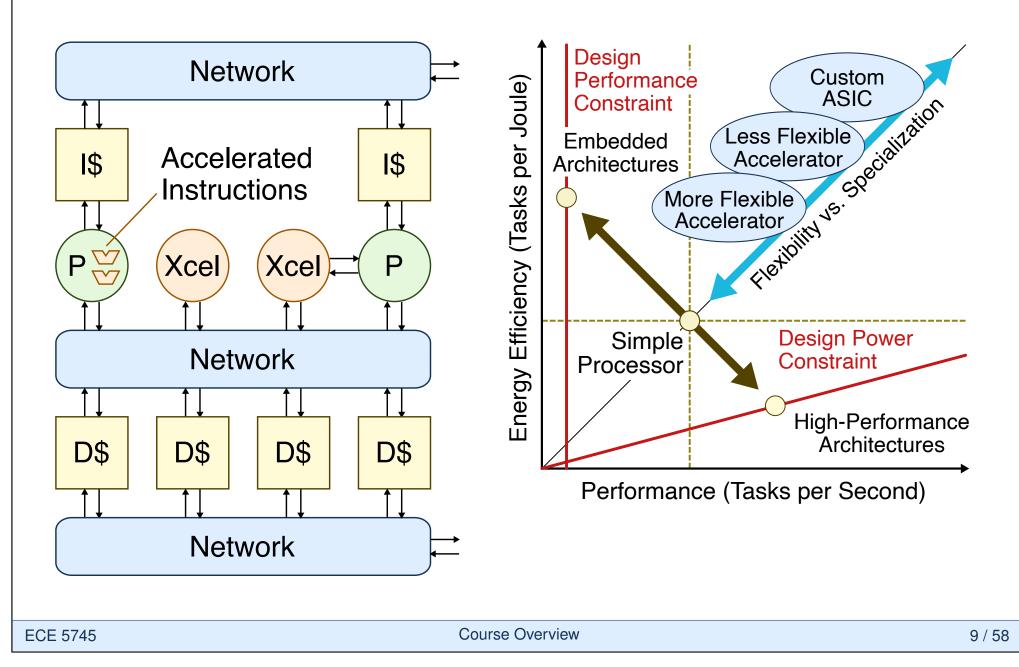

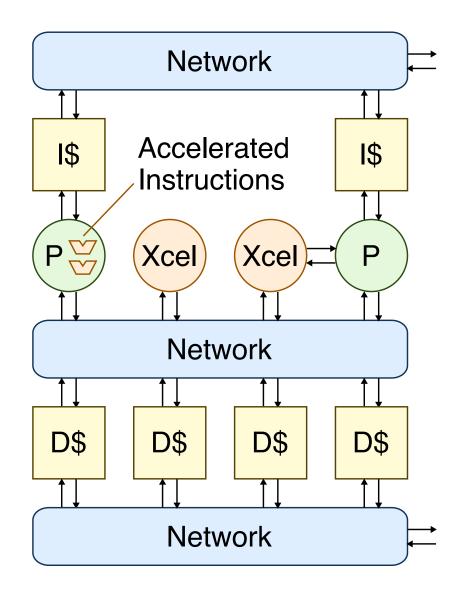

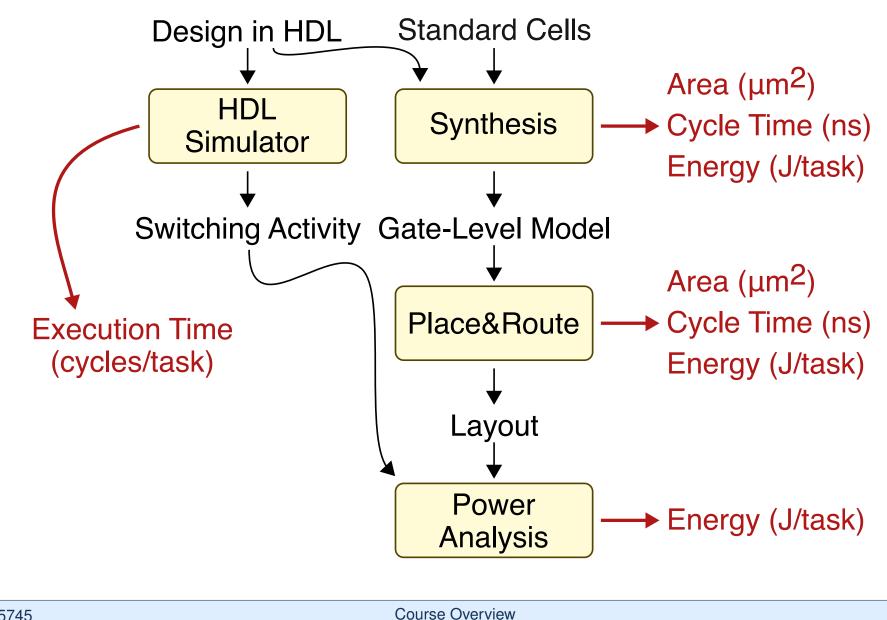

### **Unanswered Questions from ECE 4750**

- How can we quantitatively evaluate area, cycle time, and energy?

- How do we actually implement processors, memories, and networks in a real chip?

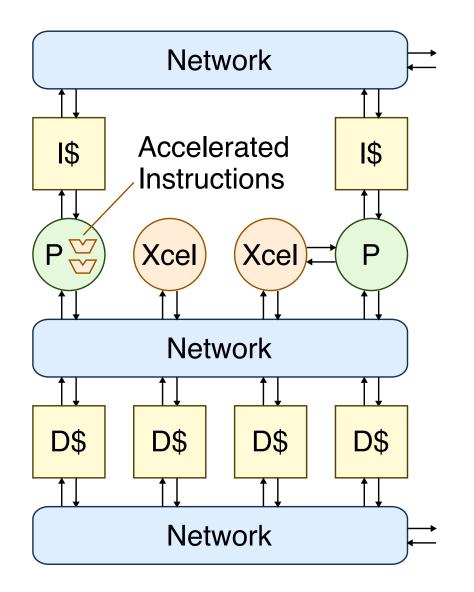

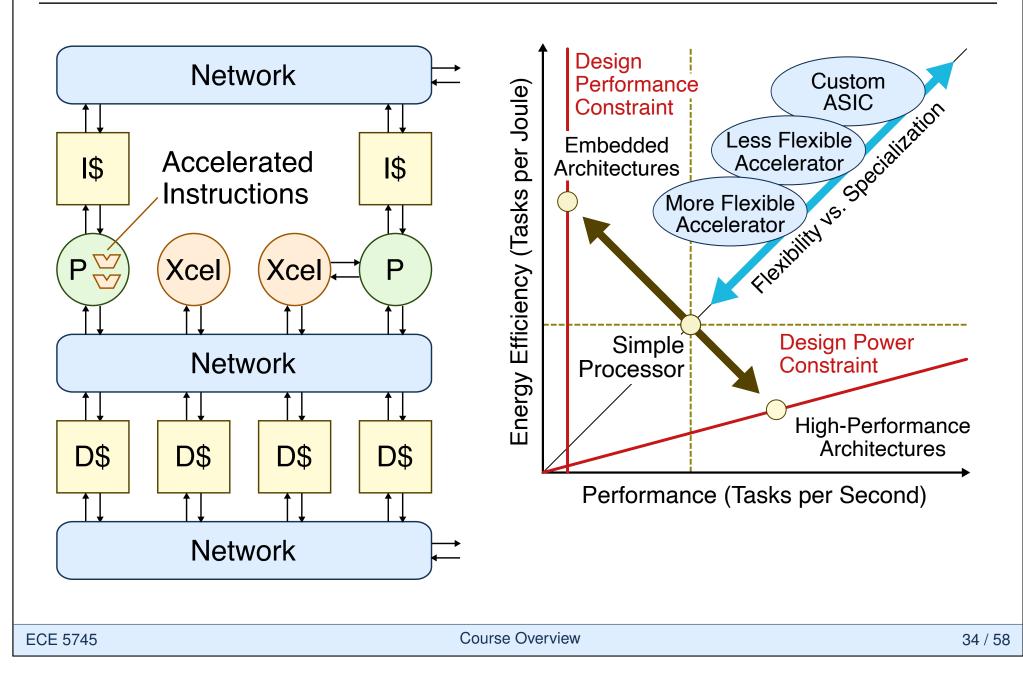

- How should we implement/analyze application-specific accelerators?

- Very loosely coupled memory-mapped accelerators

- More tightly coupled co-processor accelerators

- Specialized instructions and functional units

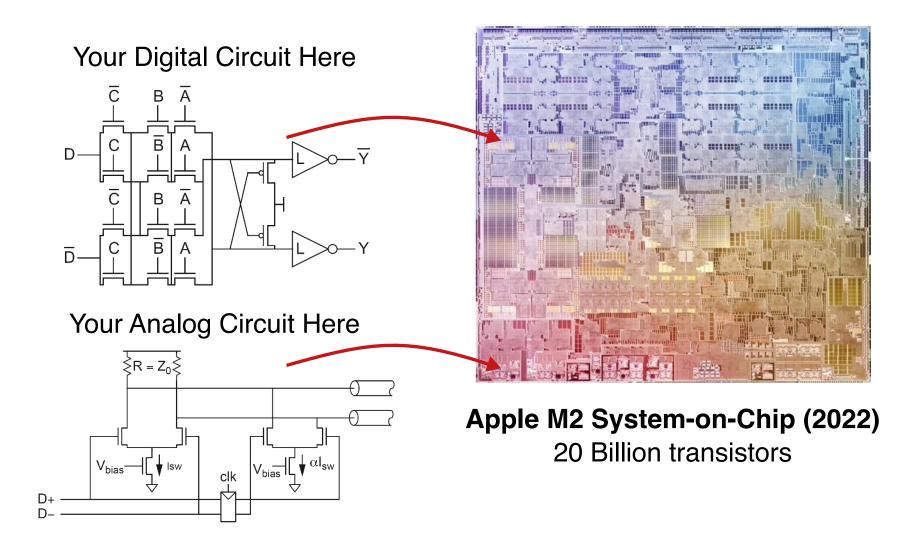

## **ASIC: Application-Specific Integrated Circuit**

## **ASIC: Application-Specific Integrated Circuit**

### Goal for ECE 5745 is to answer these questions!

- How can we quantitatively evaluate area, cycle time, and energy?

- How do we actually implement processors, memories, and networks in a real chip?

- How should we implement/analyze application-specific accelerators?

- Very loosely coupled memory-mapped accelerators

- More tightly coupled co-processor accelerators

- Specialized instructions and functional units

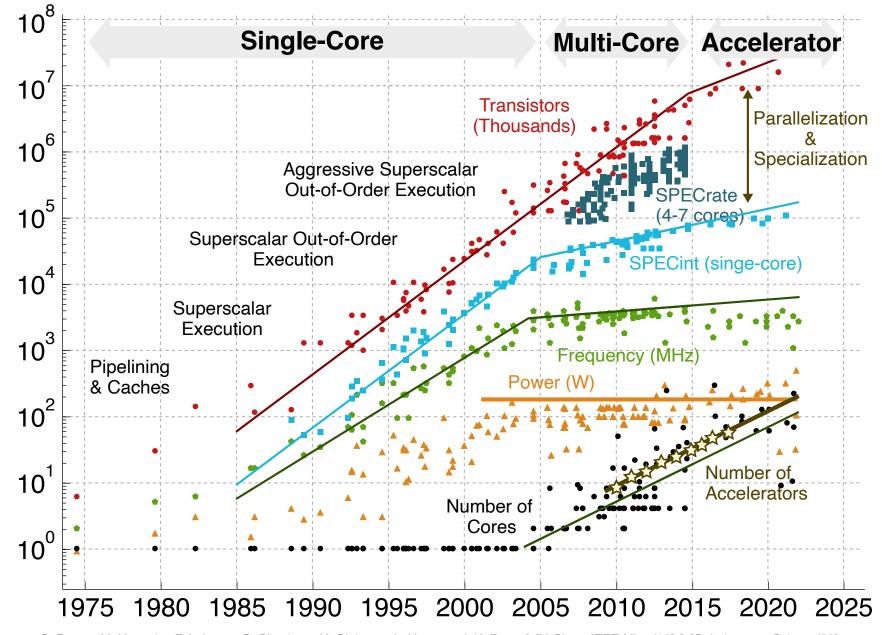

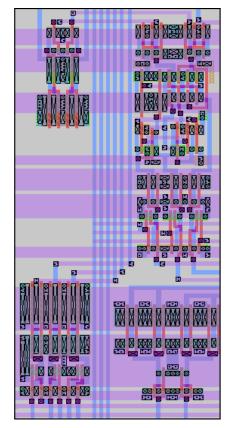

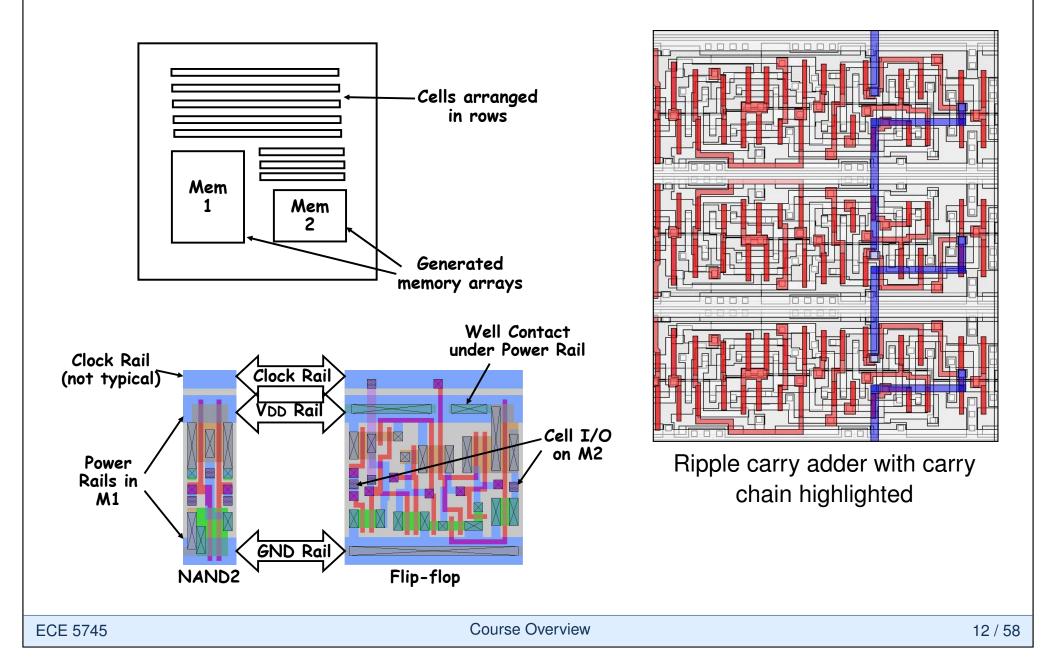

## Full Custom Design vs. Standard-Cell Design

Full-custom layout in 1.0µm w/ 2 metal layers

#### Full-Custom Design (ECE 4740)

- Designer is free to do anything, anywhere; though team usually imposes some design discipline

- Most time consuming design style; reserved for very high performance or very high volume chips (Intel microprocessors, RF power amps for cellphones)

- Standard-Cell Design (ECE 5745)

- Fixed library of "standard cells" and SRAM memory generators

- Register-transfer-level description is automatically mapped to this library of standard cells, then these cells are placed and routed automatically

- ▷ Enables agile hardware design methodology

ASIC Design Case Studies

### **Standard-Cell Design Methodology**

**ASIC Design Case Studies**

### **Standard-Cell Design Methodology**

ASIC Design Case Studies

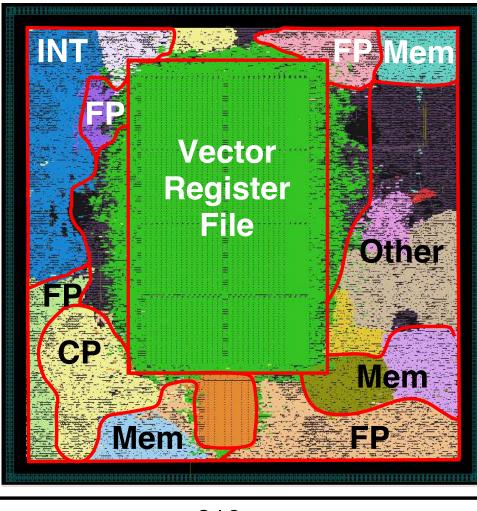

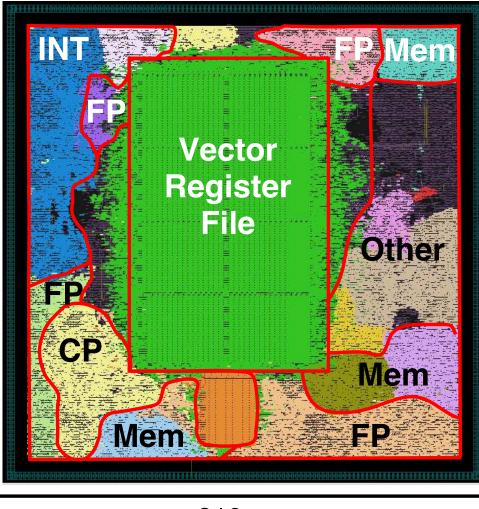

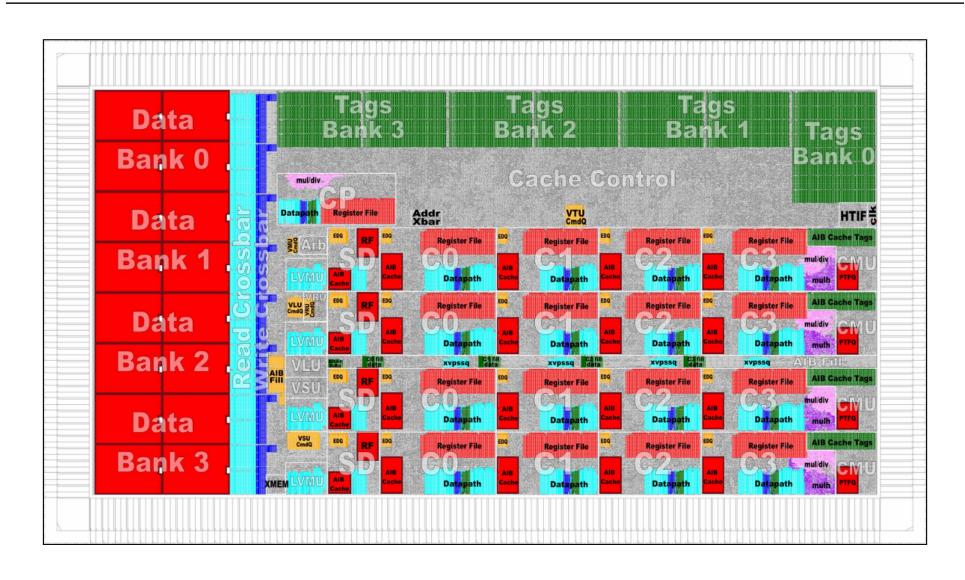

### **Example Standard-Cell Chip Plot**

| Control Processor    | 8.1%  |

|----------------------|-------|

| Vector Register File | 56.9% |

| Vector Integer ALUs  | 9.7%  |

| Vector FPUs          | 9.4%  |

| Vector Memory Units  | 7.6%  |

| Other                | 8.3%  |

810 µm

## What is Complex Digital ASIC Design?

Complex digital ASIC design is the process of

quantitatively exploring the area, cycle time, execution time, and energy trade-offs

of various

application-specific accelerators (and general-purpose proc+mem+net)

using

automated standard-cell CAD tools

and then to transform the most promising design to

layout ready for fabrication

Technology

# **Complex Digital ASIC Design**

- Course goal, structure, motivation

- What is the goal of the course?

- Why should students want to take this course?

- > How is the course structured?

- Activity: Evaluation of Integer Multiplier

- ASIC Design Case Studies

- Example design-space exploration

- Example real ASIC chips

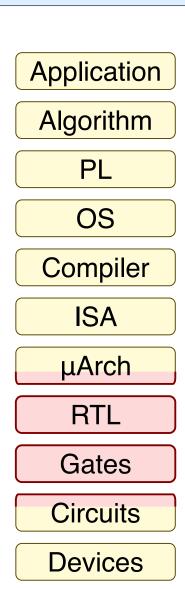

### **Technology Scaling is Slowing**

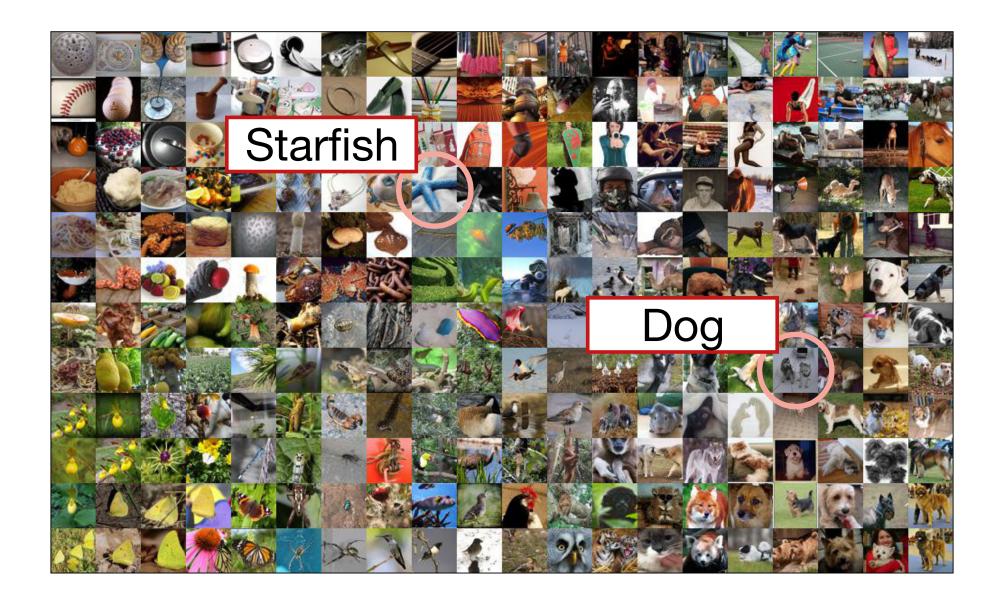

## **Example Application Domain: Image Recognition**

ASIC Design Case Studies

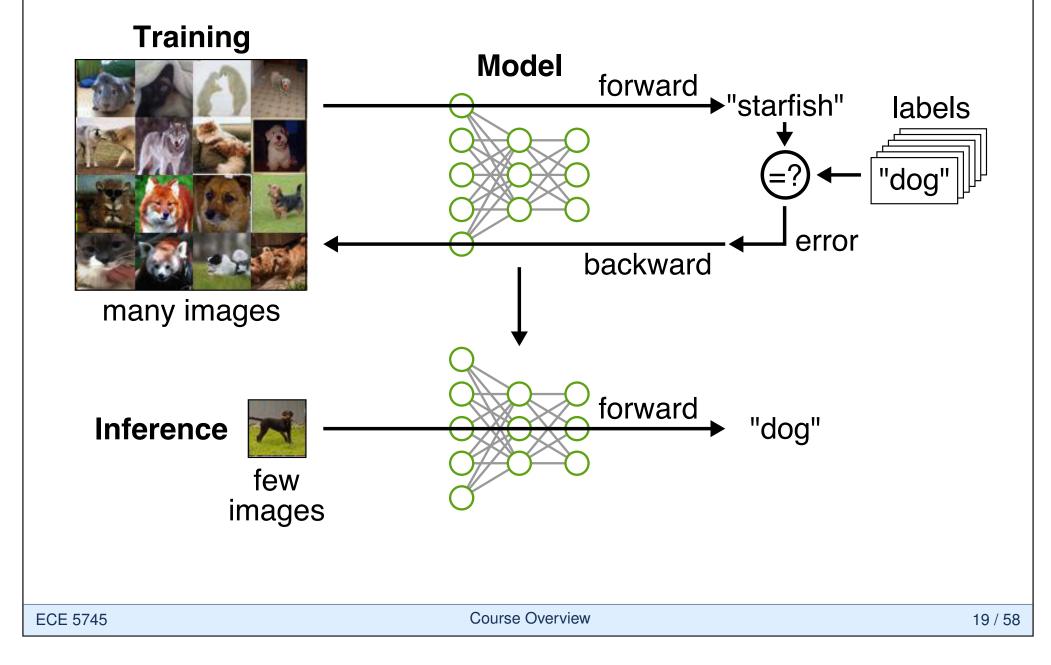

## Machine Learning: Training vs. Inference

ASIC Design Case Studies

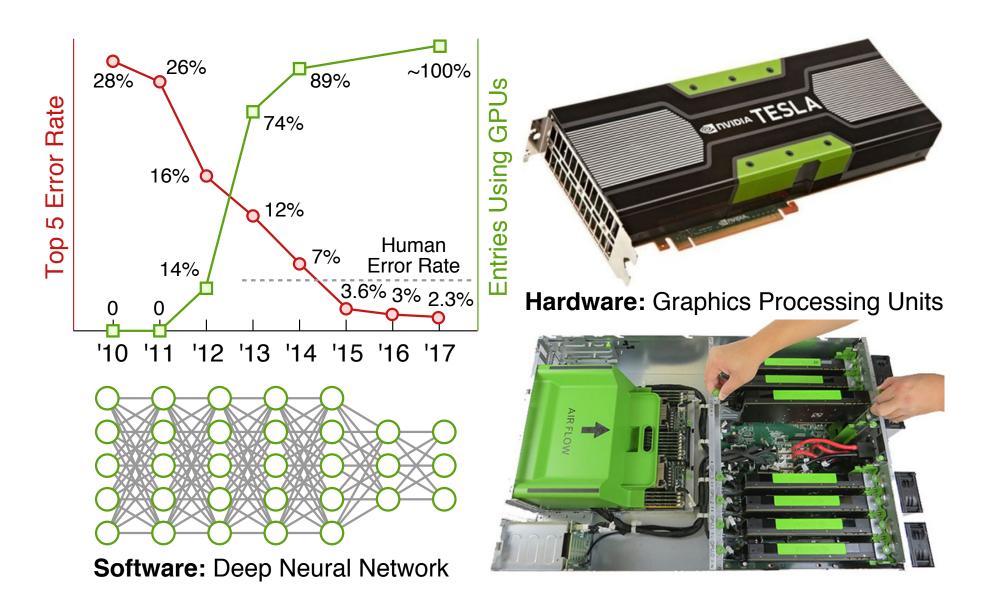

### ImageNet Large-Scale Visual Recognition Challenge

ASIC Design Case Studies

### Accelerators for Machine Learning in the Cloud

#### **NVIDIA DGX Hopper**

- Graphics processor specialized just for accelerating machine learning

- Available as part of a complete system with both the software and hardware designed by NVIDIA

#### Google TPU v4

- Custom chip specifically designed to accelerate Google's TensorFlow C++ library

- Tightly integrated into Google's data centers

#### **Microsoft Catapult**

- Custom FPGA board for accelerating Bing search and machine learning

- Accelerators developed with/by app developers

- Tightly integrated into Microsoft data center's and cloud computing platforms

ASIC Design Case Studies

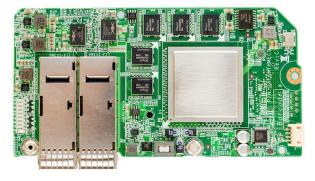

## Accelerators for Machine Learning at the Edge

#### **Amazon Echo**

- Developing AI chips so Echo line can do more on-board processing

- Reduces need for round-trip to cloud

- Co-design the algorithms and the underlying hardware

#### **Facebook Oculus**

- Starting to design custom chips for Oculus VR headsets

- Significant performance demands under strict power requirements

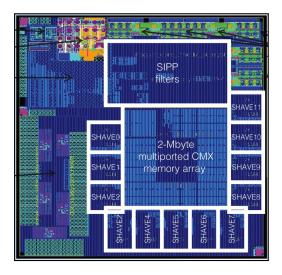

#### **Movidius Myriad 2**

# Top-five software companies are all building custom accelerators

Facebook: w/ Intel, in-house AI chips

Amazon: Echo, Oculus, networking chips

Microsoft: Hiring for AI chips

Google: TPU, Pixel, convergence

Apple: SoCs for phones and laptops

Chip startup ecosystem for machine learning accelerators is thriving!

#### Graphcore

- Nervana

- Cerebras

- Wave Computing

- Horizon Robotics

- Cambricon

- DeePhi

- Esperanto

- SambaNova

- Eyeriss

- Tenstorrent

- Mythic

- ThinkForce

- Groq

- Lightmatter

Activity

The field of complex digital ASIC design is experiencing a disruptive sea change and has a critical choice:

A technological fallow period

A golden age of ASIC design

This course will help you appreciate and possibly contribute to this golden age!

### **Course Motivation: Comp Arch Research Perspective**

ASIC Design Case Studies

### **Cross-Layer Interaction is Critical**

Architecture-level researchers need to quantitatively understand area, cycle time, and energy trade-offs to create new architectures for the accelerator era

> Cross-layer interaction can generate some of the most exciting research ideas!

### **Course Motivation: Circuits Research Perspective**

ASIC Design Case Studies

### **Cross-Layer Interaction is Critical**

Circuit-level researchers need to appreciate the system-level context for their circuits

Cross-layer interaction can generate some of the most exciting research ideas!

Technology

# **Complex Digital ASIC Design**

- Course goal, structure, motivation

- What is the goal of the course?

- Why should students want to take this course?

- > How is the course structured?

- Activity: Evaluation of Integer Multiplier

- ASIC Design Case Studies

- Example design-space exploration

- Example real ASIC chips

Course Goal, Structure, Motivation

Activity

ASIC Design Case Studies

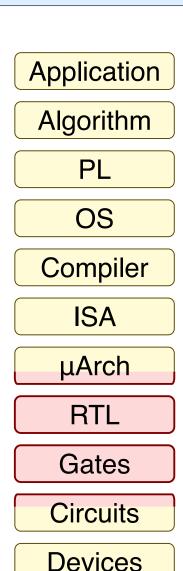

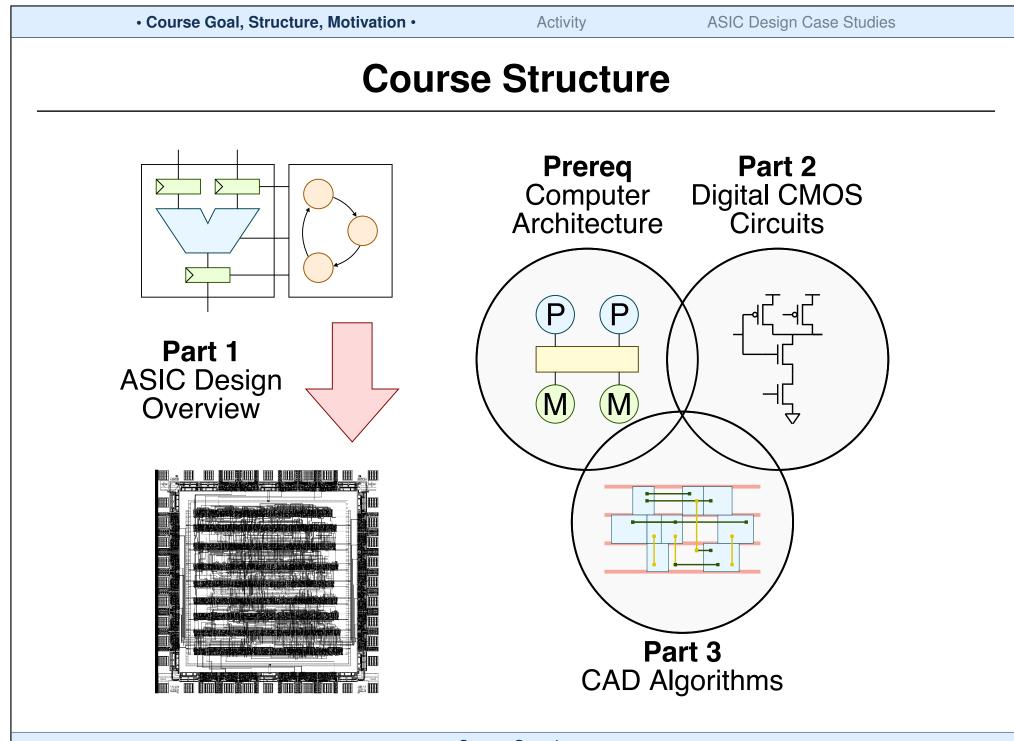

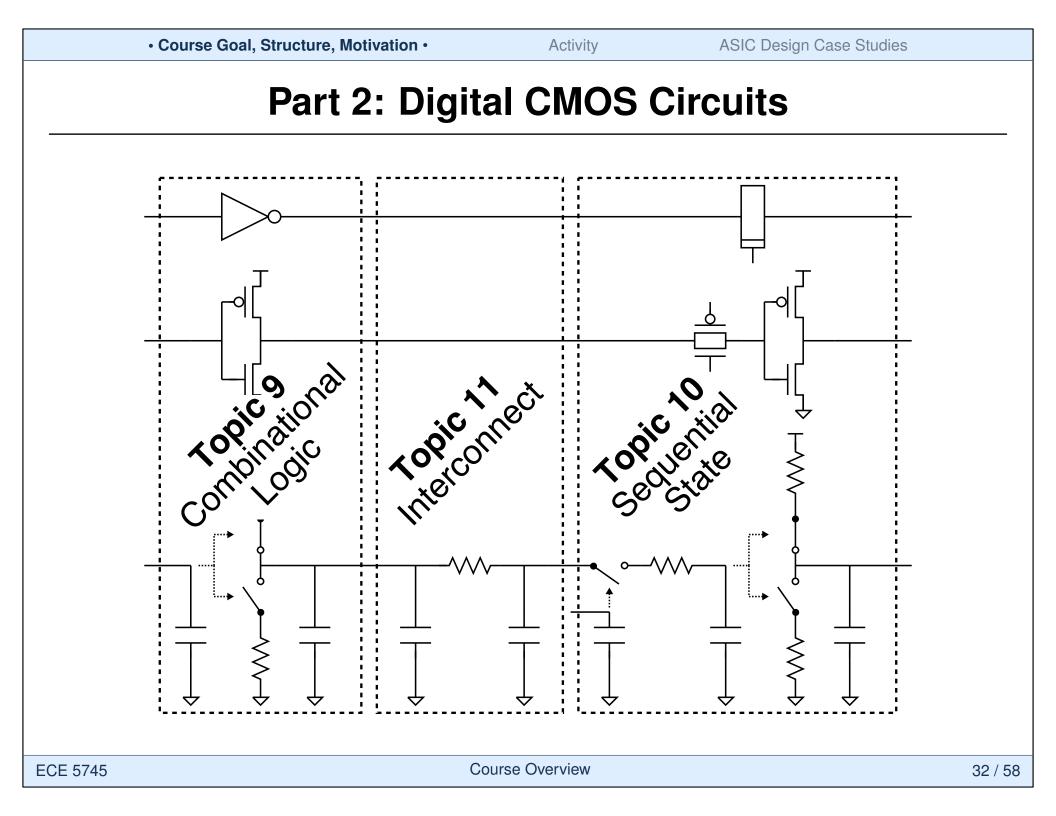

### **Part 1: ASIC Design Overview**

Course Goal, Structure, Motivation •

Activity

ASIC Design Case Studies

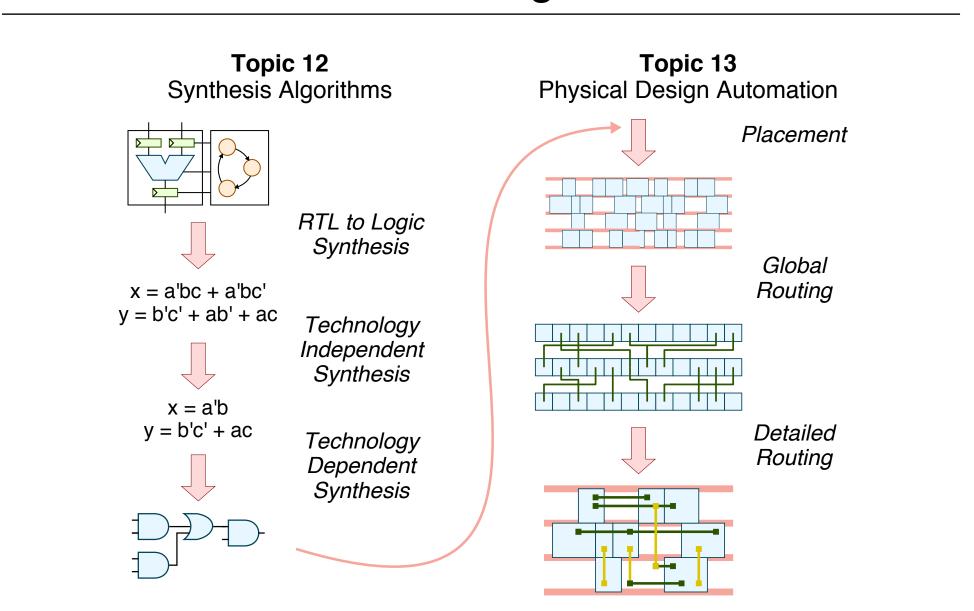

## Part 3: CAD Algorithms

ASIC Design Case Studies

#### **Five-Week Design Project**

Technology

# **Complex Digital ASIC Design**

- Course goal, structure, motivation

- What is the goal of the course?

- Why should students want to take this course?

- > How is the course structured?

- Activity: Evaluation of Integer Multiplier

- ASIC Design Case Studies

- Example design-space exploration

- Example real ASIC chips

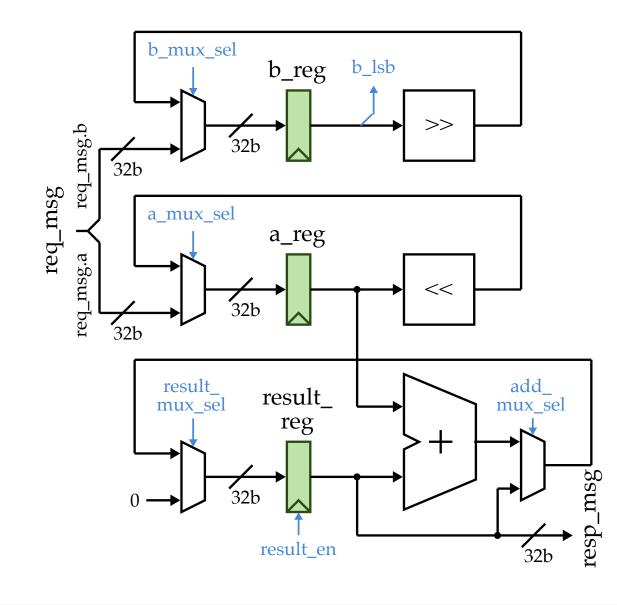

### **Fixed-Latency Iterative Multiplier Datapath**

# **Complex Digital ASIC Design**

- Course goal, structure, motivation

- What is the goal of the course?

- Why should students want to take this course?

- How is the course structured?

- Activity: Evaluation of Integer Multiplier

- ASIC Design Case Studies

- > Example design-space exploration

- > Example real ASIC chips

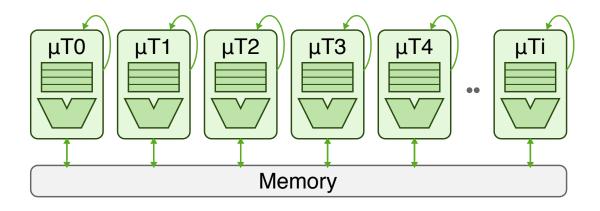

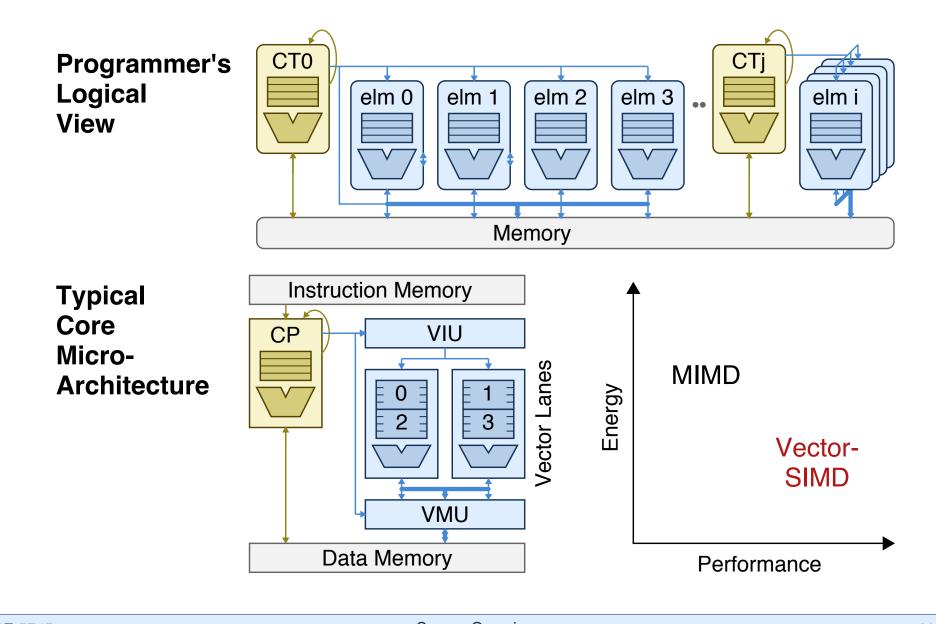

### Scalar Processors with Multithreading

**Programmer's** Logical View

### **Vector-SIMD Processors**

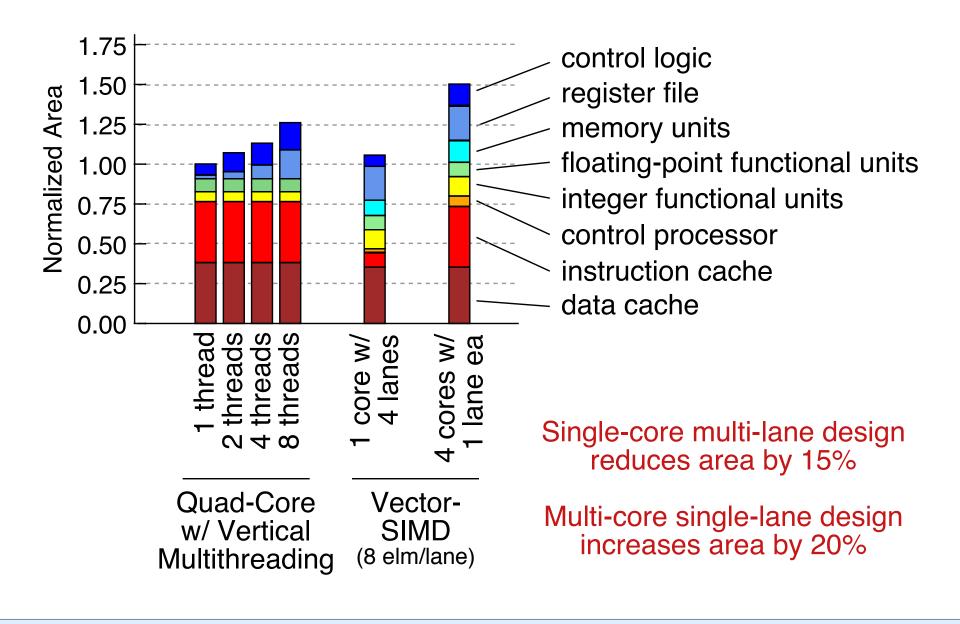

### **Quantitative Area Evaluation**

| Control Processor    | 8.1%  |

|----------------------|-------|

| Vector Register File | 56.9% |

| Vector Integer ALUs  | 9.7%  |

| Vector FPUs          | 9.4%  |

| Vector Memory Units  | 7.6%  |

| Other                | 8.3%  |

$810 \ \mu m$

### **Quantitative Area Evaluation**

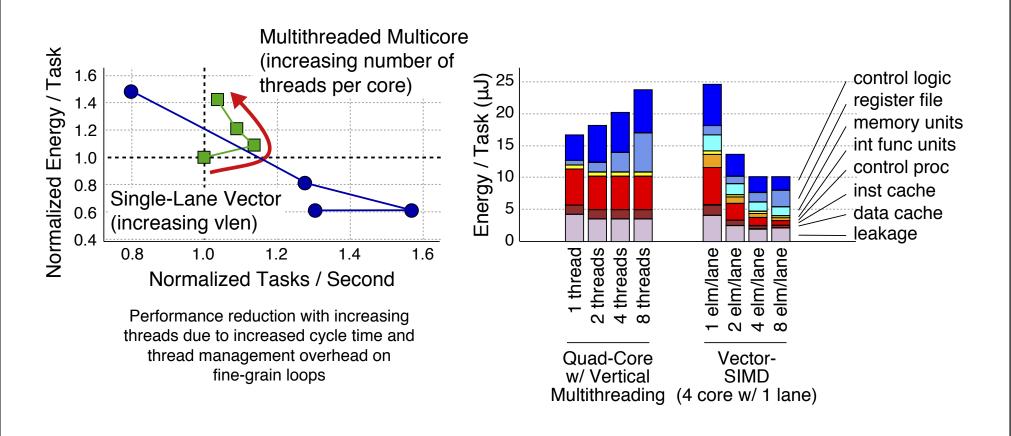

### **Quantitative Performance and Energy Evaluation**

# **Complex Digital ASIC Design**

- Course goal, structure, motivation

- What is the goal of the course?

- Why should students want to take this course?

- How is the course structured?

- Activity: Evaluation of Integer Multiplier

- ASIC Design Case Studies

- Example design-space exploration

- Example real ASIC chips

Activity Course Goal, Structure, Motivation ASIC Design Case Studies Simple RISC Processor ASIC INUE -----**SP** Control 11111=1111 1111 -1101 SP Datapath **SP Regfile** 1111 RAM Interface m ARE RE-Controller VCO IIII 4 RAM RAM 1111 alith **Subbank** Subbank i en re-SILL (2KB) (2KB) hmie 300 A RI I HEI IS Inn Di ROM RAM RAM Subbank **Subbank** -100 (2KB) (2KB) A REAL RE RARE 11011 51111 IN RUUTA NUTANA NUT -

### Simple RISC Processor ASIC

| $\begin{array}{c}1&1&1&1&1\\1&2&3&4&5\\0&0&0&0&0\\0&0&0&0&0\end{array}$ | ) 0 (          | ) () | 1<br>9<br>0<br>0 | 2<br>0<br>0<br>0 | 2<br>1<br>0<br>0 | 2<br>2<br>0<br>0 | 2<br>3<br>0<br>0 | 2<br>4<br>0<br>0 | 2<br>5<br>0<br>0 | 2<br>6<br>0 | 2<br>7<br>0<br>0 | 2<br>8<br>0<br>0 | 2<br>9<br>0<br>0 | 3<br>0<br>0<br>0 | 3<br>1<br>0<br>0 | 3<br>2<br>0<br>0 | 3<br>3<br>0<br>0 | 3<br>4<br>0<br>0 | 3<br>5<br>0 | 3<br>6<br>0 | 3<br>7<br>0<br>0 | 3<br>8<br>0<br>0 | 3<br>9<br>0<br>0 | 4<br>0<br>0<br>0 |

|-------------------------------------------------------------------------|----------------|------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|-------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|-------------|-------------|------------------|------------------|------------------|------------------|

| 750<br>740                                                              | ••••           | :    | :                | :                | :                | :                | :                | :                | :                | :           | :                | :                | :                | :                | :                | :                | :                | :                | :           | :           | :                | :                | :                | :                |

| 730<br>720                                                              |                | :    | :                | :                | :                | :                | :                | :                | :                | :           | :                | :                | :                | :                | :                | :                | :                | :                | :           | :           | :                | :                | :                | :                |

| 710<br>700                                                              |                |      | :                | :                | :                | :                | ÷                | :                | :                | :           | :                | :                | :                | :                | :                | :                | :                | :                | ÷           | *           | *                | *                | *                | :                |

| 690<br>680                                                              | • •            | •    | ÷                | ÷                | ÷                | ÷                | ÷                | ÷                | ÷                | ÷           | ÷                | ÷                | ÷                | ÷                | ÷                | ÷                | •<br>*           | •<br>*           | *           | *           | *                | *<br>*           | *                | :                |

| 670<br>660                                                              | •              | •    | •                | •                | •                | •                | •                | •                | •                | •           | •                | •                | •                | •                | •                | *                | *                | *                | *           | *           | *                | *                | •                | •                |

| 650<br>640                                                              | • • •          |      | :                | :                | :                | :                | :                | :                | :                | :           | :                | :                | :                | •<br>*<br>*      | •<br>*<br>*      | *                | *                | *                | *           | *           | *                | *                | •<br>*<br>*      | :                |

| 630                                                                     | • •            |      | :                | :                | :                | :                | ÷                | :                | :                | :           | :                | •<br>•<br>*      | *                | *                | *                | *                | *                | *                | *           | *           | *                | *                | •                | :                |

| 620<br>610                                                              |                |      | :                | :                | :                | :                | :                | :                | :                | :           | *                |                  | *                | *                | *                | *                | *                | *                | *           | *           | *                | *                | *                | :                |

| 600<br>590                                                              | ·              |      | :                | :                | :                | :                | :                | :                | :                | *           | *                | *                | *                | *                | *                | *                | *                | *                | *           | *           | *                | *<br>*           | *                | :                |

| 580<br>570                                                              | •              | •    | ÷                | :                | ÷                | ÷                | ÷                | ÷                | *                | *           | *                | *                | *                | *                | *                | *                | *                | *                | *           | *           | *                | *<br>*           | •<br>*           | •<br>*           |

| 560<br>550                                                              |                | •    | ·                | ·                | ·                | ·                | •<br>*           | •                | *                | *           | *                | *                | *                | *                | *                | *                | *                | *                | *           | *           | *                | *                | *                | *                |

| 540<br>530                                                              | • •            |      | :                | :                | :                | :                | *                | *                | *                | *           | *                | *                | *                | *                | *                | *                | *                | *                | *           | *           | *                | *                | •                | •<br>*<br>*      |

| 520                                                                     |                |      | :                | :                | :                | •<br>*<br>*      | *                | *                | *                | *           | *                | *                | *                | *                | *                | *                | *                | *                | *           | *           | *                | *                | *                | *                |

| 510<br>500                                                              | • : :          |      | :                | :                | *                | *                | *                | *                | *                | *           | *                | *                | *                | *                | *                | *                | *                | *                | *           | *           | *                | *                | *                | *                |

| 490<br>480                                                              |                |      | :                | *                | *                | *                | *                | *                | *                | *           | *                | *                | *                | *                | *                | *                | *                | *                | *           | *           | *<br>*           | *<br>*           | *                | *<br>*           |

| 470<br>460                                                              | •              | •    | *                | *                | *<br>*           | *<br>*           | *                | *<br>*           | *                | *           | *                | *                | *                | *                | *                | *                | *                | *                | *           | *           | *                | *<br>*           | *                | *<br>*           |

| 450<br>440                                                              | ••••           | •    | *                | *                | *                | *                | *                | *                | *                | *           | *                | *                | *                | *                | *                | *                | *                | *                | *           | *           | *                | *                | *                | *<br>*           |

| 430<br>420                                                              |                | *    | *                | *                | *                | *                | *                | *                | *                | *           | *                | *                | *                | *                | *                | *                | *                | *                | *           | *           | *                | *                | *                | *<br>*           |

| 410                                                                     | . *            | * *  | *                | *                | ~<br>*<br>*      | *                | *<br>*           | *                | *                | *           | *                | *                | *                | *                | *                | *                | *                | *<br>*           | *<br>*      | *           | *                | *                | *                | *                |

| 400                                                                     | * *            | * *  | *                | *                | Ŧ                | Ŧ                | Ŧ                | Ŧ                | *                | Ŧ           | *                | Ŧ                | *                | *                | *                | *                | *                | Ŧ                | Ŧ           | Ŧ           | Ŧ                | Ŧ                | *                | *                |

| 380 · · · · · · · · · · · · · · · · · · ·                               | * *            | * *  | *                | *                |                  |                  |                  |                  |                  |             |                  |                  |                  |                  |                  |                  |                  |                  |             |             |                  |                  |                  |                  |

| 360<br>350 *                                                            | * * *          | * *  | *                | *<br>*           |                  |                  |                  |                  |                  |             |                  |                  |                  |                  |                  |                  |                  |                  |             |             |                  |                  |                  |                  |

| 340 *<br>330 *                                                          |                | * *  | *                | *                |                  |                  |                  |                  |                  |             |                  |                  |                  |                  |                  |                  |                  |                  |             |             |                  |                  |                  |                  |

| 320 * *<br>310 * *                                                      | ***            |      | *                | *                |                  |                  |                  |                  |                  |             |                  |                  |                  |                  |                  |                  |                  |                  |             |             |                  |                  |                  |                  |

| 300 * *                                                                 | * * *          |      | *                | *                |                  |                  |                  |                  |                  |             |                  |                  |                  |                  |                  |                  |                  |                  |             |             |                  |                  |                  |                  |

| 280 * * *                                                               | * * *          | * *  | *                | *                |                  |                  |                  |                  |                  |             |                  |                  |                  |                  |                  |                  |                  |                  |             |             |                  |                  |                  |                  |

| 270 * * *<br>260 * * *                                                  |                |      | *                | *                |                  |                  |                  |                  |                  |             |                  |                  |                  |                  |                  |                  |                  |                  |             |             |                  |                  |                  |                  |

| 250 * * *<br>240 . * * * *                                              | * * *<br>* * * |      | *                | *<br>*           |                  |                  |                  |                  |                  |             |                  |                  |                  |                  |                  |                  |                  |                  |             |             |                  |                  |                  |                  |

| 230 . * * * *<br>220 . * * * *                                          | ***            |      | *                | *                |                  |                  |                  |                  |                  |             |                  |                  |                  |                  |                  |                  |                  |                  |             |             |                  |                  |                  |                  |

| 210 . * * * *                                                           | * * *          | * *  | *                | *                |                  |                  |                  |                  |                  |             |                  |                  |                  |                  |                  |                  |                  |                  |             |             |                  |                  |                  |                  |

| 200 * * * * *<br>190 * * * * *                                          | * * *          | * *  | *                | *                |                  |                  |                  |                  |                  |             |                  |                  |                  |                  |                  |                  |                  |                  |             |             |                  |                  |                  |                  |

| 180 * * * * *                                                           | * * *          | * *  | *                | *                |                  |                  |                  |                  |                  |             |                  |                  |                  |                  |                  |                  |                  |                  |             |             |                  |                  |                  |                  |

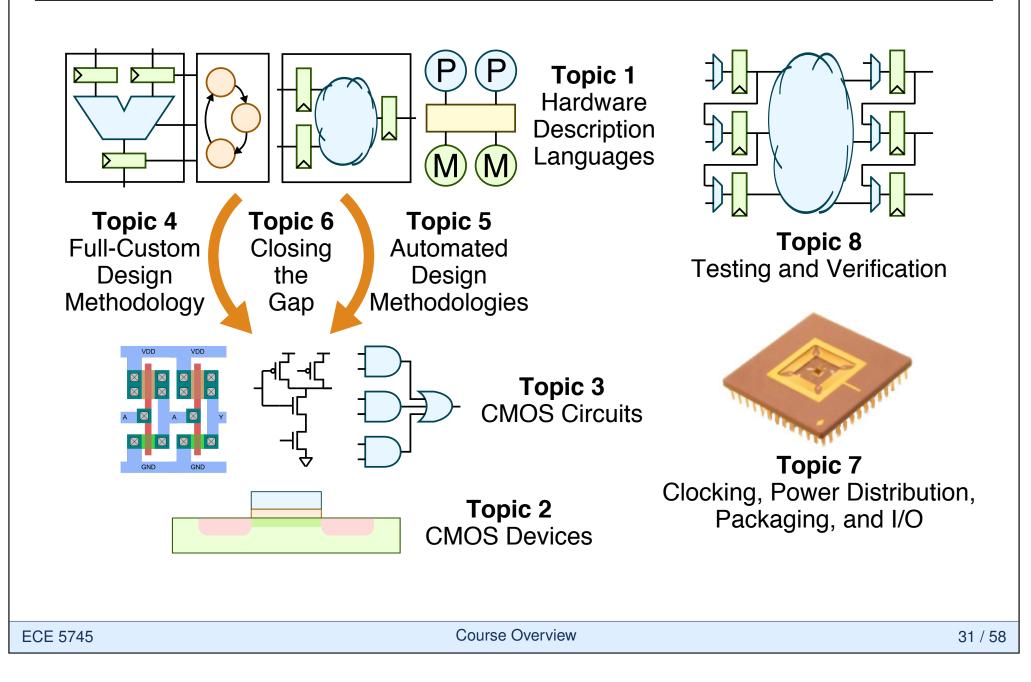

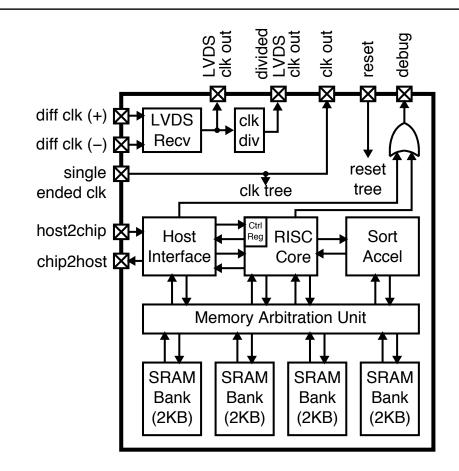

- RISC processor w/ 8 KB SRAM

- ► TSMC 0.18 µm process

- ▶ 1.7 × 2.1 mm

- 610K Transistors

- 450 MHz at 1.8 V

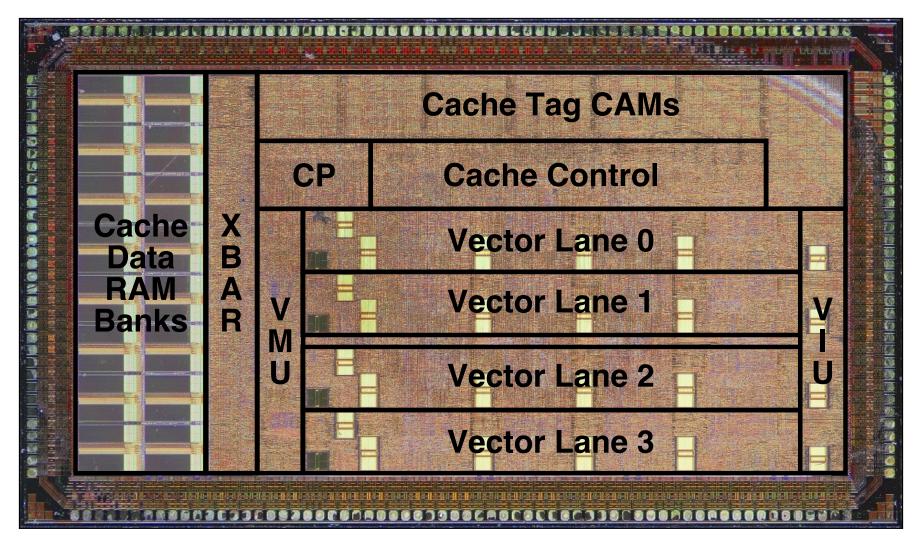

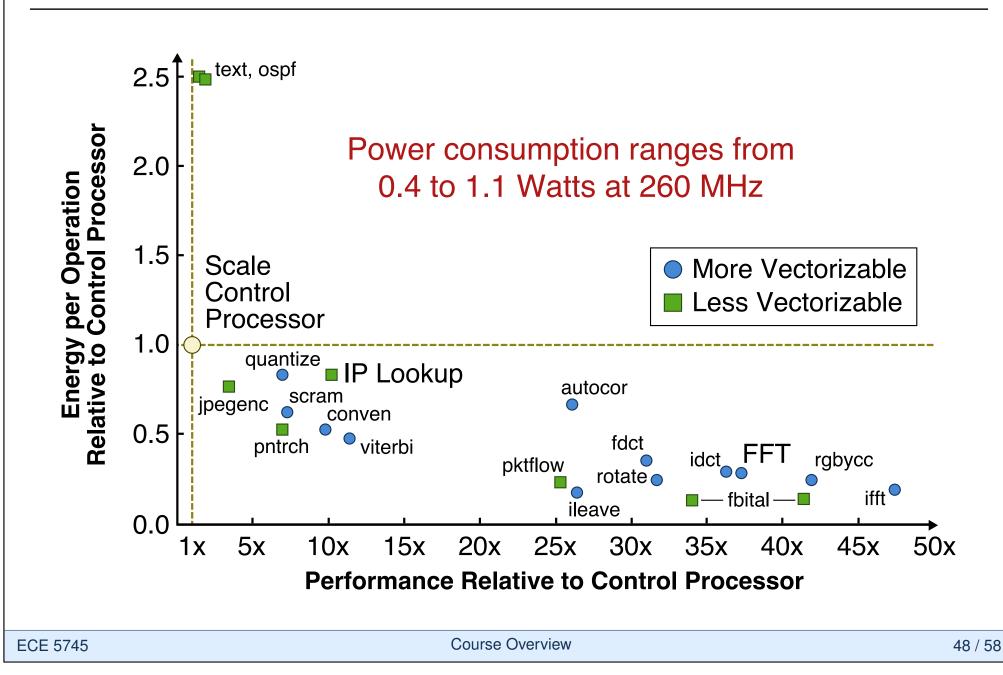

### **Scale Vector-Thread Processor ASIC**

### Scale Vector-Thread Processor ASIC

TSMC 0.18µm • 7.14 Million Transistors • 16.6 mm<sup>2</sup> Core Area

### **Scale Energy vs. Performance Results**

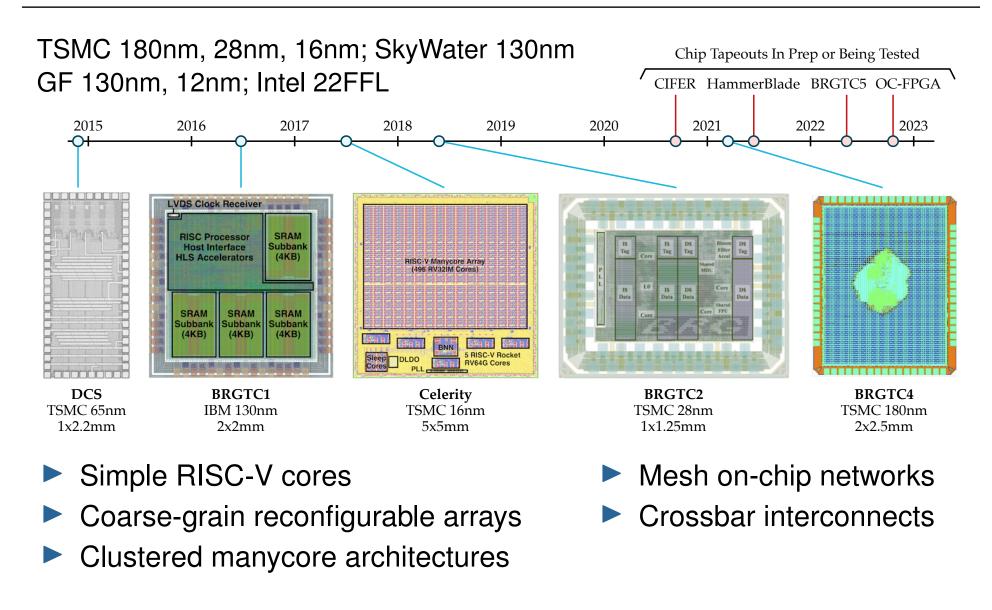

### **Batten Research Group Test Chips**

Course Goal, Structure, Motivation

#### ASIC Design Case Studies

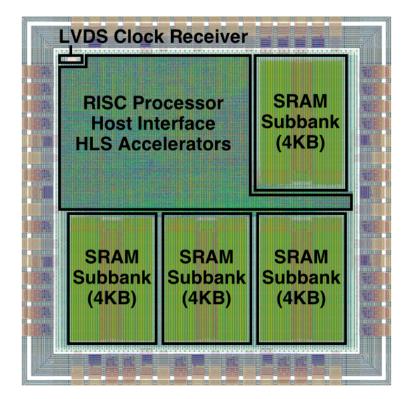

### BRG Test Chip 1 (2016)

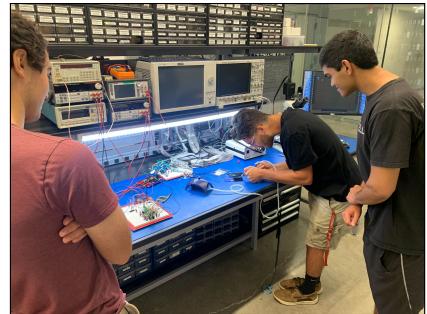

### **Post-Silicon Evaluation Strategy**

The testing platform enables running small test programs on BRGTC1 to compare the performance and energy of pure-software kernels versus the HLS-generated sorting accelerator

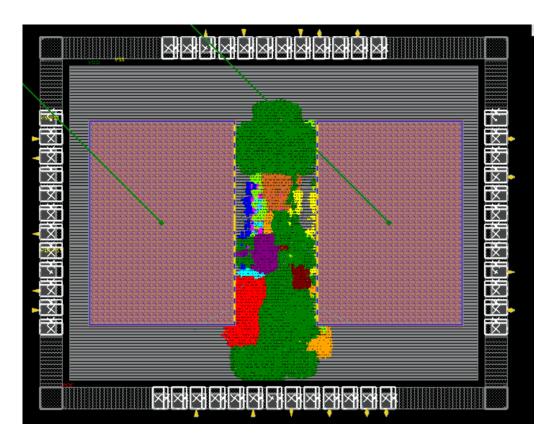

### **Taped-out Layout for BRGTC1**

2x2mm 1.3M transistors in IBM 130nm RISC processor, 16KB SRAM HLS-generated accelerators Static Timing Analysis Freq. @ 246 MHz

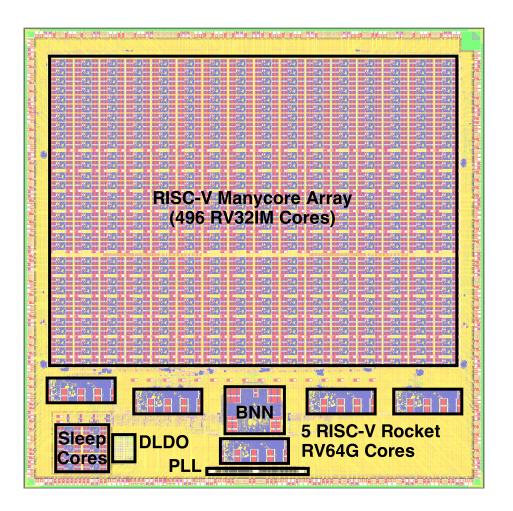

## **Celerity System-on-Chip Overview (2017)**

Target Workload: High-Performance Embedded Computing

- $5 \times 5$ mm in TSMC 16 nm FFC

- 385 million transistors

- 511 RISC-V cores

- 5 Linux-capable Rocket cores

- 496-core tiled manycore

- 10-core low-voltage array

- 1 BNN accelerator

- 1 synthesizable PLL

- 1 synthesizable LDO Vreg

- 3 clock domains

- 672-pin flip chip BGA package

- 9-months from PDK access to tape-out

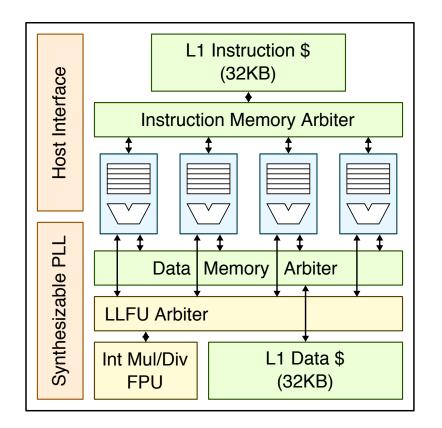

## BRG Test Chip 2 (2018)

Block Diagram 4xRV32IMAF cores with "smart" sharing L1\$/LLFU, synthesizable PLL

I\$ D\$ Bloom D\$ I\$ Filter Tag Tag Tag Tag Core Accel Shared MDU LO Core IS IS D\$ D\$ Data Data Data Data Shared Core FPU Core

Taped-out Layout for BRGTC2

2x2mm, 1.2M-trans, IBM 130nm Static Timing Analysis Freq. @ 500MHz

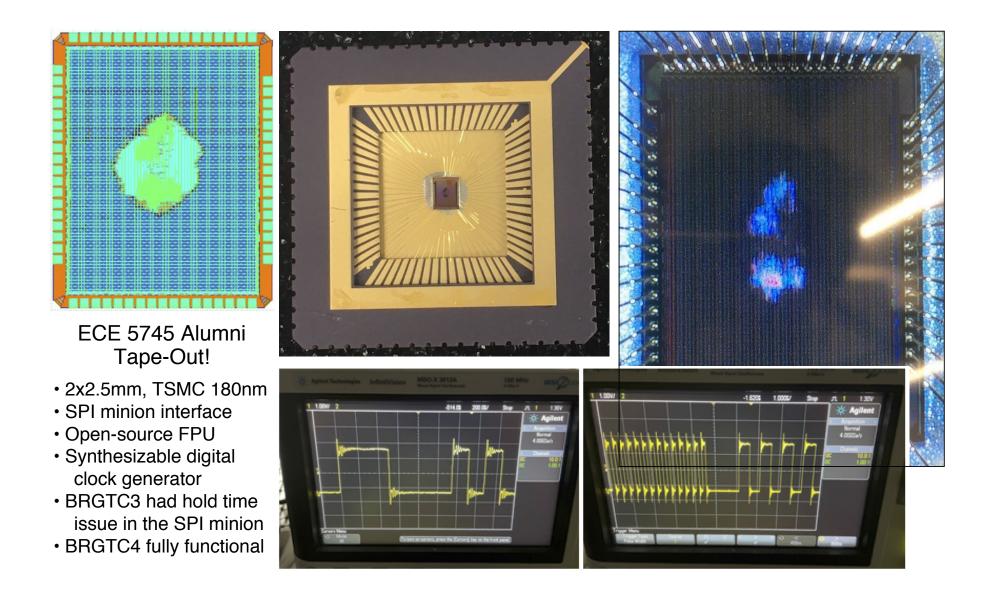

### BRG Test Chip 3/4 (2020/2021)

ECE 5745

### ECE 5745 Teaching Tapeout (2022)

- First teaching tapeout in 10 years

- SkyWater 130nm through efabless

- Taped out using completely open-source EDA tools!

- Four student projects

- CRC32 checksum unit implemented using C++ HLS

- Latency insensitive synthesizable memory implemented in PyMTL3

- 2x2 systolic array multiplier implemented in SystemVerilog

- Greatest common divisor unit implemented in SystemVerilog

- Each unit included dedicated SPI interface

Course Goal, Structure, Motivation

Activity

ASIC Design Case Studies

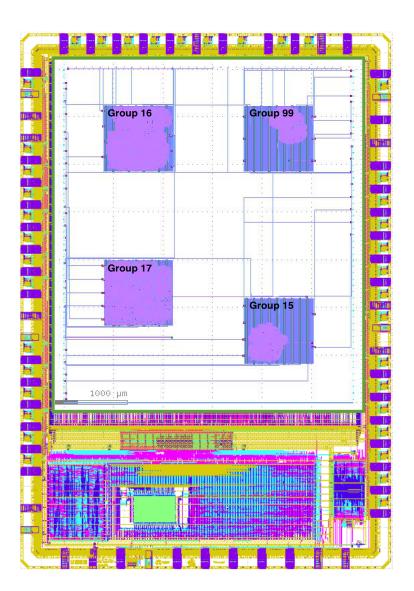

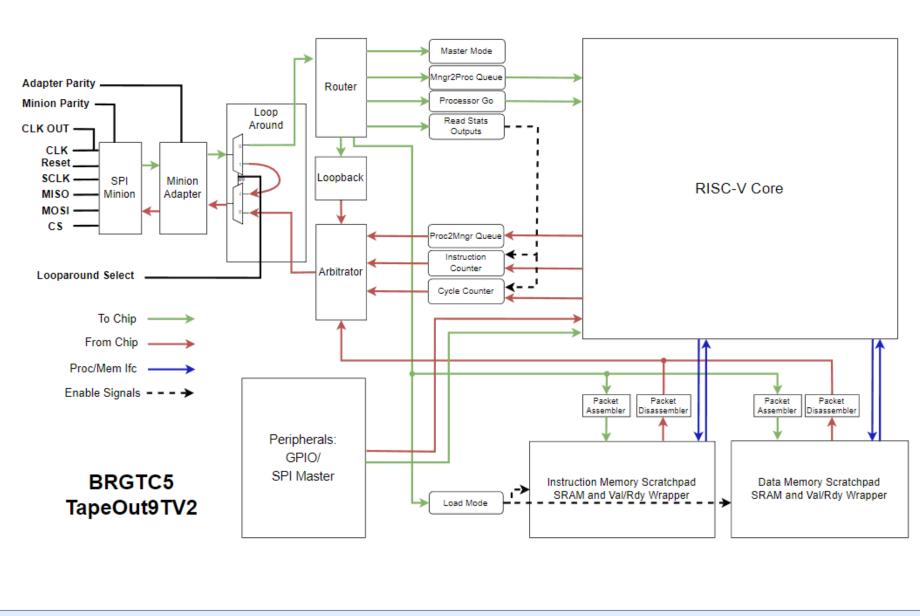

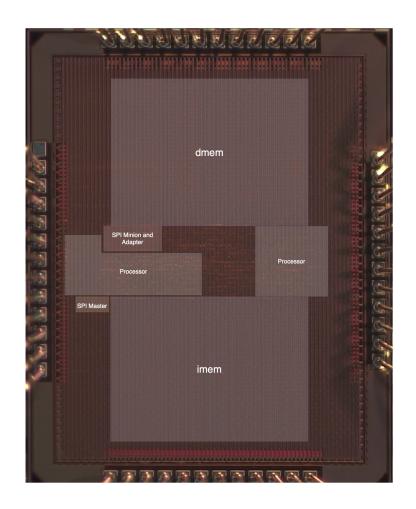

### **BRG Test Chip #5 (2022)**

RISC-V RV32IM core with 32-KB of SRAM SPI minion for config; SPI master and GP I/O for peripherals 2x2.5mm, TSMC 180nm 100% done using PyMTL3 by ECE 5745 Alumni

### **BRG Test Chip #5 (2022)**

### **BRG Test Chip #5 (2022)**

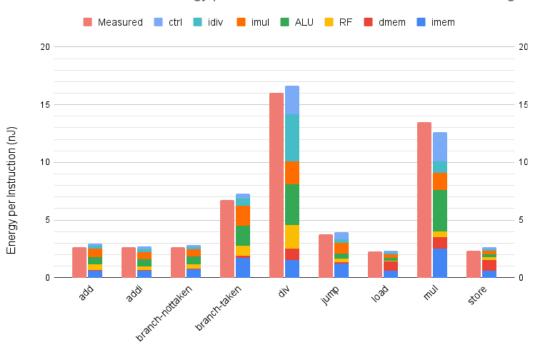

Simulated and Measured Energy per Instruction at 66 MHz and 3.3 V Core Voltage

## **Take-Away Points**

- Complex digital ASIC design is the process of quantitatively exploring the area, cycle time, execution time, and energy trade-offs of general-purpose and application-specific designs using automated standard-cell CAD tools and then to transform the most promising design to layout ready for fabrication

- Course provides an excellent foundation for students interested in pursuing a career in in industry development of ASICs or can provide useful experience with cross-layer interaction for students interested in pursuing research in computer architecture or circuits