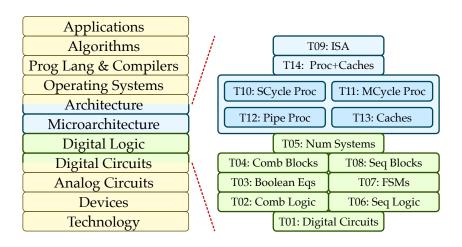

# ECE 2300 Digital Logic and Computer Organization Fall 2025

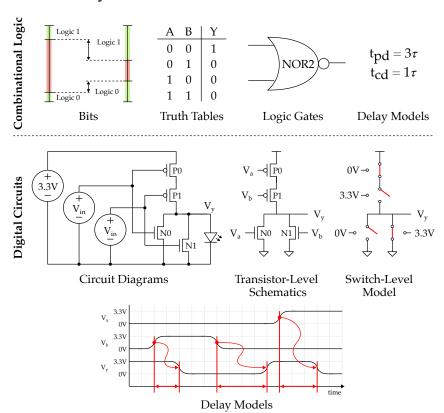

# **Topic 2: Combinational Logic**

School of Electrical and Computer Engineering Cornell University

revision: 2025-09-04-10-50

| 1 | From Voltages to Bits                          | 3  |

|---|------------------------------------------------|----|

| 2 | From Digital Circuits to Truth Tables          | 4  |

| 3 | From Truth Tables to Combinational Logic Gates | 9  |

|   | 3.1. Primitive Gate Sets                       | 13 |

| 4 | Combinational Gate-Level Networks              | 16 |

| 5 | Combinational Logic Timing Analysis            | 20 |

|   | 5.1. Combinational Logic Gates Timing          | 21 |

|   | 5.2. Combinational Gate-Level Network Timing   | 23 |

|   | 5.3. Combinational Gate-Level Network Timing   | 24 |

| 6 | Verilog Modeling of Combinational Logic        | 27 |

|   | 6.1. Modeling Logic Gates in Verilog           | 28 |

|   | 6.2. Modeling Gates-Level Netlists in Verilog  | 29 |

|   | 6.3. Modeling Delays in Verilog                | 32 |

| 7 | Summary of Abstractions                        | 33 |

Copyright © 2025 Christopher Batten. All rights reserved. This handout was prepared by Prof. Christopher Batten at Cornell University for ECE 2300 / ENGRD 2300 Digital Logic and Computer Organization. Download and use of this handout is permitted for individual educational non-commercial purposes only. Redistribution either in part or in whole via both commercial or non-commercial means requires written permission.

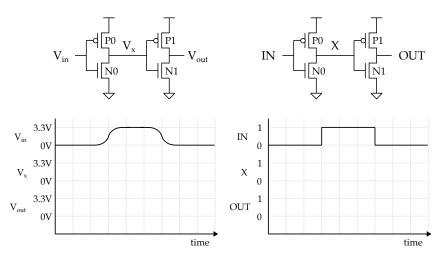

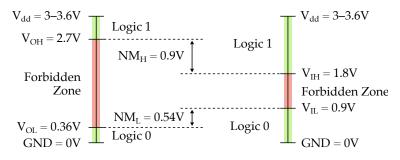

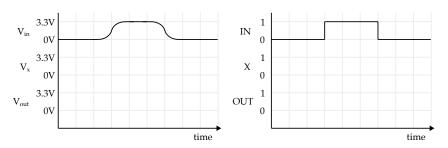

### 1. From Voltages to Bits

- Abstract 3.3V to be logic 1, and abstract 0V to be logic 0

- Enables ignoring specific voltage levels at higher abstraction levels

- Can now interpret wires as representing binary digits (bits)

- Include noise margins to make our circuits more robust

#### Output of First Inverter

#### Input of Second Inverter

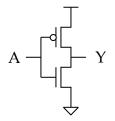

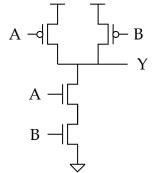

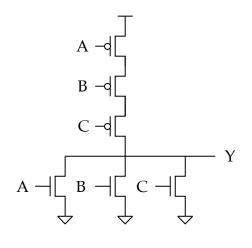

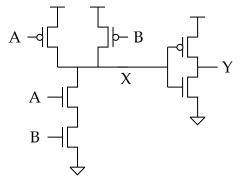

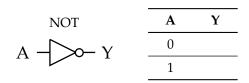

### 2. From Digital Circuits to Truth Tables

- A *truth table* specifies the output values for specific input values, with one row for every possibly combination of input values

- Let's start by deriving truth tables from digital circuits

| $V_a$ | V <sub>y</sub> |

|-------|----------------|

| 0V    |                |

| 3.3V  |                |

|       |                |

| A | Y |

|---|---|

| 0 |   |

| 1 |   |

| Va   | $V_b$ | $V_y$ |

|------|-------|-------|

| 0V   | 0V    |       |

| 0V   | 3.3V  |       |

| 3.3V | 0V    |       |

| 3.3V | 3.3V  |       |

| A | В | Y |

|---|---|---|

| 0 | 0 |   |

| 0 | 1 |   |

| 1 | 0 |   |

| 1 | 1 |   |

| A | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 |   |

| 0 | 0 | 1 |   |

| 0 | 1 | 0 |   |

| 0 | 1 | 1 |   |

| 1 | 0 | 0 |   |

| 1 | 0 | 1 |   |

| 1 | 1 | 0 |   |

| 1 | 1 | 1 |   |

| A | В | Х | Y |

|---|---|---|---|

| 0 | 0 |   |   |

| 0 | 1 |   |   |

| 1 | 0 |   |   |

| 1 | 1 |   |   |

#### • Now let's derive digital circuits from truth tables

| A | В | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

| A | В | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

| A | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

|   |   |   |   |

| A | В | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

|   |   |   | _ |

# 3. From Truth Tables to Combinational Logic Gates

$$\begin{array}{c}

A \longrightarrow \\

B \longrightarrow \\

\end{array}$$

$$\begin{array}{c} A \longrightarrow \\ B \longrightarrow \\ \end{array} \longrightarrow Y$$

| A | В | Y |

|---|---|---|

| 0 | 0 |   |

| 0 | 1 |   |

| 1 | 0 |   |

| 1 | 1 |   |

| A | В | Y |

|---|---|---|

| 0 | 0 |   |

| 0 | 1 |   |

| 1 | 0 |   |

| 1 | 1 |   |

| A | В | Y |

|---|---|---|

| 0 | 0 |   |

| 0 | 1 |   |

| 1 | 0 |   |

| 1 | 1 |   |

$$\begin{array}{c}

\text{NOR} \\

\text{A} \\

\text{B}

\end{array}$$

|   | ANOR |

|---|------|

| A | - N  |

| В |      |

**YNIOR**

| A | В | Y |

|---|---|---|

| 0 | 0 |   |

| 0 | 1 |   |

| 1 | 0 |   |

| 1 | 1 |   |

|   |   |   |

| A | В | Y |

|---|---|---|

| 0 | 0 |   |

| 0 | 1 |   |

| 1 | 0 |   |

| 1 | 1 |   |

|   |   |   |

| Α | В | Y |

|---|---|---|

| 0 | 0 |   |

| 0 | 1 |   |

| 1 | 0 |   |

| 1 | 1 |   |

|   |   |   |

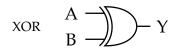

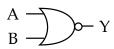

Derive the truth table for the above gate-level network. Verify it matches the truth table for an XOR gate.

| A | В | Х | W | Z | Y |

|---|---|---|---|---|---|

| 0 | 0 |   |   |   |   |

| 0 | 1 |   |   |   |   |

| 1 | 0 |   |   |   |   |

| 1 | 1 |   |   |   |   |

XNOR

$$\begin{pmatrix} A \\ B \end{pmatrix} \longrightarrow \begin{pmatrix} Y \\ B \end{pmatrix} \longrightarrow \begin{pmatrix} Y \\ B \end{pmatrix}$$

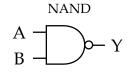

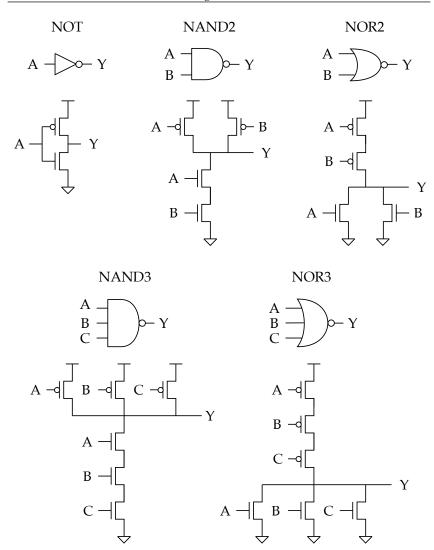

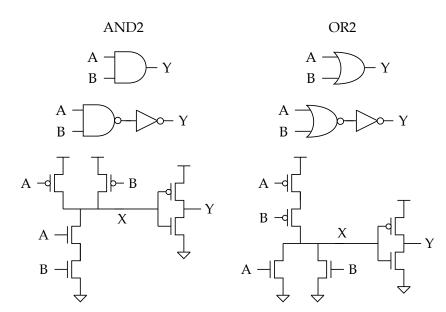

#### 3.1. Primitive Gate Sets

| • | Can implement a logic gate using other logic gates which can then |

|---|-------------------------------------------------------------------|

|   | be implemented again using more logic gates (e.g., XNOR)          |

| • | Can implement a logic gate using many different combinations of |

|---|-----------------------------------------------------------------|

|   | other logic gates                                               |

| • | = lowest level "atomic" logic gates which                             |

|---|-----------------------------------------------------------------------|

|   | are not implemented in terms of any other logic gates but are instead |

|   | implemented using digital circuits                                    |

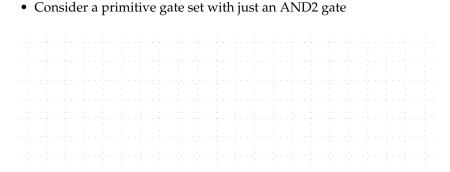

### **Incomplete Primitive Gate Sets**

• This is an *incomplete* primitive gate set since it is not possible to use this gate set to implement any other logic gate

#### Universal Primitive Gate Sets

- Consider a primitive gate set with just a NAND2 gate

- This is an *universal* primitive gate set since it is possible to use this gate set to implement any other logic gate

- A primitive gate set with just a NOR2 is also a universal

- It is inefficient (both in terms of area and timing) to implement all other logic gates just using NAND2 or NOR2 gates

#### **Maximal Primitive Gate Sets**

- Consider a primitive gate set with the following

- NOT gate

- n-input AND, n-input NAND gate

- n-input OR, n-input NOR gate

- n-input XOR, n-input XNOR gate

- AOI21, AOI22 gate (and-or-inverting)

- OAI12, OAI22 gate (or-and-inverting)

- Multiplexors, half-adders, full-adders

- Flip-flops, latches

- It is very efficient (both in terms of area and timing) to use a large primitive gate set

- It is difficult to understand how more complex gates work if we treat them as a block box implemented using digital circuits

#### **ECE 2300 Primitive Gate Set**

- The course will use a primitive gate set with the following

- NOT gate

- n-input AND, n-input NAND gate

- n-input OR, n-input NOR gate

- n-input XOR, n-input XNOR gate

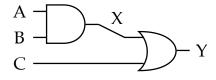

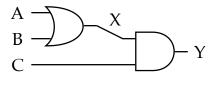

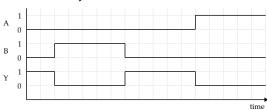

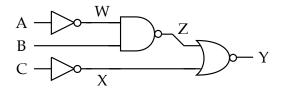

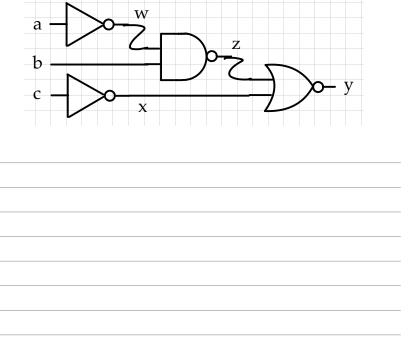

#### 4. Combinational Gate-Level Networks

- A *gate-level network* is a collection of logic gates connected by wires

- Let's start by deriving truth tables from gate-level networks

**Gate-Level Network**

| A | В | С | X | Y |

|---|---|---|---|---|

| 0 | 0 | 0 |   |   |

| 0 | 0 | 1 |   |   |

| 0 | 1 | 0 |   |   |

| 0 | 1 | 1 |   |   |

| 1 | 0 | 0 |   |   |

| 1 | 0 | 1 |   |   |

| 1 | 1 | 0 |   |   |

1

1

1

**Truth Table**

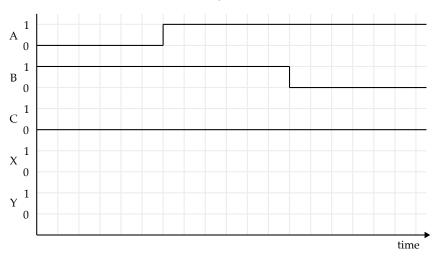

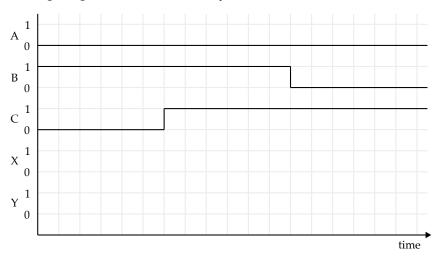

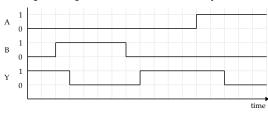

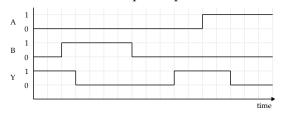

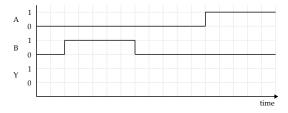

Timing Diagram (assume zero delay model)

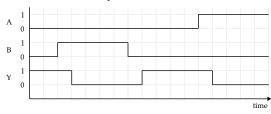

**Gate-Level Network**

#### **Truth Table**

| A | В | С | X | Y |

|---|---|---|---|---|

| 0 | 0 | 0 |   |   |

| 0 | 0 | 1 |   |   |

| 0 | 1 | 0 |   |   |

| 0 | 1 | 1 |   |   |

| 1 | 0 | 0 |   |   |

| 1 | 0 | 1 |   |   |

| 1 | 1 | 0 |   |   |

| 1 | 1 | 1 |   |   |

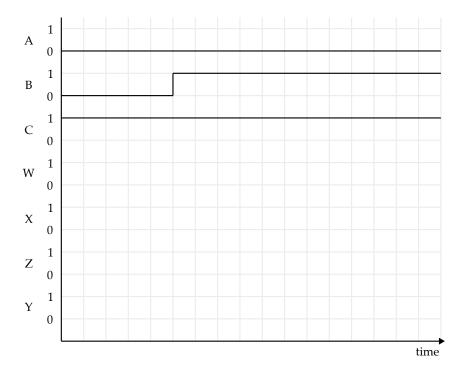

### Timing Diagram (assume zero delay model)

### • Now let's derive gate-level networks from truth tables

Gate-Level Network

| Truth Table |   |   |

|-------------|---|---|

| A           | В | Y |

| 0           | 0 | 1 |

| 0           | 1 | 0 |

| 1           | 0 | 1 |

| 1           | 1 | 1 |

Twith Table

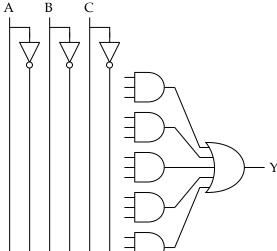

#### Truth Table

|   | A | В | C | Y |

|---|---|---|---|---|

|   | 0 | 0 | 0 | 0 |

|   | 0 | 0 | 1 | 1 |

|   | 0 | 1 | 0 | 0 |

|   | 0 | 1 | 1 | 1 |

|   | 1 | 0 | 0 | 0 |

|   | 1 | 0 | 1 | 1 |

| ′ | 1 | 1 | 0 | 1 |

|   | 1 | 1 | 1 | 1 |

|   |   |   |   |   |

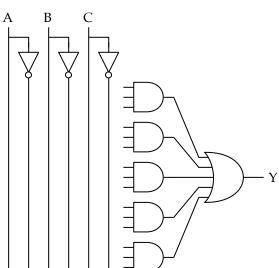

#### **Gate-Level Network**

#### **Truth Table**

| A | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

|   |   |   |   |

### 5. Combinational Logic Timing Analysis

• Use abstract time units ( $\tau$ ) instead of picoseconds (ps)

- Recall from previous topic that many delay models are possible

- Zero delay models

- Constant delay models

- Input-dependent constant delay models

- Transition- and input-dependent constant delay models

- Load-, transition-, and input-dependent linear delay models

- Slew-, load-, transition-, and input-dependent linear delay models

- Non-linear delay models

# 5.1. Combinational Logic Gates Timing

$$t =$$

#### • Constant Delay Model

#### • Input-Dependent Constant Delay Model

$$t_{A \to Y} =$$

$t_{B \to Y} =$

### • Transition- and Input-Dependent Constant Delay Model

$$t_{A \to Y,hl} =$$

$$t_{A \to Y.lh} =$$

$$t_{B \to Y,hl} =$$

$$t_{B \to Y, lh} =$$

#### **Propagation and Contamination Delay Modeling**

- We want to improve the accuracy of the constant delay model but without the more complex of delay models

- $\underline{\hspace{1cm}}$  ( $t_{pd}$ ) = maximum time from when input changes until the output reaches final value

- \_\_\_\_\_ ( $t_{cd}$ ) = minimum time from when input changes until any output changes its value (might not be final value)

- Constant Delay Model (with propagation and contamination delays)

$$t_{pd} = t_{cd} =$$

• Input-Dependent Constant Delay Model (with propagation and contamination delays)

$$t_{pd,A \to Y} =$$

$t_{cd,A \to Y} =$

$t_{pd,B \to Y} =$

$t_{cd,B \to Y} =$

Propagation and contamination delay modeling is conservative but simplifies our analysis

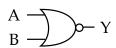

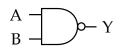

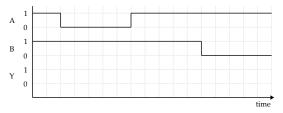

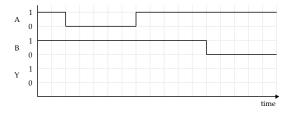

### Complete the timing diagrams for a NAND gate.

• Constant Delay Model (with propagation and contamination delays)

$$t_{pd} = 2\tau$$

$t_{cd} = 1\tau$

• Input-Dependent Constant Delay Model (with propagation and contamination delays)

$$t_{pd,A \to Y} = 2\tau$$

$t_{cd,A \to Y} = 1\tau$

$t_{pd,B \to Y} = 1.5\tau$

$t_{cd,B \to Y} = 1\tau$

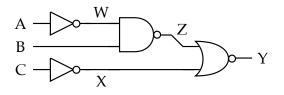

# 5.2. Combinational Gate-Level Network Timing

- Apply our delay model to all gates in a gate-level network

- Analyze all paths from every input to every output in network

- \_\_\_\_\_ = longest path through a gate-level network (only consider propagation delays!)

- \_\_\_\_\_ = shortest path through a gate-level network (only consider contamination delays!)

# 5.3. Combinational Gate-Level Network Timing

| Gate  | $t_{pd}$ | $t_{cd}$ |

|-------|----------|----------|

| NOT   | $1\tau$  | $1\tau$  |

| NAND2 | $2\tau$  | $1\tau$  |

| NOR2  | 3τ       | $1\tau$  |

| Gate  | $t_{pd}$ | $t_{cd}$ |

|-------|----------|----------|

| NOT   | $1\tau$  | $1\tau$  |

| NAND2 | 2τ       | 1τ       |

| NOR2  | $3\tau$  | $1\tau$  |

| Path                                                 | Propagation<br>Delay | Contamination<br>Delay |

|------------------------------------------------------|----------------------|------------------------|

|                                                      |                      | _                      |

| $B \rightarrow NAND2 \rightarrow NOR2 \rightarrow Y$ |                      |                        |

|                                                      |                      |                        |

- Which path is the critical path?

- Which path is the short path?

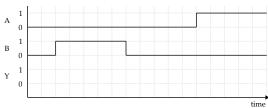

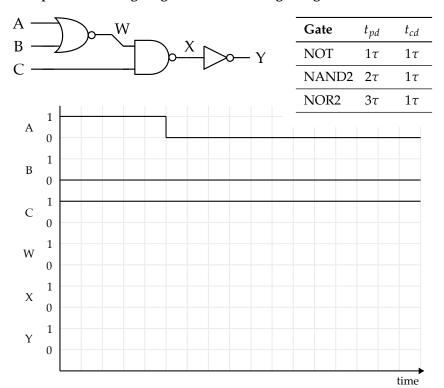

### Complete the timing diagram and table for given gate-level network.

| Path | Propagation<br>Delay | Contamination<br>Delay |

|------|----------------------|------------------------|

|      |                      |                        |

|      |                      |                        |

|      |                      |                        |

## 6. Verilog Modeling of Combinational Logic

| • | Verilog is not a programming language (PL), it is a hardware |

|---|--------------------------------------------------------------|

|   | description language (HDL)                                   |

| • | = portion of the language that                               |

|   | models real hardware                                         |

| • | = portion of the language that does                          |

|   | not model real hardware but is instead used to test hardware |

- We will simulate designs implemented in Verilog to verify their functionality

- We will *synthesize* designs implemented in Verilog to map them to real hardware in the lab using a field programmable gate array

### **Verilog Datatypes**

- All signals in Verilog can have one of four values:

- Logic 1

- Logic 2

- X (undefined value or don't care about specific value)

- Z (floating)

It is critical to always keep in mind the *real hardware* you are trying to model using Verilog!

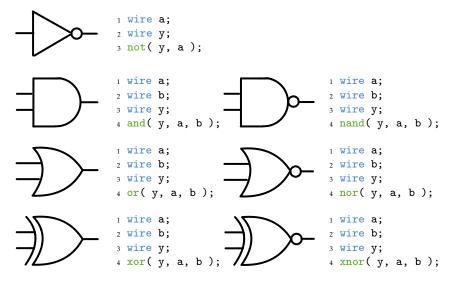

# 6.1. Modeling Logic Gates in Verilog

- Declare wires using wire

- Instantiate logic gate primitives (e.g., not, and)

- List wires to connect them to inputs and outputs, output is first

- Logic gates with more than two inputs are allowed

- What if one of the inputs is X?

- Consider an AND gate

| A | В | Y |

|---|---|---|

| 0 | Χ |   |

| 1 | Х |   |

| Х | 0 |   |

| Х | 1 |   |

| Х | Х |   |

|   |   |   |

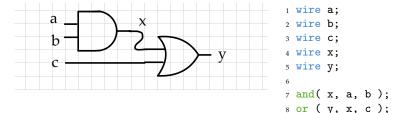

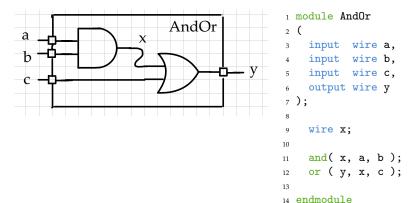

## 6.2. Modeling Gates-Level Netlists in Verilog

#### **Defining Hardware Modules in Verilog**

https://www.edaplayground.com/x/KjwN

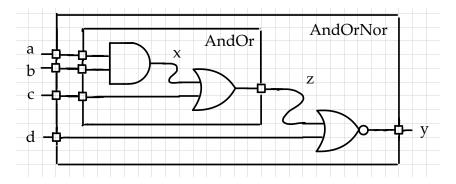

#### **Instantiating Hardware Modules in Verilog**

```

1 module AndOrNor

(

input wire a,

3

input wire b,

4

input wire c,

5

input wire d,

output wire y

);

8

wire z;

10

11

AndOr and_or

12

13

.a (a),

14

.b (b),

15

.c (c),

16

.y (z)

17

);

18

19

or( y, z, d );

20

21

22 endmodule

```

**Implement the following gate-level network in Verilog.** Match the coding style from the previous examples.

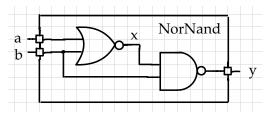

# 6.3. Modeling Delays in Verilog

| Gate  | $t_{pd}$ | $t_{cd}$ |

|-------|----------|----------|

| NOT   | $1\tau$  | $1\tau$  |

| NAND2 | 2τ       | 1τ       |

| NOR2  | 3τ       | 1τ       |

```

1 module NorNand

2 (

3   input wire a,

4   input wire b,

5   output wire y

6 );

7

8   wire x;

9

10   nor #(3) ( x, a, b );

11   nand #(2) ( y, x, b );

12

13 endmodule

```

https://www.edaplayground.com/x/Hpjf

# 7. Summary of Abstractions