Cornell University Computer Systems Laboratory

# An Open-Source Python-Based Hardware Generation, Simulation, and Verification Framework

Shunning Jiang, Christopher Torng, Christopher Batten

Computer Systems Laboratory School of Electrical and Computer Engineering Cornell University

## Outline

- Introduction

- PyMTL features

- PyMTL use cases

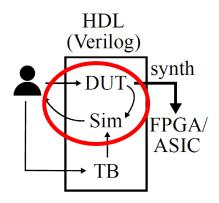

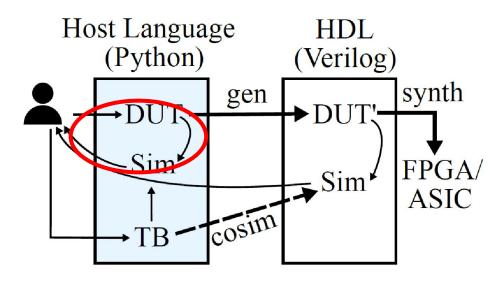

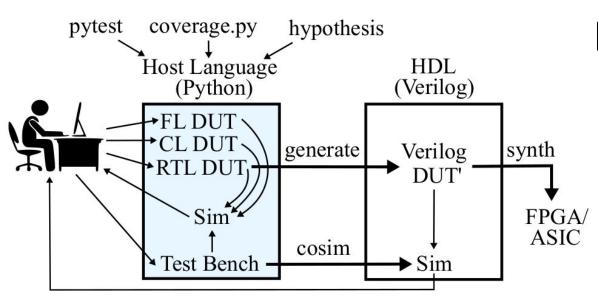

#### The Traditional Flow

- \* HDL: hardware description language

- \* DUT: design under test

- \* TB: test bench

- \* synth: synthesis

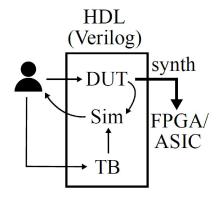

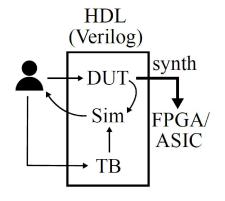

# Traditional hardware description language

- Example: Verilog

- ✓ Fast edit-debug-sim loop

- Single language for design and testbench

- X Difficult to parameterize

- X Require specific ways to build powerful testbench

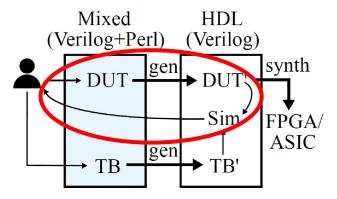

#### Hardware Preprocessing Frameworks (HPF)

Traditional hardware description language

- Example: Verilog

- ✓ Fast edit-debug-sim loop

- Single language for design and testbench

- X Difficult to parameterize

- X Require specific ways to build powerful testbench

Hardware preprocessing framework (HPF) - Example: Genesis2

- Better parametrization with insignificant coding style change

- X Multiple languages create "semantic gap"

- X Still not easy to build powerful testbench

#### Hardware Generation Frameworks (HGF)

Mixed

(Verilog+Perl)

DUT

TΒ

Traditional hardware description language

- Example: Verilog

- ✓ Fast edit-debug-sim loop

- Single language for design and testbench

- X Difficult to parameterize

- X Require specific ways to build powerful testbench

#### Hardware preprocessing framework (HPF) - Example: Genesis2

gen

gen

HDL

(Verilog)

DUT

Sim'

TB'

synth

FPGA/

ASIC

- Better parametrization with insignificant coding style change

- X Multiple languages create "semantic gap"

- X Still not easy to build powerful testbench

#### Hardware generation framework (HGF) - Example: Chisel

- Powerful parametrization

- Single language for design

- X Slower edit-debug-sim loop

- X Yet still difficult to build powerful testbench (can only generate simple testbench)

#### PyMTL is an Hardware Generation and Simulation framework

- Powerful parametrization

- Single language for design and testbench

- Use host language for verification

- Easy to create highly parameterized generators

#### PyMTL framework

## Outline

- Introduction

- **PyMTL** features

- PyMTL use cases

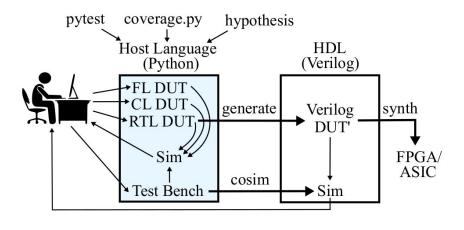

## Eight features that make PyMTL productive

- Multi-level modeling

- Method-based interfaces

- Highly parametrized static elaboration

- Analysis and transform passes

- Pure-Python simulation

- Property-based random testing

- Python/SystemVerilog integration

- Fast simulation speed

## Multi-level modeling

- Functional-level modeling: quickly building reference model and testbench

- Cycle-level modeling: design space exploration

- Register-transfer-level modeling: generating hardware

Example: Accelerator designers only want to implement the accelerator in RTL. How about cache and processor to do end-to-end testing?

#### Highly parametrized static elaboration

7

9

PyMTL embeds the DSL into Python, so the hardware designs can use full Python's expressive power to construct hardware.

```

1 class Register( Model ):

1 class Mux( Model ):

def __init__(s, nbits):

2 def __init__(s, nbits, nports):

type = Bits( nbits )

s.in_ = InPort[nports](nbits)

3

s.sel = InPort (bw(nports))

s.in_ = InPort ( type ) 4

s.out = OutPort( type ) 5

s.out = OutPort(nbits)

6

@s.tick_rtl

7

Qs.combinational

def seq_logic():

8

def comb_logic():

s.out.next = s.in

s.out.value = s.in [s.sel]

9

```

```

1 class MuxReg( Model ):

def __init__( s, nbits=8, nports=4 ):

s.in_ = [ InPort( nbits ) for x in range( nports ) ]

s.sel = InPort ( bw( nports ) )

s.out = OutPort( nbits )

s.reg_ = Register( nbits )

s.mux = Mux

( nbits )

9

s.connect( s.sel, s.mux.sel )

10

for i in range( nports ):

11

s.connect( s.in_[i], s.mux.in_[i] )

12

s.connect( s.mux.out, s.reg_.in_ )

13

s.connect( s.reg_.out, s.out

14

```

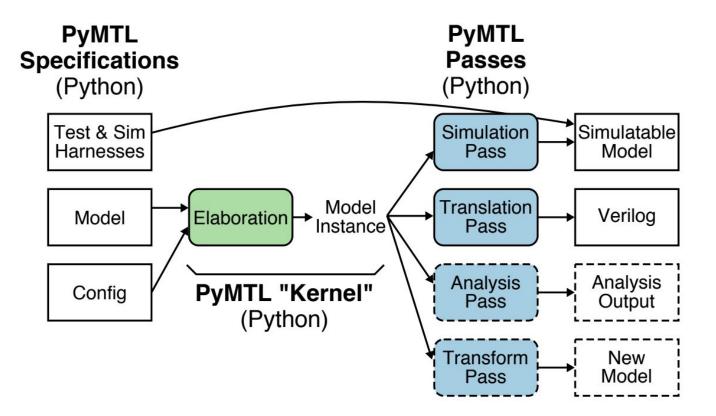

## PyMTL passes

PyMTL analysis/transform passes systematically traverse through the design and/or transform the module hierarchy by mutating the internal data structures.

```

# Analysis pass example:

1

# Get a list of processors with >=2 input ports

2

def count_pass( top ):

3

ret = []

for m in top.get_all_modules_filter(

5

lambda m: len( m.get_input_ports() ) >= 2 ):

6

if isinstance( m, AbstractProcessor ):

7

ret.append( m )

8

9

return m

```

```

# Transform pass example:

1

# Wrap every ctrl with CtrlWrapper

2

def debug_port_pass( top ):

3

for m in top.get_all_modules():

4

if m.get_full_name().startswith("ctrl"):

5

p = m.get_parent()

6

ctrl = p.delete_component( "ctrl" )

7

w = p.add_component( "ctrl_wrap", CtrlWrapper() )

8

new_ctrl = w.add_component( "ctrl", m )

9

10

. . .

< connect ports >

11

12

. . .

```

#### Property-based random testing

Since the simulation is just executing a piece of Python code, we can leverage **random testing frameworks that test Python software** for testing hardware.

- hypothesis

```

import hypothesis

1

from

hypothesis import strategies as st

2

3

@hypothesis.given(

x = st.integers(2, 100),

5

y = st.integers(2, 100),

6

src_delay = st.integers( 0, 20 ),

7

sink_delay = st.integers( 0, 20 ),

8

test_msgs = st.data() )

9

def test_dut_hypothesis( x, y, src_delay, sink_delay, test_msgs ):

10

11

hypothesis.assume( x + y \le 200 )

12

hypothesis.event( "Testing x=%d, y=%d" % (x, y) )

13

# compose_test_msg is another function that draws random numbers

14

# from hypothesis strategies.

15

msgs = test_msgs.draw( st.lists( compose_test_msg( x, y ),

16

min_size=1, max_size=32 ) )

17

18

run_dut_test( DUT(), msgs, x, y, src_delay, sink_delay, msgs )

19

```

## PyMTL/SystemVerilog integration

- PyMTL can import SystemVerilog and co-simulate it with the same Python test harness.

- PyMTL can also compose multiple PyMTL/SystemVerilog designs and translate the larger design into SystemVerilog.

```

# By default PyMTL imports module DUT of DUT.v

1

# in the same folder as the python source file.

2

class DUT( VerilogModel ):

3

def __init__( s ):

4

s.in_ = InPort (Bits32)

5

s.out = OutPort ( Bits32 )

6

7

# Connect top level ports of DUT

8

# to corresponding PyMTL ports

9

s.set_ports({

10

'clk' : s.clk,

11

'reset' : s.reset.

12

'in' : s.in_,

13

'out' : s.out,

14

})

15

```

#### Fast pure-Python simulation

With Mamba techniques, the next version of PyMTL gets an order of magnitude of speedup when simulating **in a pure-Python environment**.

- Design the framework from the ground up with a just-in-time compiler in mind

- Enhance the just-in-time compiler to recognize critical hardware constructs

|         | PyMTL                          | MyHDL        | PyRTL        | Migen | IVerilog     | CVS         | Mamba |

|---------|--------------------------------|--------------|--------------|-------|--------------|-------------|-------|

| Divider | 118K CPS                       | $0.8 \times$ | $2.2 \times$ | 0.03× | 0.6×         | 9.3×        | 20×   |

| 1-core  | 20K CPS                        | -            | -            | -     | $1 \times$   | 15×         | 16×   |

| 32-core | 118K CPS<br>20K CPS<br>360 CPS | -            | -            | -     | $1.8 \times$ | $25 \times$ | 12×   |

## Outline

- Introduction

- PyMTL features

- PyMTL use cases

- **PyMTL** in teaching: 400+ students across 2 universities

- PyMTL in research: four ISCA/MICRO papers use PyMTL

- PyMTL in silicon prototyping: three tape-outs, two of which completely use PyMTL

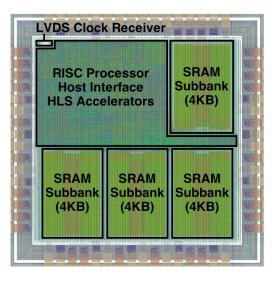

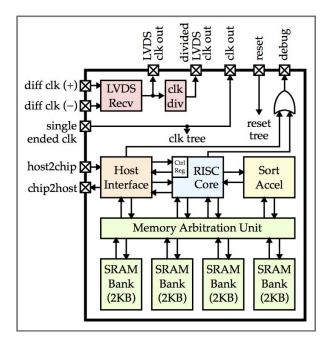

## PyMTL in Silicon Prototyping: BRGTC1 (2016)

- Fabricated in IBM 130nm

- 2mm x 2mm die, 1.2M transistor

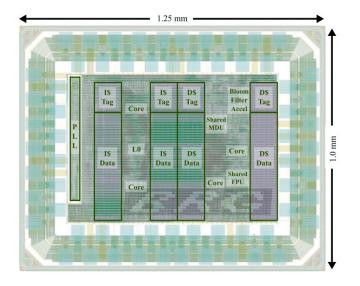

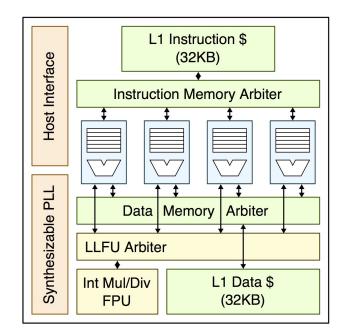

#### PyMTL in Silicon Prototyping: BRGTC2 (2018)

- Fabricated in TSMC 28nm

- 1mm x 1.25mm die, 6.7M transistor

- Quad-core in-order RV32IMAF

- Advertisement: our open-source modular VLSI build system used in this tapeout https://github.com/cornell-brg/alloy-asic

# PyMTL:

- Multi-level modeling

- Method-based interfaces

- Highly parametrized static elaboration

- Analysis and transform passes

- Pure-Python simulation

- Property-based random testing

- Python/SystemVerilog integration

- Fast simulation speed

We expect a new release in 2019.

PyMTL: https://github.com/cornell-brg/pymtl

Modular ASIC Build system: <u>https://github.com/cornell-brg/alloy-asic</u>