# Experiences Using a Novel Python-Based Hardware Modeling Framework for Computer Architecture Test Chips

### This Poster...

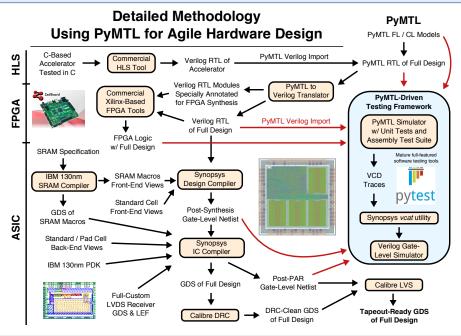

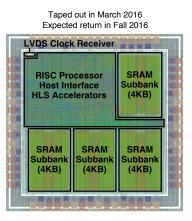

Describes a taped-out 2x2 mm 1.3M-transistor test chip in IBM 130nm designed and implemented using PyMTL, a novel Python-based hardware modeling framework

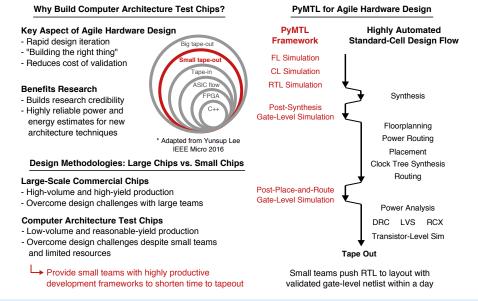

Goal of tapeout was to demonstrate the ability of this framework to enable Agile hardware design flows

#### PyMTL: A Unified Python-Based Framework for FL, CL, and RTL Modeling

- Functional-Level Modeling (FL)

- Behavior

### Cycle-Level Modeling (CL)

- Behavior

- Cycle-Approximate

- Analytical Area, Energy, Timing

#### Register-Transfer-Level Modeling (RTL)

- Behavior

- Cycle-Accurate Timing

- Gate-Level Area, Energy, Timing

### What Does PyMTL Enable?

- 1. Incremental refinement from algorithm to hardware implementation

- 2. Automated testing and integration of PyMTL-generated Verilog

3. Multi-level co-simulation of FL, CL, and RTL models

4. Construction of highly parameterized RTL chip generators

## **PyMTL for Computer Architecture Test Chips**

#### Cornell University

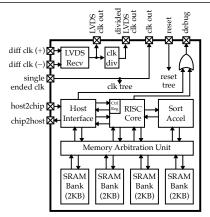

### PyMTL in Practice: BRG Test Chip 1

### **Testing Plans After Fabrication**

The testing platform enables running small test programs on BRGTC1 to compare the performance and energy of pure-software kernels versus the HLS-generated sorting accelerator

### Taped-out Layout for BRGTC1

2x2mm 1.3M transistors in IBM 130nm RISC processor, 16KB SRAM HLS-generated accelerators Static Timing Analysis Freq. @ 246 MHz