# A New Era of Open-Source Hardware

**Christopher Batten**

Computer Systems Laboratory Electrical and Computer Engineering Cornell University

On Sabbatical as a Visiting Scholar SLICE Laboratory University of California, Berkeley

Cornell University

**Christopher Batten**

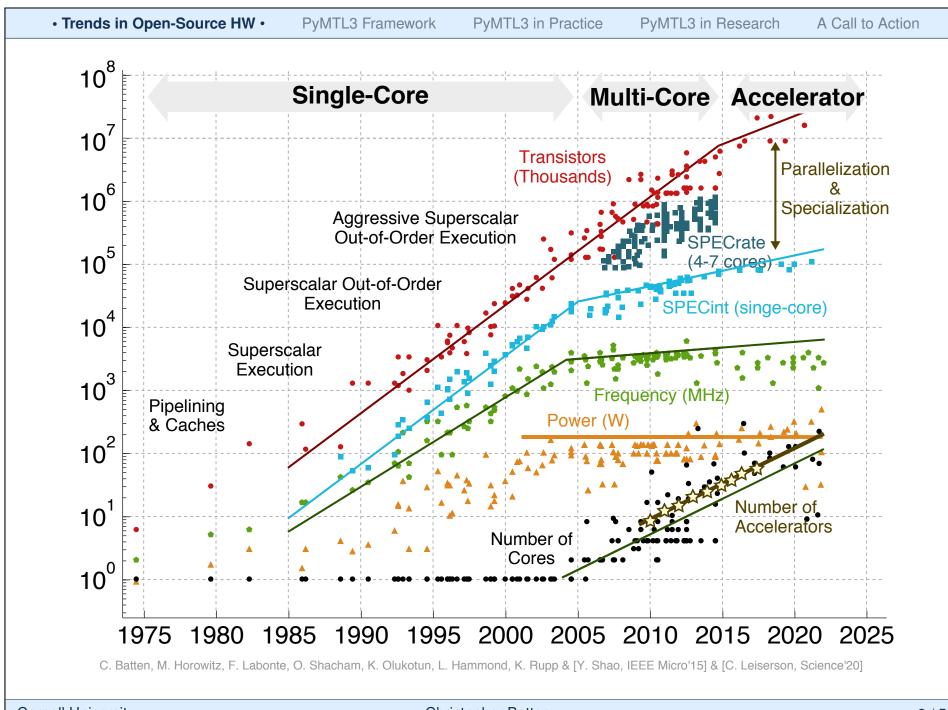

# Top-five software companies are all building custom accelerators

- Facebook: MTIA for DLRM

Amazon: Echo, Oculus, Inferentia/Trainium

Microsoft: In-house AI chips

- Google: TPU, Pixel, convergence

- Apple: SoCs for phones and laptops

Chip startup ecosystem for machine learning accelerators is thriving!

How can we accelerate innovation in accelerator-centric hardware design?

- Graphcore

- Nervana

- Cerebras

- Wave Computing

- Horizon Robotics

- Cambricon

- DeePhi

- Esperanto

- SambaNova

- **Eyeriss**

- Tenstorrent

- Mythic

- ThinkForce

- Groq

- Lightmatter

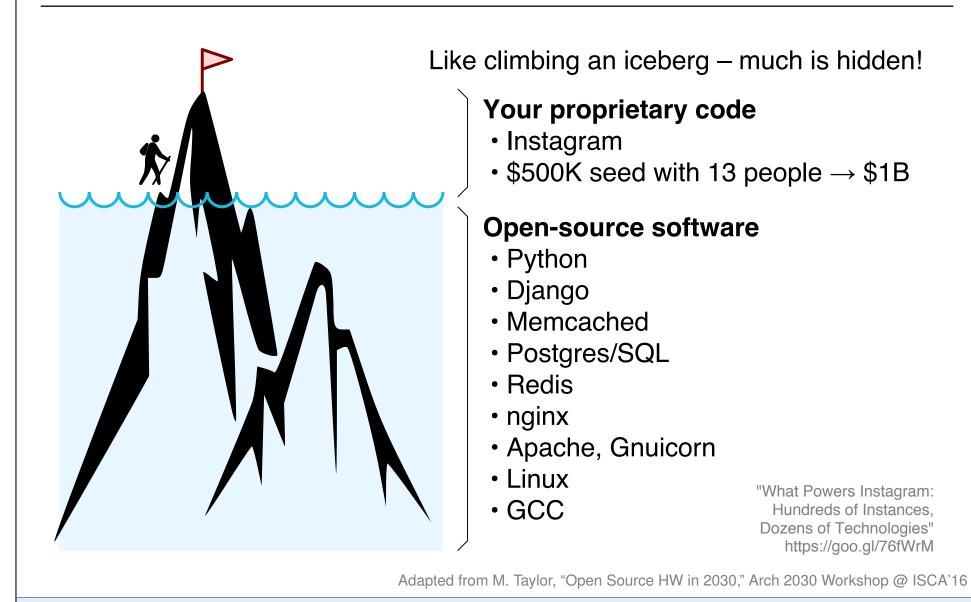

# **Software Innovation Today**

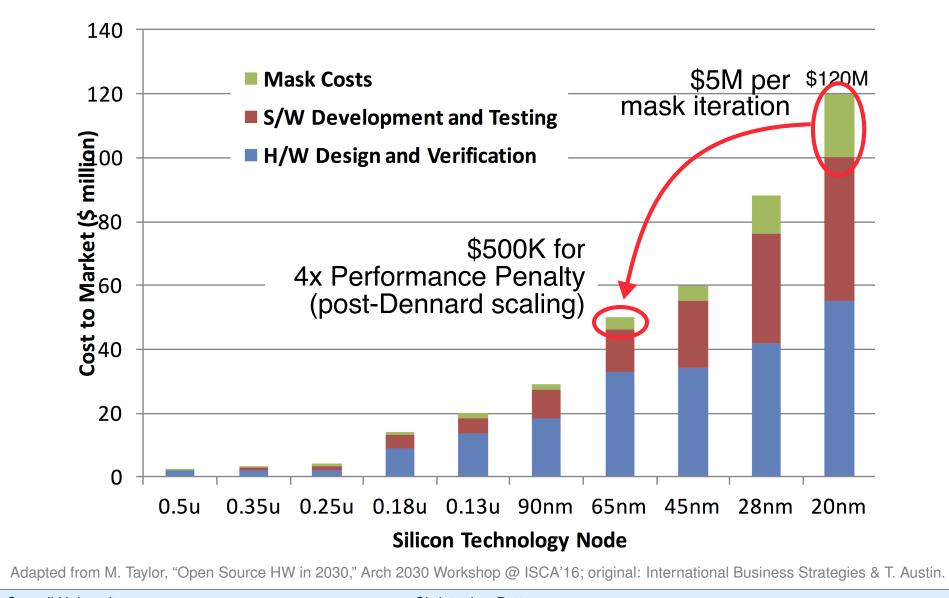

# Hardware Innovation Today

Like climbing a mountain – nothing is hidden!

#### What you have to build

- New machine learning accelerator

- Other unrelated components, anything you cannot afford to buy or for which COTS IP does not do

#### **Closed source**

- ARM A57, A7, M4, M0

- ARM on-chip interconnect

- Standard cells, I/O pads, DDR Phy

- SRAM memory compilers

- VCS, Modelsim

- DC, ICC, Formality, Primetime

- Stratus, Innovus, Voltus

- Calibre DRC/RCX/LVS, SPICE

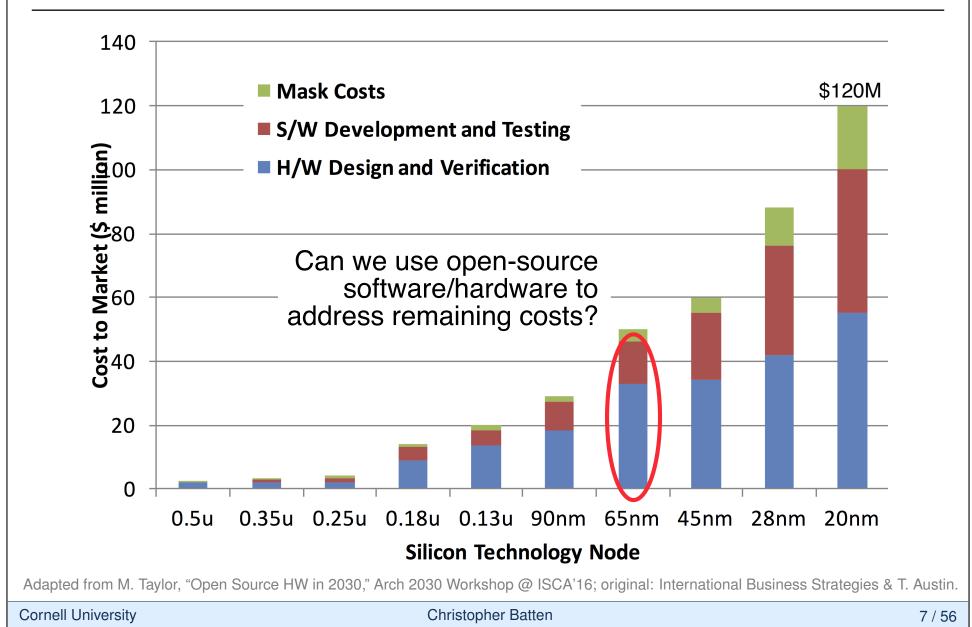

Adapted from M. Taylor, "Open Source HW in 2030," Arch 2030 Workshop @ ISCA'16

### Minimum Viable Product/Prototype

### Minimum Viable Product/Prototype

#### How can HW design be more like SW design?

| <b>Open-Source</b>      | Software                              | Hardware                                                                                    |   |

|-------------------------|---------------------------------------|---------------------------------------------------------------------------------------------|---|

| high-level<br>languages | Python, Ruby, R,<br>Javascript, Julia | Chisel, PyMTL, PyRTL, MyHDL,<br>JHDL, Cλash, Calyx, DFiant                                  |   |

| libraries               | C++ STL,<br>Python std libs           | BaseJump                                                                                    |   |

| systems                 | Linux, Apache, MySQL,<br>memcached    | Rocket, Pulp/Ariane, OpenPiton<br>Boom, FabScalar, MIAOW, Nyuz                              | - |

| standards               | POSIX                                 | RISC-V ISA, RoCC, TileLink                                                                  |   |

| tools                   | GCC, LLVM, CPython,<br>MRI, PyPy, V8  | Icarus Verilog, Verilator, qflow,<br>Yosys, TimberWolf, qrouter,<br>magic, klayout, ngspice |   |

| methodologies           | agile software design                 | agile hardware design                                                                       |   |

| cloud                   | laaS, elastic computing               | laaS, elastic CAD                                                                           |   |

| ell University          | Christopher Bat                       | iten                                                                                        | 8 |

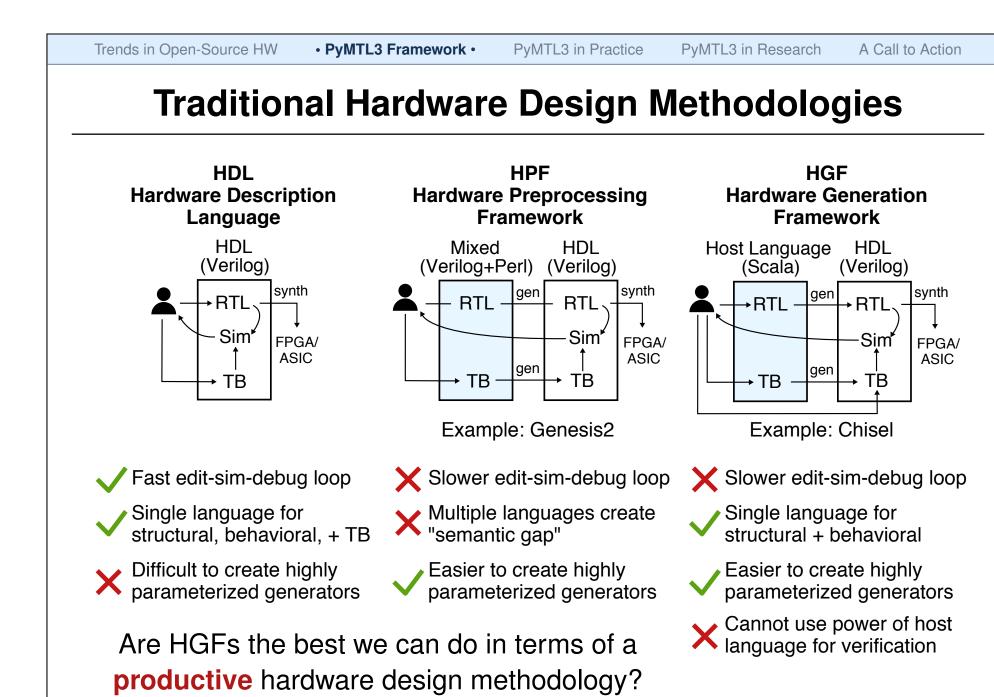

• Trends in Open-Source HW • PyMTL3 Framework PyMTL3 in Practice PyMTL3 in Research A Call to Action

```

# Ubuntu Server 16.04 LTS (ami-43a15f3e)

% sudo apt-get update

c. 2018

% sudo apt-get -y install build-essential qflow

% mkdir qflow && cd qflow

% wget http://opencircuitdesign.com/qflow/example/map9v3.v

% qflow synthesize place route map9v3 # yosys, graywolf, qrouter

% wget http://opencircuitdesign.com/qflow/example/osu035_stdcells.gds2

# design def/lef -> magic format

% magic

>>> lef read /usr/share/qflow/tech/osu035/osu035_stdcells.lef

>>> def read map9v3.def

>>> writeall force map9v3

% magic

# stdcell qds -> magic format

>>> gds read osu035_stdcells.gds2

>>> writeall force

% magic map9v3

>>> gds write map9v3  # design + stdcells magic format -> qds

% sudo apt-get -y install libqt4-dev-bin libqt4-dev libz-dev

% wget http://www.klayout.org/downloads/source/klayout-0.24.9.tar.gz

% tar -xzvf klayout-0.24.9.tar.gz && cd klayout-0.24.9

% ./build.sh -noruby -nopython

% wget http://www.csl.cornell.edu/~cbatten/scmos.lyp

% ./bin.linux-64-gcc-release/klayout -l scmos.lyp ../map9v3.gds

```

**Cornell University**

## **RISC-V Hardware** and Software Ecosystem

**Open-source software:** Gcc, binutils, glibc, Linux, BSD, LLVM, QEMU, FreeRTOS, ZephyrOS, LiteOS, SylixOS, ...

**Commercial software:**

Lauterbach, Segger, IAR, Micrium, ExpressLogic, Ashling, AntMicro, Imperas, UltraSoC ...

Software

ISA specification Golden Model Compliance

#### Hardware

| <b>Open-source cores:</b>  | Commercial core providers:  | Inhouse cores:  |

|----------------------------|-----------------------------|-----------------|

| Rocket, BOOM, RI5CY,       | Andes, Bluespec, Cloudbear, | Nvidia, +others |

| Ariane, PicoRV32, Piccolo, | Codasip, Cortus, C-Sky,     |                 |

| SCR1, Shakti, Swerv,       | InCore, Nuclei, SiFive,     |                 |

| Hummingbird,               | Syntacore,                  |                 |

Trends in Open-Source HW

PyMTL3 Framework PyMTL3 in Practice PyMTL3 in Research A Call to Action **OpenROAD: The Future of Open-Source EDA** design.v + .lib + .lef + .sdc + parameters.cfg Flow parameters Library, techfile preparation **Flow Setup** Macro wrappers Dont\_use list Logic optimization Logic Synthesis Technology mapping Buffering, sizing **OpenROAD** v1.0 Static Timing Analysis (OpenSTA) Parasitic Extraction (OpenRCX) IO placement Mixed-size + macro placement Floorplanning Shared Data Model Tapcell insertion **OpenTitan SoC** PDN generation (OpenDB) Global placement GF12LP **Placement** Placement-based optimization Detailed placement Clock tree synthesis CTS CTS, hold, ERC repair Placement legalization Global routing Routing Antenna check + repair Detailed routing Filler cell + BEOL fill insertion Finishing Merge wrapped macros Merge GDS result.def + ppa.rpt + drc.rpt + results.gds **Cornell University Christopher Batten** 14 / 56

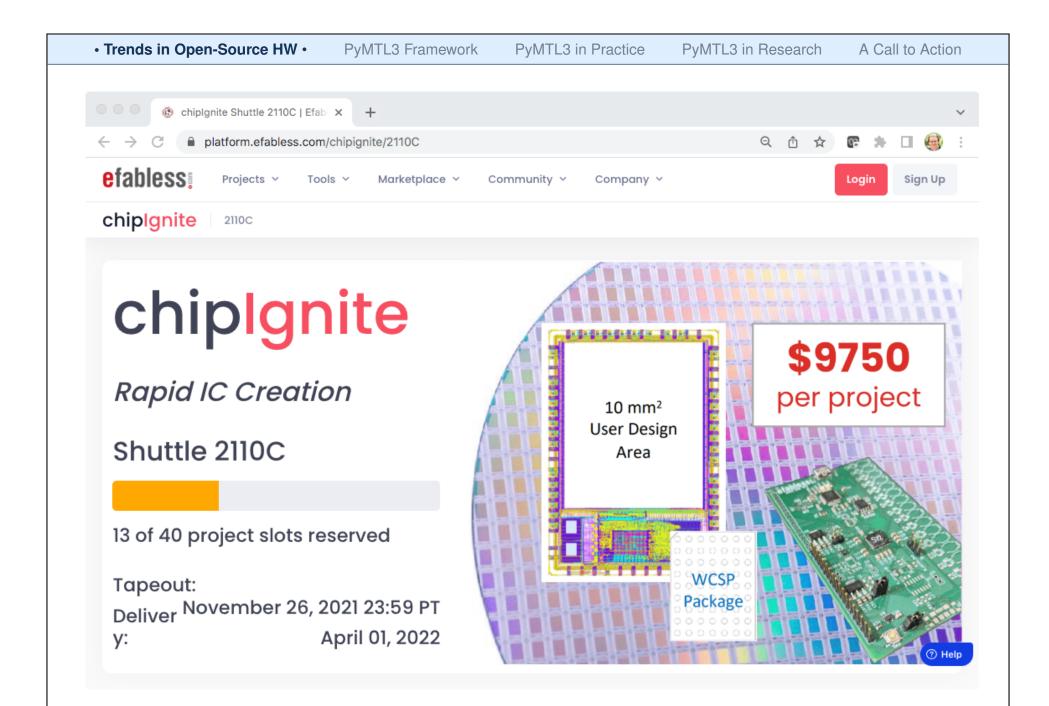

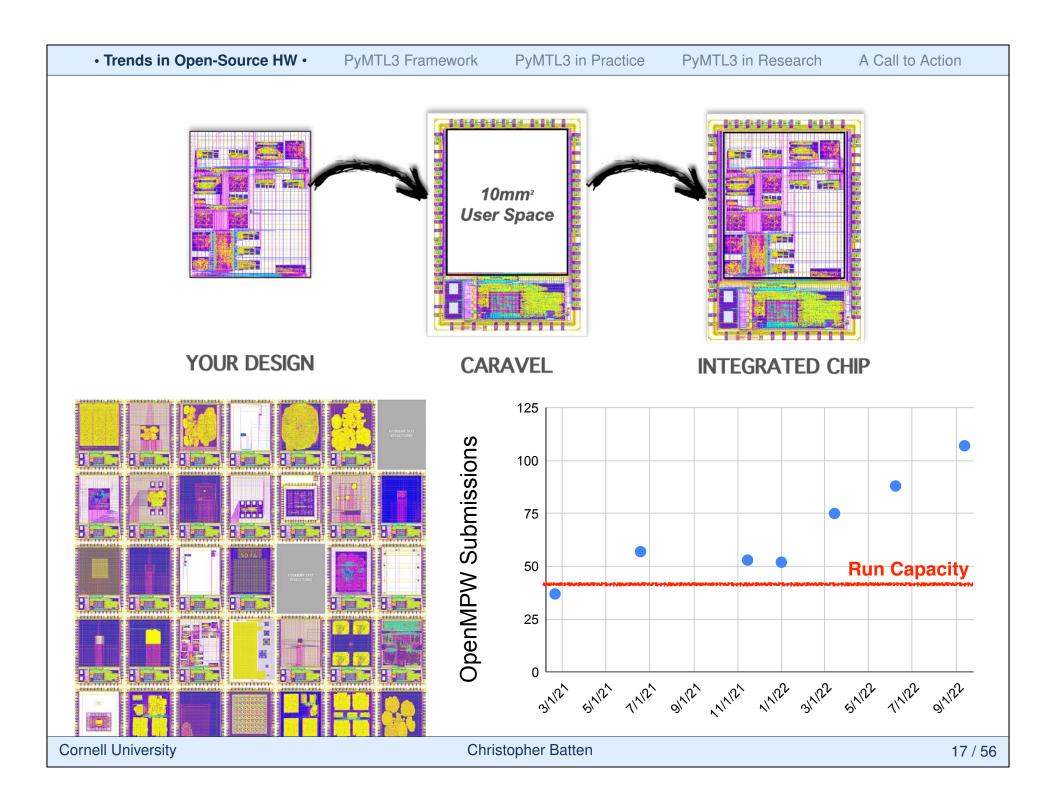

## **C2S2: Cornell Custom Silicon Systems Project Team**

Three-year student-led project team focused on designing, fabricating, and testing chips in SkyWater 130nm to implement a proof-of-concept system for a campus partner

- Open-Source VexRISCV microcontroller

- Open-Source OpenROAD chip flow

- Open PDK for SkyWater 130nm

- ChipIgnite w/ efabless

100+ applications  $\rightarrow$  30 team members

- Digital Subteam (2022/2023: FFT Xcel)

- Analog Subteam (2022/2023: OpAmp)

- Software Subteam

- System Architecture Subteam

- Project Management Subteam

C2S2 Digital and Analog Tapeouts Spring 2023

Trends in Open-Source HW • PyMTL3 Framework • PyMTL3 in Practice

```

1 from pymtl3 import *

2

class RegIncrRTL( Component ):

3

4

def construct( s, nbits ):

5

s.in = InPort ( nbits )

6

s.out = OutPort( nbits )

7

s.tmp = Wire ( nbits )

8

9

@update_ff

10

def seq_logic():

11

s.tmp <<= s.in_

12

13

Qupdate

14

def comb_logic():

15

s.out @= s.tmp + 1

16

```

# A New Era of Open-Source Hardware

PyMTL3 in Research

A Call to Action

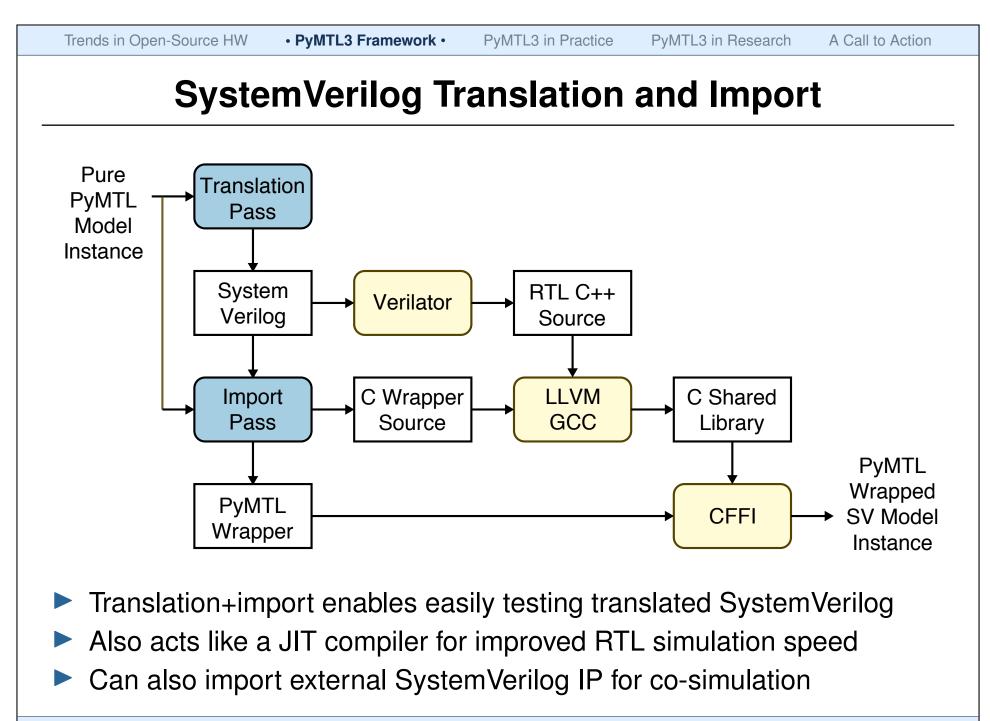

Trends in Open-Source HW **PyMTL3** Framework **PyMTL3** in Practice **PyMTL3** in Research **JIT-Compiled Simulation** [DAC'18] Property-Based Testing [D&T'21] Gradual Typing [MEMOCODE'23] **Future Research**

A Call to Action

Trends in Open-Source HW • PyMTL

```

1 from pymtl3 import *

2

class RegIncrRTL( Component ):

3

4

def construct( s, nbits ):

5

s.in = InPort ( nbits )

6

s.out = OutPort( nbits )

7

s.tmp = Wire ( nbits )

8

9

@update_ff

10

def seq_logic():

11

s.tmp <<= s.in_

12

13

Qupdate

14

def comb_logic():

15

s.out @= s.tmp + 1

16

```

# A New Era of Open-Source Hardware

**Trends in Open-Source HW PyMTL3 Framework PyMTL3** in Practice PyMTL3 in Research JIT-Compiled Simulation [DAC'18] Property-Based Testing [D&T'21] Gradual Typing [MEMOCODE'23] **Future Research**

A Call to Action

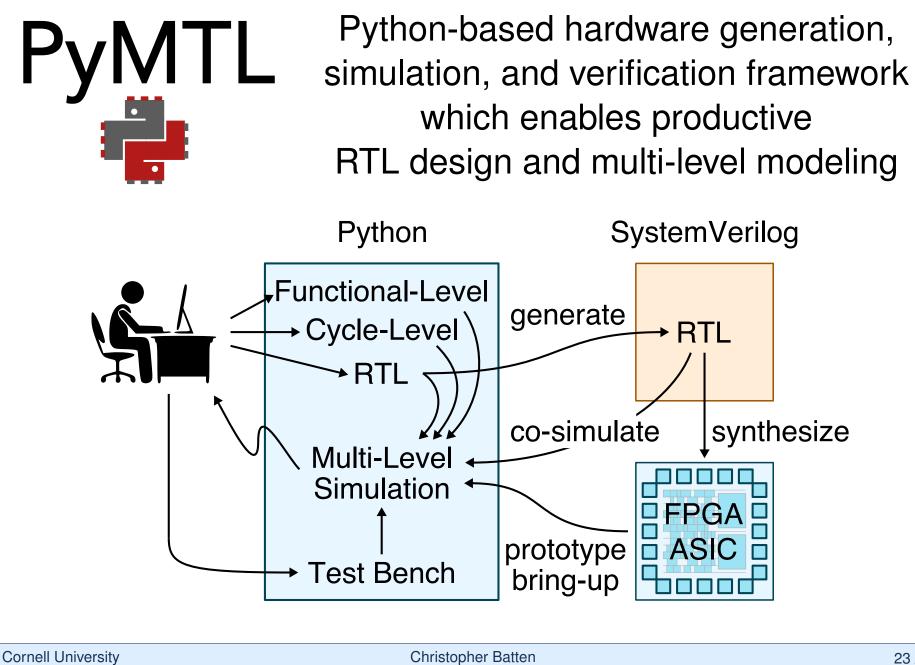

- **PyMTL2**: https://github.com/cornell-brg/pymtl

- ▷ released in 2014

- extensive experience using framework in research & teaching

- **PyMTL3**: https://github.com/pymtl/pymtl3

- official release in May 2020

- adoption of new Python3 features

- significant rewrite to improve productivity & performance

- cleaner syntax for FL, CL, and RTL modeling

- completely new Verilog translation support

- first-class support for method-based interfaces

Trends in Open-Source HW PyMTL3 Framework •

**PyMTL3 in Practice**

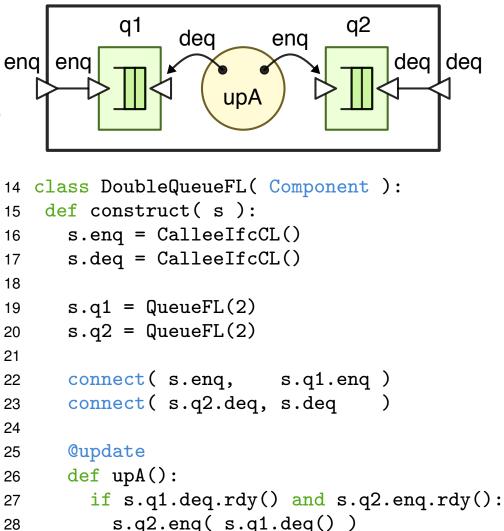

# **PyMTL3 High-Level Modeling**

```

1 class QueueFL( Component ):

def construct( s, maxsize ):

2

s.q = deque( maxlen=maxsize )

3

eng

4

@non_blocking(

5

lambda s: len(s.q) < s.q.maxlen )</pre>

6

def enq( s, value ):

7

s.q.appendleft( value )

8

9

@non_blocking(

15

10

lambda s: len(s.q) > 0)

16

11

def deq( s ):

12

17

return s.q.pop()

18

13

19

20

FL/CL components can use

21

method-based interfaces

22

23

24

Structural composition via

25

connecting methods

26

27

28

```

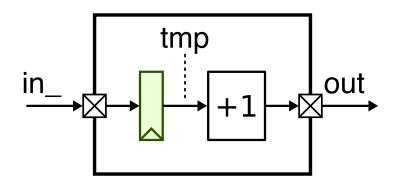

## **PyMTL3 Low-Level Modeling**

```

from pymtl3 import *

2

class RegIncrRTL( Component ):

3

4

def construct( s, nbits ):

5

s.in = InPort ( nbits )

6

s.out = OutPort( nbits )

7

s.tmp = Wire ( nbits )

8

9

@update_ff

10

def seq_logic():

11

s.tmp <<= s.in_</pre>

12

13

Qupdate

14

def comb_logic():

15

s.out @= s.tmp + 1

16

```

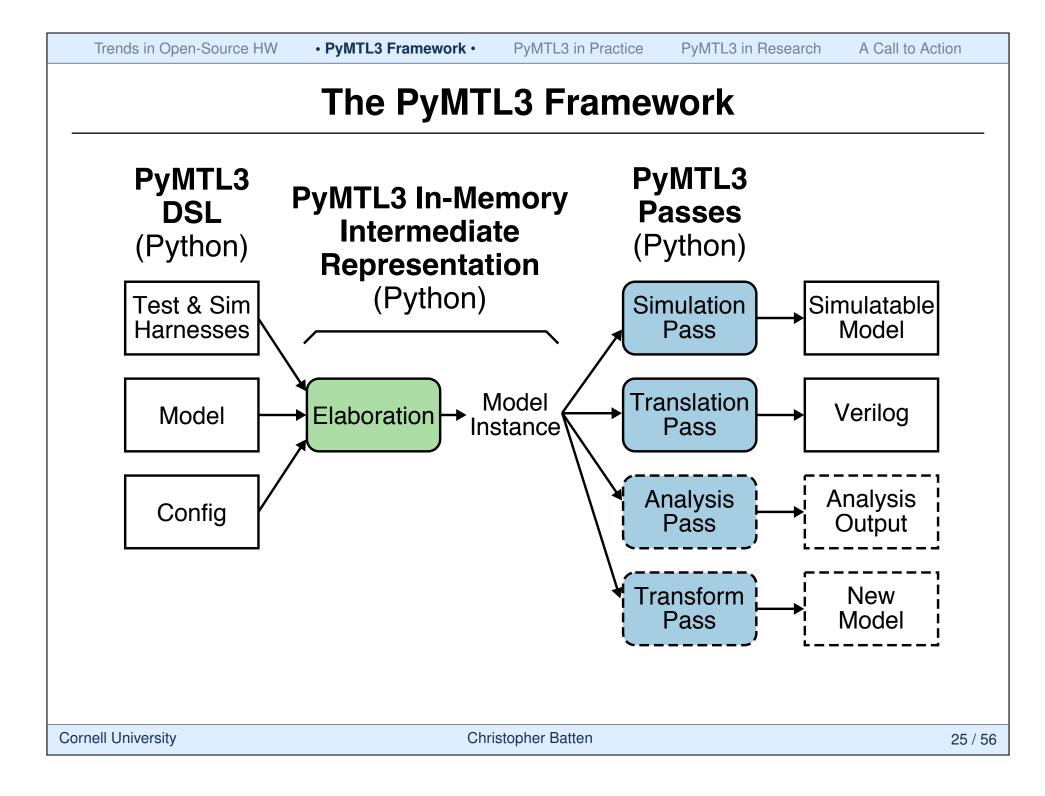

- Hardware modules are Python classes derived from Component

- construct method for constructing (elaborating) hardware

- ports and wires for signals

- update blocks for modeling combinational and sequential logic

## What is PyMTL3 for and not (currently) for?

#### PyMTL3 is for ...

- Taking an accelerator design from concept to implementation

- Construction of highly-parameterizable CL models

- Construction of highly-parameterizable RTL design generators

- Rapid design, testing, and exploration of hardware mechanisms

- Interfacing models with other C++ or Verilog frameworks

#### PyMTL3 is not (currently) for ...

- Python high-level synthesis

- Many-core simulations with hundreds of cores

- Full-system simulation with real OS support

- Users needing a complex OOO processor model "out of the box"

Trends in Open-Source HW PyMTL3 Framework

A Call to Action

```

1 from pymtl3 import *

2

class RegIncrRTL( Component ):

3

4

def construct( s, nbits ):

5

s.in = InPort ( nbits )

6

s.out = OutPort( nbits )

7

s.tmp = Wire ( nbits )

8

9

@update_ff

10

def seq_logic():

11

s.tmp <<= s.in_</pre>

12

13

Qupdate

14

def comb_logic():

15

s.out @= s.tmp + 1

16

```

# A New Era of Open-Source Hardware

Trends in Open-Source HW PyMTL3 Framework

# **PyMTL3 in Practice**

PyMTL3 in ResearchJIT-Compiled Simulation[DAC'18]Property-Based Testing[D&T'21]Gradual Typing[MEMOCODE'23]Future Research

A Call to Action

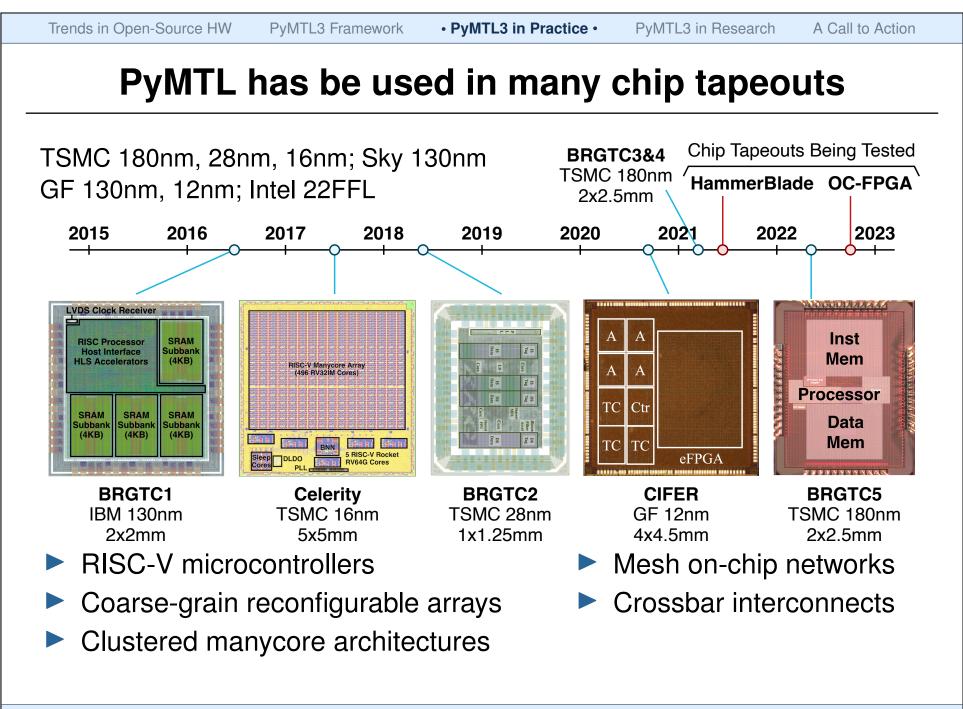

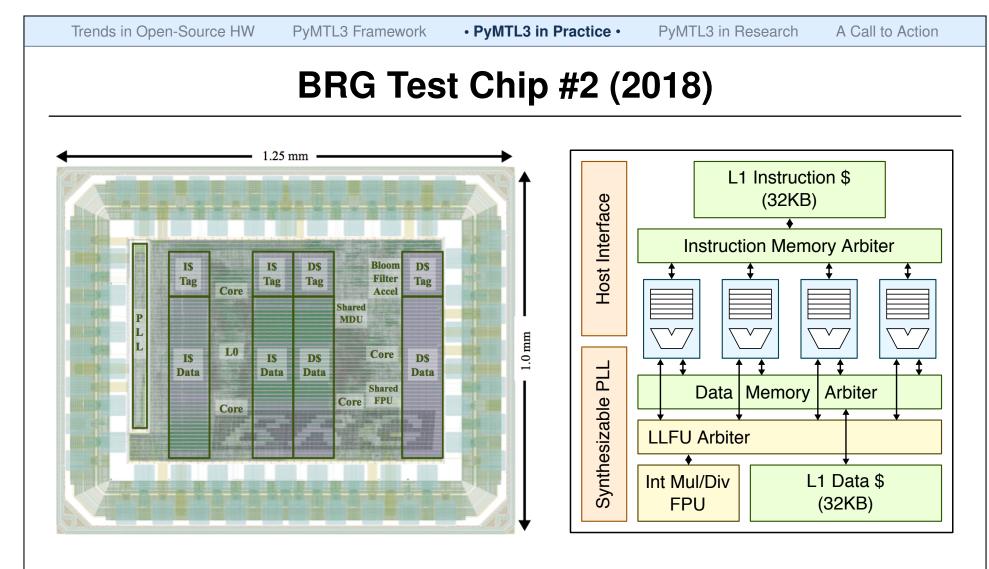

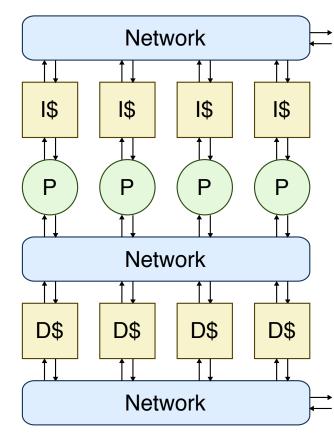

Four RISC-V RV32IMAF cores with "smart" sharing of L1\$/LLFU 1x1.2mm, 6.7M-trans, TSMC 28nm 95% done using PyMTL2

**Christopher Batten**

PyMTL3 in Practice •

A Call to Action

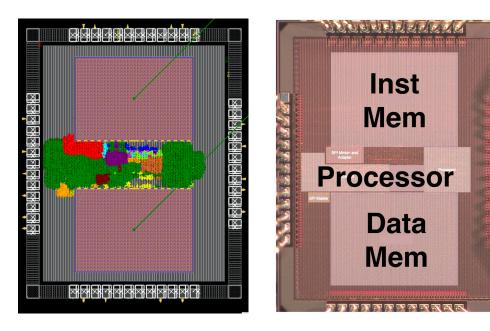

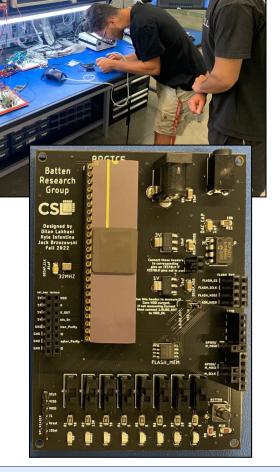

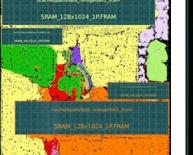

# **BRG Test Chip #5 (2022)**

- RISC-V RV32IM micro-controller

- 2×2.5mm in TSMC 180nm

- 16KB of instruction SRAM, 16KB of data SRAM

- SPI interface for config, SPI master, GP I/O

- 100% done using PyMTL3

- PyMTL3-based post-silicon test environment

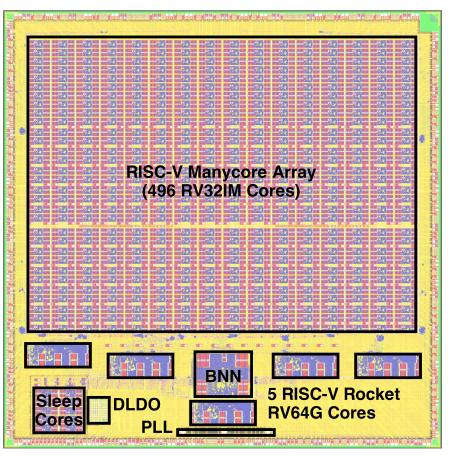

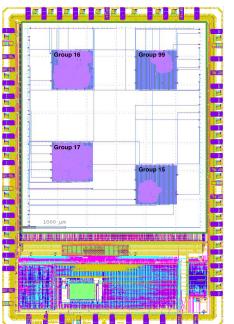

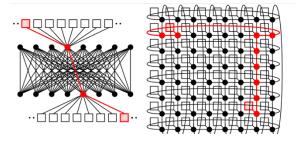

## Celerity System-on-Chip (2016–2018)

Collaboration with UC San Diego & University of Michigan

- ▶  $5 \times 5$ mm in TSMC 16 nm FFC

- 385 million transistors

- 511 RISC-V cores

- ▷ 5 Linux-capable Rocket cores

- ▷ 496-core tiled manycore

- 10-core low-voltage array

- 1 BNN accelerator

- 1 synthesizable PLL

- 1 synthesizable LDO Vreg

- PyMTL2 used for testing and integration of BNN accelerator

[HOTCHIPS'17, IEEE Micro'18, SCCL'18]

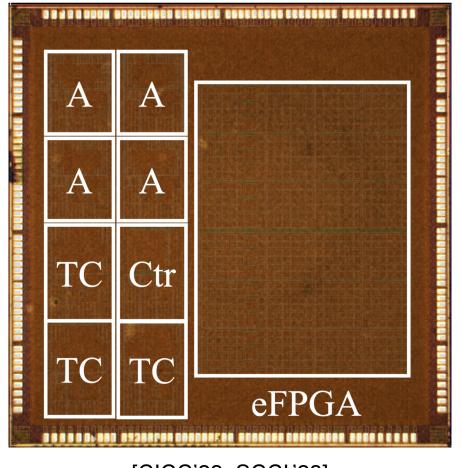

# CIFER System-on-Chip (2021–2023)

#### Collaboration with Princeton University

- $4 \times 4$ mm in GF 12 nm FinFET

- 456 million transistors

- 22 RISC-V cores

- A RV64GC Ariane cores

- 3 Tiny Core clusters each with

6 RV32IM cores

- Embedded FPGA

- Heterogeneous cache coherent memory system

- PyMTL3 used for tiny cores and on-chip mesh network

[CICC'23, SCCL'23]

PyMTL3 in Research

### **PyMTL3 for Undergraduate and Graduate Courses**

**Computer Arch Course** Labs use PyMTL for verification, PyMTL or Verilog for RTL design

**Chip Design Course** Labs use PyMTL for verification, PyMTL or Verilog for RTL design, standard ASIC flow

> First Teaching Tapeout in 10+ years! Four student projects All use PyMTL for testing Two use PyMTL for design

A Call to Action

```

1 from pymtl3 import *

2

class RegIncrRTL( Component ):

3

4

def construct( s, nbits ):

5

s.in = InPort ( nbits )

6

s.out = OutPort( nbits )

7

s.tmp = Wire ( nbits )

8

9

@update_ff

10

def seq_logic():

11

s.tmp <<= s.in_

12

13

Qupdate

14

def comb_logic():

15

s.out @= s.tmp + 1

16

```

## A New Era of Open-Source Hardware

Trends in Open-Source HW PyMTL3 Framework PyMTL3 in Practice

### PyMTL3 in Research

JIT-Compiled Simulation [DAC'18] Property-Based Testing [D&T'21]

Gradual Typing [MEMOCODE'23]

**Future Research**

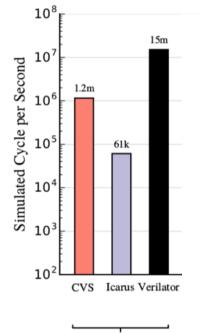

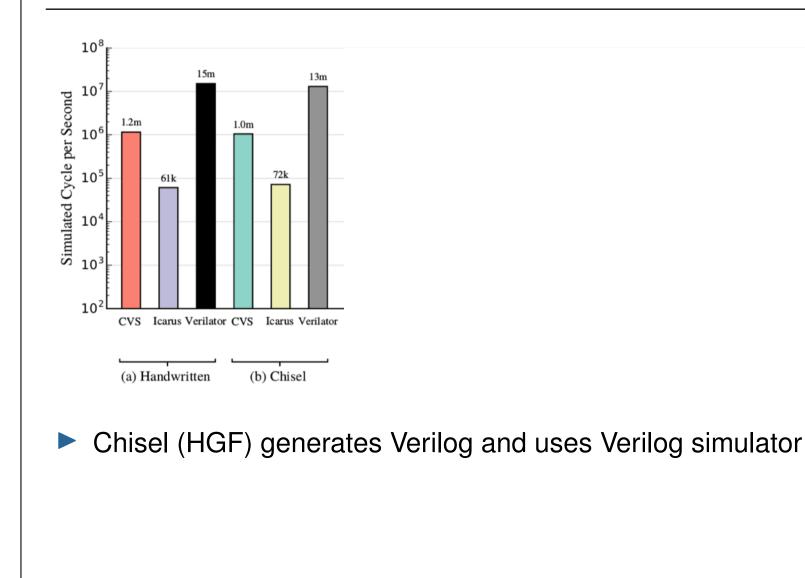

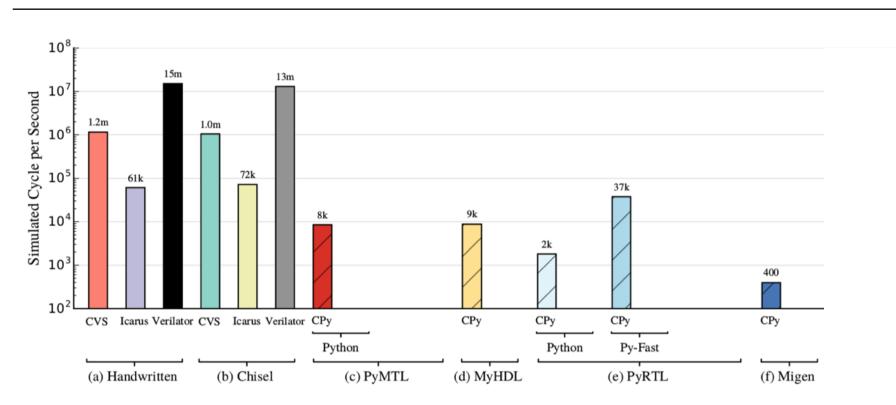

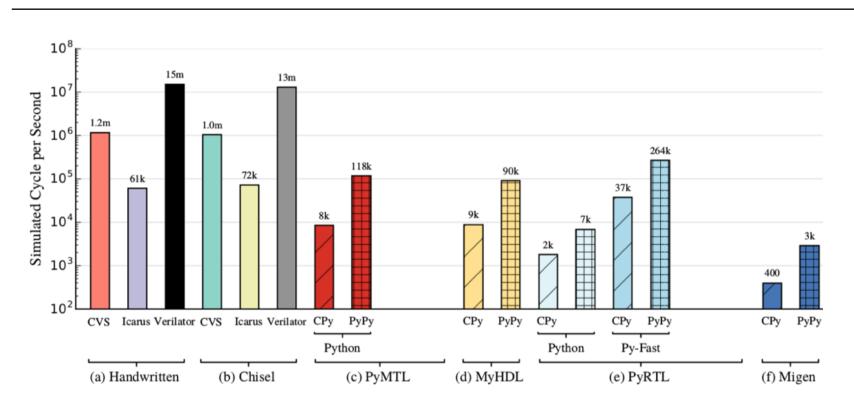

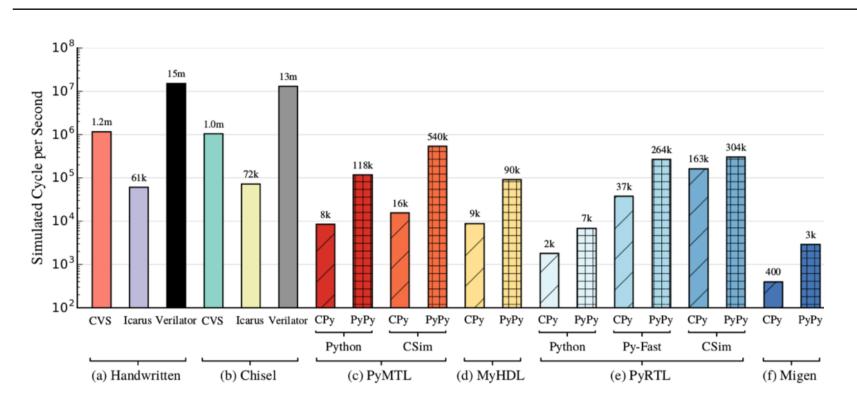

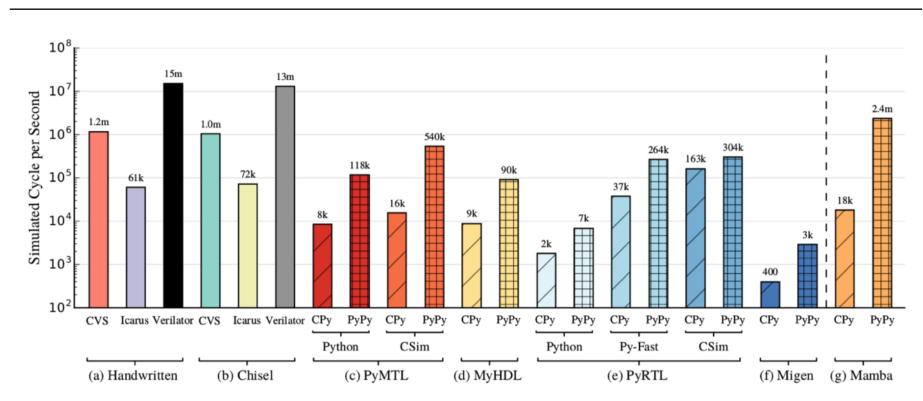

### **Evaluating HDLs, HGFs, and HGSFs**

- Apple-to-apple comparison of simulator performance

- 64-bit radix-four integer iterative divider

- All implementations use same control/datapath split with the same level of detail

- Modeling and simulation frameworks:

- ▷ Verilog: Commercial verilog simulator, Icarus, Verilator

- ▷ HGF: Chisel

- ▶ HGSFs: PyMTL, MyHDL, PyRTL, Migen

### **Productivity/Performance Gap**

(a) Handwritten

- Higher is better

- Log scale (gap is larger than it seems)

- Commercial Verilog simulator is

20× faster than Icarus

- Verilator requires C++ testbench, only works with synthesizable code, takes significant time to compile, but is 200× faster than Icarus

### **Productivity/Performance Gap**

### **Productivity/Performance Gap**

Using CPython interpreter, Python-based HGSFs are much slower than commercial Verilog simulators; even slower than Icarus!

### **Productivity/Performance Gap**

Using PyPy JIT compiler, Python-based HGSFs achieve ~10× speedup, but still significantly slower than commercial Verilog simulator

### **Productivity/Performance Gap**

- Hybrid C/C++ co-simulation improves performance but:

- only works for a synthesizable subset

- ▶ may require designer to simultaneously work with C/C++ and Python

### **Productivity/Performance Gap**

PyMTL3 achieves impressive simulation performance by co-optimizing the framework and JIT

| Trends in Open-Source HW PyMTL3 Fra | amework PyMTL | 3 in Practice • | PyMTL3 in Research • | A Call to Action |  |

|-------------------------------------|---------------|-----------------|----------------------|------------------|--|

| PyMTL3 Performance                  |               |                 |                      |                  |  |

|                                     |               |                 |                      |                  |  |

| Technique                           | Divider       | 1-Core          | 16-core              | 32-core          |  |

| Event-Driven                        | 24K CPS       | 6.6K CPS        | 6 155 CPS            | 66 CPS           |  |

| JIT-Aware HGSF                      |               |                 |                      |                  |  |

| + Static Scheduling                 | <b>13</b> ×   | <b>2.6</b> ×    | <b>1</b> ×           | 1.1×             |  |

| + Schedule Unrolling                | 16×           | <b>2</b> 4×     | 0.4×                 | 0.2×             |  |

| + Heuristic Toposort                | <b>18</b> ×   | <b>26</b> ×     | 0.5	imes             | 0.3×             |  |

| + Trace Breaking                    | <b>19</b> ×   | <b>3</b> 4×     | <b>2</b> ×           | 1.5×             |  |

| + Consolidation                     | <b>27</b> ×   | <b>34</b> ×     | <b>47</b> ×          | <b>42</b> ×      |  |

| HGSF-Aware JIT                      |               |                 |                      |                  |  |

| + RPython Constructs                | <b>96</b> ×   | <b>48</b> ×     | 62×                  | 61×              |  |

| + Huge Loop Support                 | 96×           | <b>49</b> ×     | 65×                  | 67×              |  |

RISC-V RV32IM five-stage pipelined cores

Only models cores, no interconnect nor caches

A Call to Action

```

1 from pymtl3 import *

2

class RegIncrRTL( Component ):

3

4

def construct( s, nbits ):

5

s.in = InPort ( nbits )

6

s.out = OutPort( nbits )

7

s.tmp = Wire ( nbits )

8

9

@update_ff

10

def seq_logic():

11

s.tmp <<= s.in_

12

13

Qupdate

14

def comb_logic():

15

s.out @= s.tmp + 1

16

```

## A New Era of Open-Source Hardware

Trends in Open-Source HW PyMTL3 Framework PyMTL3 in Practice

### PyMTL3 in Research

JIT-Compiled Simulation [DAC'18]

- Property-Based Testing [D&T'21]

- Gradual Typing [MEMOCODE'23]

Future Research

### **Testing HW Design Generators is Challenging**

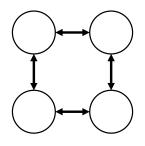

#### Testing a specific ring network instance requires a number of different test cases

test\_ring\_1pkt\_2x2\_0\_chnl test\_ring\_2pkt\_2x2\_0\_chnl test\_ring\_2pkt\_2x2\_0\_chnl test\_ring\_self\_2x2\_0\_chnl test\_ring\_clockwise\_2x2\_0\_chnl test\_ring\_neighbor\_2x2\_0\_chnl test\_ring\_tornado\_2x2\_0\_chnl test\_ring\_backpressure\_2x2\_0\_chnl

### Ideal testing technique:

- 1. Detect error quickly with **small number of test cases**

- 2. The failing test case has **minimal number of transactions**

- 3. The bug trace has **simplest transactions**

- 4. The failing test case has the **simplest design**

| / | pkt( | <pre>src=0,</pre> | dst=1, | payload=0xdeadbeef | ) |

|---|------|-------------------|--------|--------------------|---|

|   | pkt( | <pre>src=0,</pre> |        | payload=0x0000003  | ) |

|   | pkt( | <pre>src=1,</pre> |        | payload=0x00010000 | ) |

|   | pkt( | <pre>src=1,</pre> |        | payload=0x00010002 | ) |

|   | pkt( | <pre>src=2,</pre> | dst=1, | payload=0x00020001 | ) |

|   | pkt( | <pre>src=2,</pre> | dst=3, | payload=0x00020003 | ) |

|   | pkt( | <pre>src=3,</pre> | dst=2, | payload=0x00030002 | ) |

|   | pkt( | <pre>src=3,</pre> | dst=0, | payload=0x00030000 | ) |

|   | pkt( | <pre>src=0,</pre> | dst=1, | payload=0x00001000 | ) |

|   | pkt( | <pre>src=1,</pre> | dst=2, | payload=0x10002000 | ) |

|   | pkt( | <pre>src=2,</pre> | dst=3, | payload=0x20003000 | ) |

|   | pkt( | <pre>src=3,</pre> | dst=0, | payload=0x3000000  | ) |

|   | pkt( | <pre>src=0,</pre> | dst=3, | payload=0x00003000 | ) |

|   | pkt( | <pre>src=1,</pre> | dst=0, | payload=0x1000000  | ) |

|   | pkt( | <pre>src=2,</pre> | dst=1, | payload=0x20001000 | ) |

| - | pkt( | <pre>src=3,</pre> | dst=2, | payload=0x30002000 | ) |

A design generator can have many parameters: topology, routing, flow control, channel latency

### **Software Testing Techniques**

- Complete Random Testing (CRT)

- Randomly generate input data

- Detects error quickly

- Debug complicated test case

- Iterative Deepened Testing (IDT)

- Gradually increase input complexity

- Finds bug with simple input

- Takes many test cases to find bug

- Property-Based Testing (PBT)

- Search strategies, auto shrinking

- Detects error quickly

- Produces minimal failing test case

- Increasingly state-of-the-art in software testing

```

def gcd( a, b ):

while b > 0:

a, b = b, a % b

return a

```

```

def test_crt():

```

for \_ in range( 100 ):

a = random.randint( 1, 128 )

b = random.randint( 1, 128 )

assert gcd( a, b ) == math.gcd( a, b )

```

def test_idt():

for a_max in range( 1, 128 ):

for b_max in range( 1, 128 ):

assert gcd( a, b ) == math.gcd( a, b )

```

```

@hypothesis.given(

a = hypothesis.strategies.integers( 1, 128 ),

b = hypothesis.strategies.integers( 1, 128 ),

)

def test_pbt( a, b ):

assert gcd( a, b ) == math.gcd( a, b )

```

### PyH2 Creatively Adopts PBT for SW to Test HW

- PyH2 combines PyMTL3, a unified hardware modeling framework, with Hypothesis, a PBT framework for Python software and creates a property-based testing framework for hardware

- PyH2 leverages PBT to explore not just the input values for an HW design but to also explore the parameter values used to configure an HW design generator

|                                        | Complete<br>Random<br>Testing | Iterative<br>Deepened<br>Testing | PyH2         |

|----------------------------------------|-------------------------------|----------------------------------|--------------|

| Small number of test cases to find bug | $\checkmark$                  | Х                                | $\checkmark$ |

| Small number transactions in bug trace | e X                           | $\checkmark$                     | $\checkmark$ |

| Simple transactions in bug trace       | Х                             | $\checkmark$                     | $\checkmark$ |

| Simple design instance for bug trace   | Х                             | $\checkmark$                     | $\checkmark$ |

A Call to Action

```

1 from pymtl3 import *

2

class RegIncrRTL( Component ):

3

4

def construct( s, nbits ):

5

s.in = InPort ( nbits )

6

s.out = OutPort( nbits )

7

s.tmp = Wire ( nbits )

8

9

@update_ff

10

def seq_logic():

11

s.tmp <<= s.in_

12

13

Qupdate

14

def comb_logic():

15

s.out @= s.tmp + 1

16

```

## A New Era of Open-Source Hardware

Trends in Open-Source HW PyMTL3 Framework PyMTL3 in Practice

### PyMTL3 in Research

JIT-Compiled Simulation [DAC'18]

- Property-Based Testing [D&T'21]

- Gradual Typing [MEMOCODE'23]

Future Research

|                             | Design<br>Productivity | Testing<br>Productivity | Simulation<br>Performance | Static Correctness<br>Guarantees |

|-----------------------------|------------------------|-------------------------|---------------------------|----------------------------------|

| Verilog/SystemVerilog       | Low                    | Low                     | High 🔵                    | Low                              |

| Bluespec                    | Medium                 | Low                     | Medium 🕓                  | High                             |

| Clash/Chisel/SpinalHDL      | Medium                 | Low                     | Medium                    | Medium                           |

| PyRTL/MyHDL/Migen/<br>PyMTL | High                   | High                    | Low                       | None                             |

| PyMTL3                      | High                   | High                    | Medium 🚺                  | Low                              |

Trends in Open-Source HW PyMTL3 Framework PyMTL3 in Practice • PyMTL3 in Research • A Call to Action Gradual Gradua Gradual Gradua Gradual 1 class Foo: 1 T\_W = TypeVar( "T\_W", bound=Bits ) bar = 42Dynamic 2 3 def g(x): class RegIncrRTL( Component, 3 x.bar = 'hello world' 4 Generic[T\_W] ): 5 def f(x:Object({bar:Int}))->Int: 4 g(x)6 5 Static return x.bar 7 def construct( s, W: Type[T\_W] ): 6 8 f(Foo()) s.in\_ = InPort (W) 7 s.out = OutPort(W) Code in Reticulated Python, 8 a Gradually Typed Dialect of Python s.tmp = Wire (W) 9 10 IDiv @update\_ff 11 IDivCtrl rdy def seq\_logic(): 12 IDivDpath [n:n\*2] **Fest Bench: Test Source** s.tmp <<= s.in\_</pre> 13 Test Bench: Test Sin 14 **Qupdate** 15 def comb\_logic(): 16 s.out @= s.tmp + 1 17 Dyn. Typed Static. Typed 1 ~ 3 Dyn. Checks ······ Boundary

Component Hierarchy in GT-HDL

**Symbolic Elaboration**  $T_W = TypeVar("T_W", bound=Bits)$ 1 How can we prove class Adder(Component, Generic[T\_W]): 2 matching bitwidths for the def construct(s, W: Type[T\_W]) -> None: 3 assignment in upblock in  $n = get_nbits(W)$ 4 5 all possible instances? = InPort (W) s.a 6 s.b = InPort(W)Instead of using concrete 7 s.out = OutPort(mk bits(n+1)) 8 bitwiths at elaboration s.carry = Wire (mk\_bits(n+1)) 9 time, we symbollically = Wire (W) s.sum 10 determine the bitwdiths 11 s.fa = [FullAdder() for \_ in range(n)] 12 ahead of time 13 for i in range(n): 14 We can translate if  $i \ge 0$ : 15 geneartor properties into connect(s.carry[i+1], s.fa[i].cout) 16 integer constraints 17 . . . suitable for use with an **@update** 18 def upblk() -> None: 19 SMT solver s.out @= concat(s.carry[n], s.sum) 20

**PyMTL3** in Practice

PyMTL3 in Research

A Call to Action

PyMTL3 Framework

Trends in Open-Source HW

A Call to Action

```

1 from pymtl3 import *

2

class RegIncrRTL( Component ):

3

4

def construct( s, nbits ):

5

s.in = InPort ( nbits )

6

s.out = OutPort( nbits )

7

s.tmp = Wire ( nbits )

8

9

@update_ff

10

def seq_logic():

11

s.tmp <<= s.in_

12

13

Qupdate

14

def comb_logic():

15

s.out @= s.tmp + 1

16

```

## A New Era of Open-Source Hardware

Trends in Open-Source HW PyMTL3 Framework PyMTL3 in Practice

### PyMTL3 in Research

JIT-Compiled Simulation [DAC'18]

- Property-Based Testing [D&T'21]

- Gradual Typing [MEMOCODE'23]

**Future Research**

PyMTL3 in Practice

### **PyMTL3 Publications**

- Shunning Jiang, et al. "Mamba: Closing the Performance Gap in Productive Hardware Development Frameworks." 55th ACM/IEEE Design Automation Conf. (DAC), June 2018.

- Shunning Jiang, Peitian Pan, Yanghui Ou, et al. "PyMTL3: A Python Framework for Open-Source Hardware Modeling, Generation, Simulation, and Verification." *IEEE Micro*, 40(4):58–66, July 2020.

- Shunning Jiang\*, Yanghui Ou\*, Peitian Pan, et al. "PyH2: Using PyMTL3 to Create Productive and Open-Source Hardware Testing Methodologies." *IEEE Design & Test*, 38(2):53–61, Apr. 2021.

- Shunning Jiang, Yanghui Ou, Peitian Pan, et al. "UMOC: Unified Modular Ordering Constraints to Unify Cycle- and Register-Transfer-Level Modeling." 58th ACM/IEEE Design Automation Conf. (DAC), Dec. 2021.

| Ther                  | ne Article: Agile and Open-Sourc                                                                                                                                                                                                                                                                                                                                                                | e Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fra<br>Ha<br>Ge<br>an | MTL3: A Pythor<br>amework for Op<br>ardware Modelin<br>eneration, Simu<br>d Verification                                                                                                                                                                                                                                                                                                        | en-Source<br>ng,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       | Abstract—In this article, we present PyHTL3,<br>modeling, peneration, simulation, and verifica<br>using the Python language, PyHTL3 is designer<br>workflows for both hardware designers and co<br>seamless multilevel modeling environment an<br>architecture using a cophisticated in memory<br>of passes that analyze, instrument, and Transi<br>PyHTL3 can pyga minportant role in jump-ata | ed to provide flexible, modular, and extensible<br>omputer architects. PMTL3 supports a<br>d carefully designed modular software<br>intermediate representation and a collection<br>orm PyMTL3 hardware models. We believe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                       | Doe to the breakdown of transistor scaling<br>and the slowdown of Moore's law, there has<br>been an increasing trend loward caregyefficient<br><i>Light Oper Monther ID 100 JML 2022 207CH</i><br><i>Date of publication 23 May 2020, date of current cersion<br/>20 Jane 2020.</i>                                                                                                             | equented paire official spinol (SSG) and a spinol s |

| 58                    | 0.272-1722 © 2020 IEEE Published by the I                                                                                                                                                                                                                                                                                                                                                       | EEE Computer Society                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

- Peitan Pan, Shunning Jiang, Yanghui Ou, et al. "Symbolic Elaboration: Checking Generator Properties in Dynamic Hardware Description Languages." 21st ACM/IEEE Int'l Symp. on Formal Methods and Models for System Design (MEMOCODE), Sep. 2023.

- Peitan Pan, Christopher Batten. "Formal Verification of the Stall Invariant Property for Latency-Insensitive RTL Modules." 21st ACM/IEEE Int'l Symp. on Formal Methods and Models for System Design (MEMOCODE), Sep. 2023.

A Call to Action

```

1 from pymtl3 import *

2

class RegIncrRTL( Component ):

3

4

def construct( s, nbits ):

5

s.in = InPort ( nbits )

6

s.out = OutPort( nbits )

7

s.tmp = Wire ( nbits )

8

9

@update_ff

10

def seq_logic():

11

s.tmp <<= s.in_

12

13

Qupdate

14

def comb_logic():

15

s.out @= s.tmp + 1

16

```

## A New Era of Open-Source Hardware

**Trends in Open-Source HW PyMTL3 Framework PyMTL3** in Practice PyMTL3 in Research JIT-Compiled Simulation [DAC'18] Property-Based Testing [D&T'21] Gradual Typing [MEMOCODE'23] **Future Research**

- Open-source hardware needs developers who

- ▷ ... are idealistic

- ▷ ... have lots of free time

- ... will work for free

- Who might that be?

### Students!

Academics have a practical and ethical motivation for using, developing, and promoting open-source EDA tools and open-source hardware designs

- Two key trends make this a particularly exciting time to contribute

- Open-source verification methodologies and tools are a key challenge

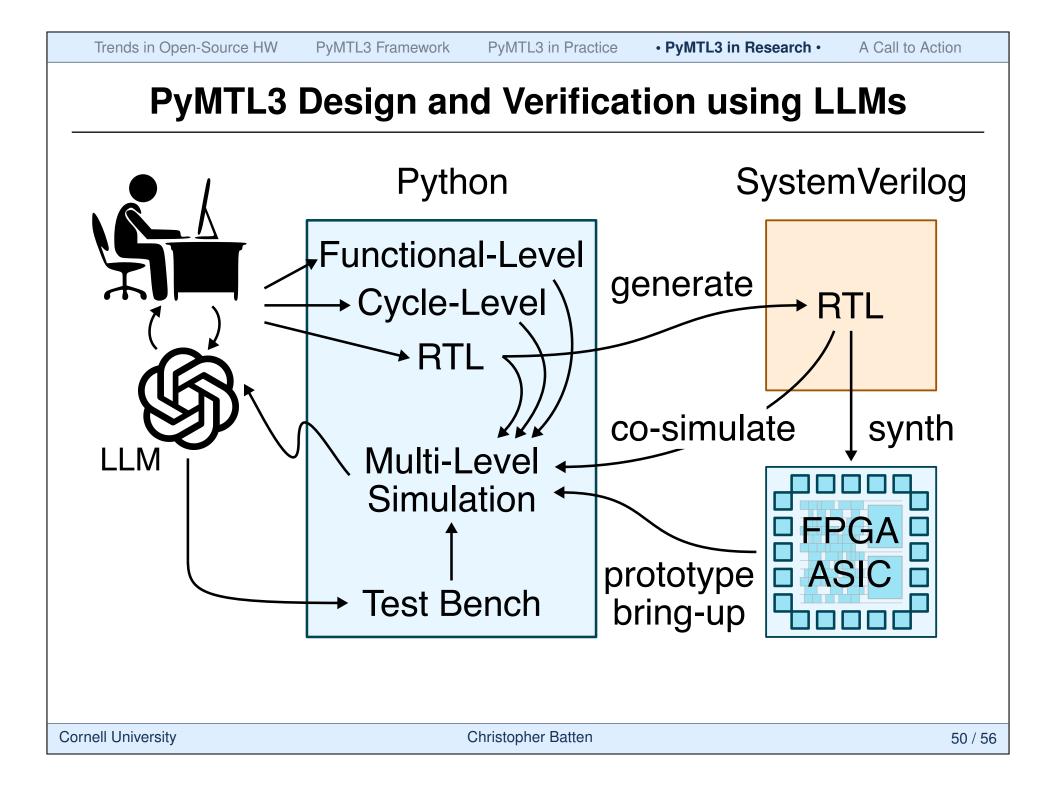

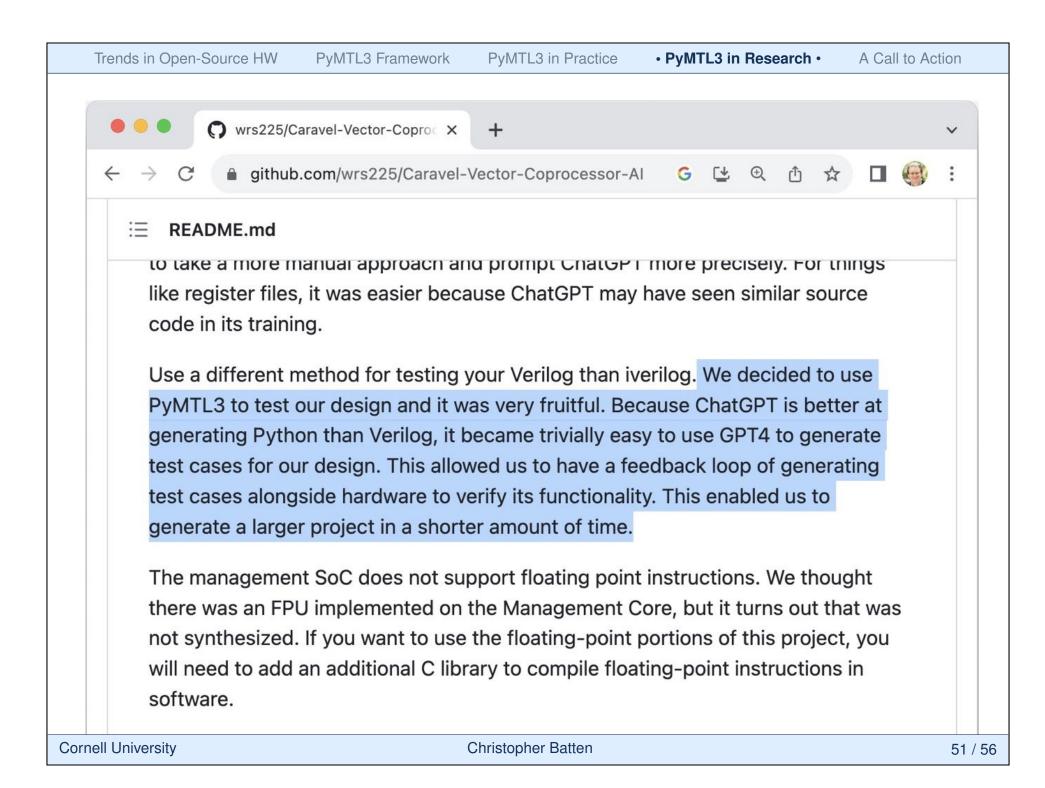

- Large-language models offer a new opportunity to address this challenge

**Cornell University**

Christopher Batten

This work was supported in part by NSF XPS Award #1337240, NSF CRI Award #1512937, NSF SHF Award #1527065, AFOSR YIP Award #FA9550-15-1-0194, DARPA Young Faculty Award #N66001-12-1-4239, DARPA POSH Award #FA8650-18-2-7852, DARPA SDH Award #FA8650-18-2-7863, a Xinux University Program industry gift, and the the Center for Applications Driving Architectures (ADA), one of six centers of JUMP, a Semiconductor Research Corporation program co-sponsored by DARPA, and equipment, tool, and/or physical IP donations from Intel, NVIDIA, Synopsys, and ARM.

Thanks to the core PyMTL developers, Derek Lockhart, Shunning Jiang, Peitian Pan, Yanghui Ou, along with Khalid Al-Hawaj, Moyang Wang, Tuan Ta, Ji Kim, Shreesha Srinath, Berkin Ilbeyi, Dilan Lakhani, Jack Brzozowski, Kyle Infantino, Yixiao Zhang, Jacob Glueck, Aaron Wisner, Gary Zibrat, Christopher Torng, Cheng Tan, Raymond Yang, Kaishuo Cheng, Carl Friedrich Bolz, David MacIver, and Zac Hatfield-Dodds for their help designing, developing, testing, and using PyMTL

The U.S. Government is authorized to reproduce and distribute reprints for Government purposes notwithstanding any copyright notation theron. Any opinions, findings, and conclusions or recommendations expressed in this publication are those of the author(s) and do not necessarily reflect the views of any funding agency.