Cornell University

School of Electrical and Computer Engineering

ECE 5970 Chip-Level Interconnection Networks

Spring 2010

Prof. Christopher Batten

207 Upson Hall • Tuesday and Thursday • 10:10–11:25am

home | details | schedule | projects

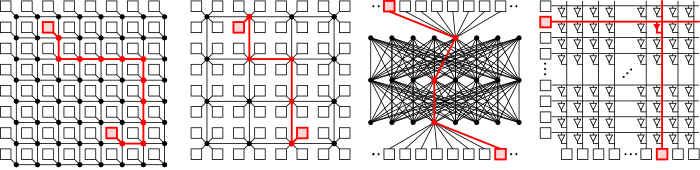

Today's embedded, network, graphics, and server processors already contain tens to hundreds of cores integrated onto just a few chips, and this number will surely increase with future scaling. Chip-level interconnection networks, which connect cores on the same or different chips to each other and to main memory, are becoming a critical design component in terms of performance, power consumption, and programmer productivity. This course will explore the underlying principles and the practical implementation issues for such interconnection networks.

Topics will include network topology, routing algorithms, flow-control strategies, router microarchitecture, performance analysis, and emerging physical technology issues. We will examine applications in message-passing and shared-memory networks for single-chip and multiple-chip multiprocessors. The course will include a mix of lectures and student-led discussion of both classic and modern research papers in the field. Students are expected to read and digest all assigned reading and to articulate their views in class discussion. Students will prepare short critiques of each reading, and will be responsible for leading the discussion and preparing a more comprehensive critique of one research paper. There will be one quiz covering both the lecture material and our class discussions.

In the latter portion of the course, students will work in small groups to design, implement, and evaluate an interesting research idea related to chip-level interconnection networks. Students are encouraged to select projects that overlap with their own research. Groups will summarize their findings in a short presentation and a conference-style paper.