# ECE 4750 Computer Architecture, Fall 2016 T06 Fundamental Network Concepts

School of Electrical and Computer Engineering Cornell University

revision: 2016-10-16-22-06

| 1 | Net  | work/Roadway Analogy                  | 3  |

|---|------|---------------------------------------|----|

|   | 1.1. | Running Errands                       | 4  |

|   | 1.2. | Network Technology                    | 5  |

|   | 1.3. | Networks in Computer Architecture     | 6  |

| 2 | Net  | work Topology                         | 8  |

|   | 2.1. | Single-Stage Bus Topology             | 8  |

|   | 2.2. | Single-Stage Crossbar Topology        | 9  |

|   | 2.3. | Multi-Stage Butterfly Topology 1      | .0 |

|   | 2.4. | Multi-Stage Torus Topology 1          | 2  |

|   | 2.5. | Terminology                           | .4 |

| 3 | Net  | work Routing 1                        | 8  |

|   | 3.1. | Oblivious Deterministic Routing 1     | .8 |

|   | 3.2. | Oblivious Non-Deterministic Routing 1 | 8  |

|   | 3.3. | Adaptive Routing                      | 9  |

|   | 3.4. | Deadlock                              | 20 |

| 4 | Ana  | lyzing Network Performance   | 21 |

|---|------|------------------------------|----|

|   | 4.1. | Traffic Patterns             | 21 |

|   | 4.2. | Ideal Throughput             | 23 |

|   | 4.3. | Zero-Load Latency            | 25 |

|   | 4.4. | Comparing Topologies         | 28 |

|   | 4.5. | Comparing Routing Algorithms | 29 |

### 1. Network/Roadway Analogy

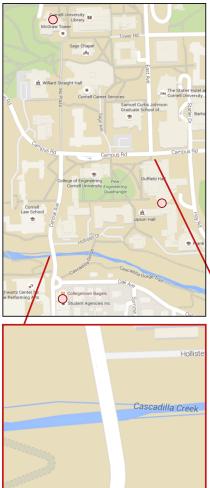

Our goal is to run some errands around town using our bike. Assume we are studying in the Duffield Atrium and we need to: (1) do some laundry in Collegetown (maybe pickup some coffee?), and (2) pick up some books about computer architecture from the library.

- Duffield Atrium

- Coffee/Laundry

- Library

### 1.1. Running Errands

- Network Topology

- Arrangement of roads and intersections to interconnect sources and destinations

- Wide vs. narrow roads

- Long vs. short roads

- Small vs. large intersections

- Network Routing

- Path from source to destination along roads and intersections

- Short vs. long paths

- Common vs. rare paths

- Network Microarchitecture

- Managing long line of bikes and cars on road

- Managing many cars and bikes at same intersection

### 1.2. Network Technology

|                 | AWG24<br>Twisted Pair | PCB Trace                        | On-Chip M6<br>Wire in 0.18µm     |  |

|-----------------|-----------------------|----------------------------------|----------------------------------|--|

|                 |                       |                                  |                                  |  |

| Resistance      | $0.08\Omega/m$        | $5\Omega/m$                      | $40 \mathrm{k}\Omega/\mathrm{m}$ |  |

| Inductance      | 400 nH/m              | 300 nH/m                         | $4\mu H/m$                       |  |

| Capacitance     | 40 pF/m               | 100 pF/m                         | 300 pF/m                         |  |

| Data Rate       | $\approx$ Gb/s        | ≈Gb/s                            | $\approx Gb/s$                   |  |

| Critical Length | 1m                    | 10cm                             | <1cm                             |  |

| Pitch           | $\approx$ mm          | <mm< th=""><th>&lt;µm</th></mm<> | <µm                              |  |

#### **On-Chip Wires**

Distributed Wire Resistance and Capacitance

Because both wire resistance and wire capacitance increase with length, wire delay grows quadratically with length

On-chip buffers are 1r1 FIFOs implemented using either a register file or SRAM

On-chip network technology constraints very different from off-chip technology constraints

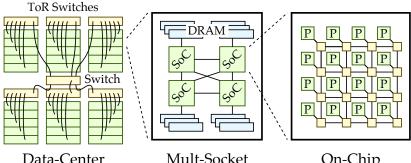

### 1.3. Networks in Computer Architecture

- Network Topology

- Arrangement of channels and routers to interconnect sources and destinations

- Roads = channels (implemented with cables, traces, wires)

- Width of road = channel bw

- Intersections = routers

- Size intersection = router radix

- Network Routing

- Path from source to destination along channels and routers

- Short vs. long paths = minimal vs. non-minimal paths

- Common vs. rare paths = channel congestion

- Topology is constrained by packaging (geography)

Mult-Socket

On-Chip

### **Network Transactions**

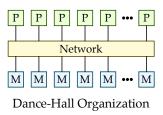

We will use processor-memory networks as a driving example throughout the course. Processor-memory networks allow many processors to perform memory read/write transactions on many memories.

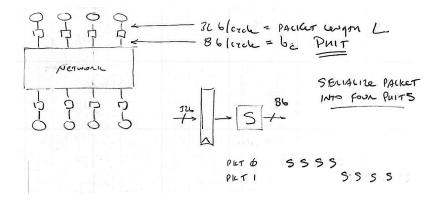

- Message = Logical unit of data transfer provided by network interface

- Packet = Unit of routing within a network

- Flit = Smallest unit of resource allocation in channel/router (flow-control digit)

- Phit = Smallest unit of data processed by a channel/router (physical digit)

For the processor-memory networks we will primarily study:

The processor will send memory request messages/packets over the network, and the memories will send memory response messages/packets back to the processor. In this context, we consider the network messages/packets to be the "transactions".

| Processors | : | Instructions    |

|------------|---|-----------------|

| Memories   | : | Memory accesses |

| Networks   | : | Network packets |

Integrated-Node Organization

### 2. Network Topology

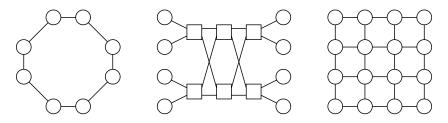

Network topology is the arrangement of channels and routers to interconnect sources and destinations. We will explore four different topology classes:

- Single-stage bus topologies

- Single-stage crossbar topologies

- Multi-stage butterfly topologies

- Mult-stage torus topologies

## 2.1. Single-Stage Bus Topology

#### SWMR Bus

#### **MWSR Bus**

MWMR Bus

#### **Integrating Multiple Buses**

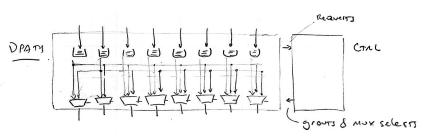

### 2.2. Single-Stage Crossbar Topology

- Single-stage topologies are difficult to scale in terms of cycle time, energy, and area

- Multi-stage topologies improve scalability but raise many other interesting challenges

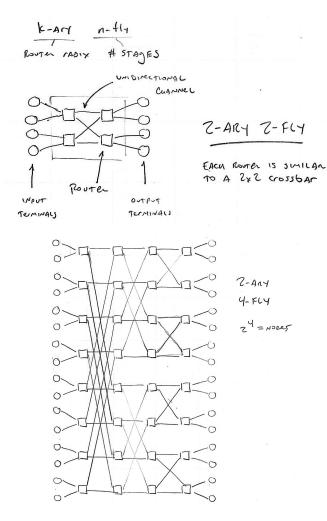

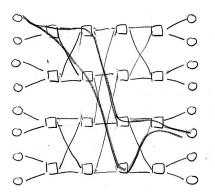

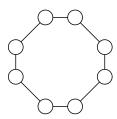

### 2.3. Multi-Stage Butterfly Topology

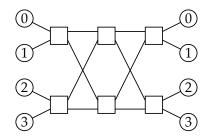

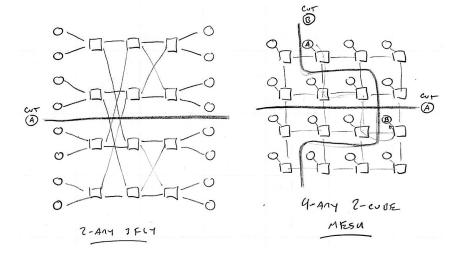

#### **Example Butterfly Topology: 4-ary 2-fly**

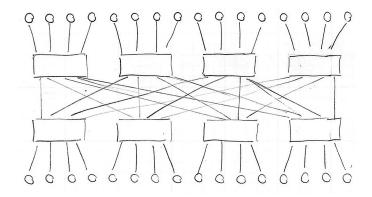

#### **Example Butterfly Topology: 3-ary 2-fly**

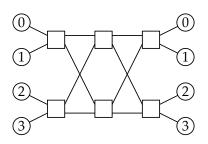

Sketch a 3-ary 2-fly. Use circles for the terminals, squares for the routers, and lines for one uni-directional channel.

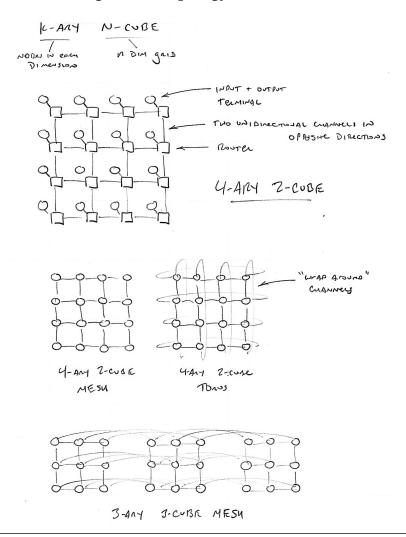

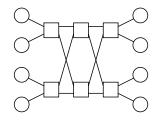

#### 2.4. Multi-Stage Torus Topology

#### **Example Torus Topology: 8-ary 1-cube torus**

Sketch a 8-ary 1-cube torus. Use circles for a terminal+router and lines for the two uni-directional channels in opposite directions.

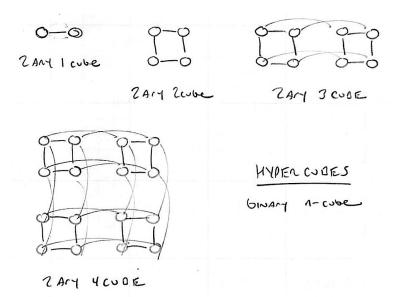

#### Constructing k=ary n-cube from k k-ary (n-1) cubes

### 2.5. Terminology

#### Nodes and Channels

- Uni-directional channels in butterfly

- Bi-directional channels in mesh

- Indirect Network: node is either a terminal or router (butterfly)

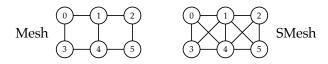

- Direct Network: node combines a terminal and router (mesh)

- Channel parameters

- $-w_c$  = channel width (number of pins/wires)

- $f_c$  = channel frequency

- $-t_c$  = channel latency

- $l_c =$ channel length

- $b_c$  = channel bandwidth ( $w_c \times f_c$ )

#### **Bisection Cuts**

- Cut: set of channels that partitions terminals into two sets

- Bisection Cut: cut that partitions terminals in two equal halves

- Min Bisection Cut (*B<sub>c</sub>*): min channel count over all bisection cuts

- Bisection Bandwidth (*B<sub>B</sub>*): min bandwidth over all bisection cuts

- For networks with uniform channel bandwidth:  $B_B = B_c \times b_c$

- Bisection bandwidth is a good way to estimate global wiring resources (i.e., technology constraints)

- Example from previous butterfly/mesh topologies

- Cut A on butterfly is a minimum bisection cut

- Both cut A and B on mesh are bisection cuts

- Cut A on mesh is a minimum bisection cut

### Paths

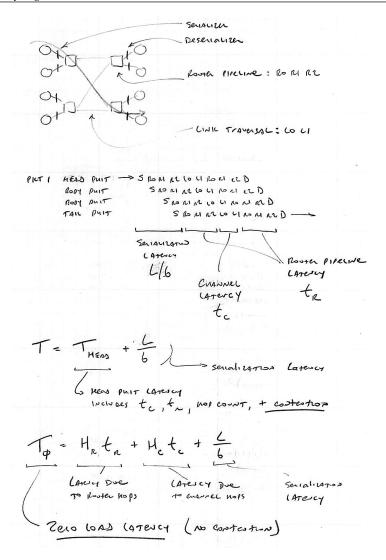

- Channel Hop Count ( $H_c$ ): number of channels on a path

- Channels from terminal to first router may or may not be included

- Router Hop Count  $(H_r)$ : number of routers on a path

- Minimal Path: smallest hop count between two terminals

- Diameter ( $H_{max}$ ): largest minimal path between all terminal pairs

- Average min hop count  $(H_{min})$ : average over all terminal pairs

- Example from previous butterfly/mesh topologies

- Path from A to B on mesh:  $H_r = 5$ ,  $H_c = 4$

- $H_{max,bfly} = 4, H_{max,mesh} = 8$

- $H_{min,bfly} = 4$

Calculating  $H_{min}$  usually requires enumerating the minimal hop count for every source/destination pair. The book states that  $H_{min}$  for a torus with even *k* is nk/4 and for a mesh with even *k* is nk/3. Where does this come from?

"terminal channels" circles = terminals squares = routers

CALCULATING MININ, R 0123 Including i = i 32/16 = 2 01232 1×4 = 4 Dest 2 21 23 2×8 = 16 2 3 21 2 3×9 = 12 - 16 3×4 = 12 excluding ini 28/12 = 2.3 32321 CALCULATING HANN, C win terminal mannels 0123 welding in 40/16 = 2.5 0 2 3 4 31 2×4 = 8 3×8 = 24 4×4 = 16 Dest 1 3234 4×4 = 16 excluding i= i 40/12 = 3.3 33432 CALCULATING MAINIC WITHOUT TERMINAL CHANNELS Src 0123  $1 \sim 10^{-10} c^{-10} c^{-10}$ 1×8 = 8 2×4 = 8 0 0121 Dest 1 012 2 2 101 31210 EQUATION FROM BOOK 15 The Even n  $\frac{n!k}{3} = \frac{2\cdot2}{3} = 1.33$ This is for  $H_{MWC}$ Without terminal consumers  $+ ignormag \ \hat{c} \text{ sensing to itsuck}$

### Path Diversity

- Path diversity is number of paths between any two terminals

- Mesh has high path diversity, butterfly has no path diversity

ADDING EXTRA BELY STAGES 1 PAM DIVENSITY

#### **Example Topologies**

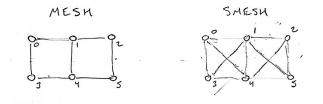

Assume  $b_c$  for mesh is 32 bits/cycle, while  $b_c$  for smesh is 16 bits/cycle. smesh has reduced channel bandwidth due to increased number of channels, assumes specific technology constraint. Calculate the following parameters for each topology.

|       | $B_C$ | $B_B$ | $H_{max}$ | $H_{min}$ |

|-------|-------|-------|-----------|-----------|

| mesh  |       |       |           |           |

| smesh |       |       |           |           |

### 3. Network Routing

Network routing is the choice of path from source to destination along channels and routers. Routing algorithms can be oblivious (not factor in network state) or adaptive (factor in network state), and can also be deterministic or non-deterministic.

### 3.1. Oblivious Deterministic Routing

- Ring: always use minimal path, equidistant choose CW

- Butterfly: use destination to choose middle router

- Mesh: route in X first, then route in Y (Dimension-Ordered-Routing)

### 3.2. Oblivious Non-Deterministic Routing

- Ring: randomly choose CW vs CCW

- Butterfly: randomly choose middle router

- Mesh: randomly choose between XY-DOR and YX-DOR (O1-TURN)

### 3.3. Adaptive Routing

- Ring: look at queues, choose direction with least congestion

- Butterfly: look at queues, choose middle router with least congestion

- Mesh: look at queues during each hop to choose X vs Y

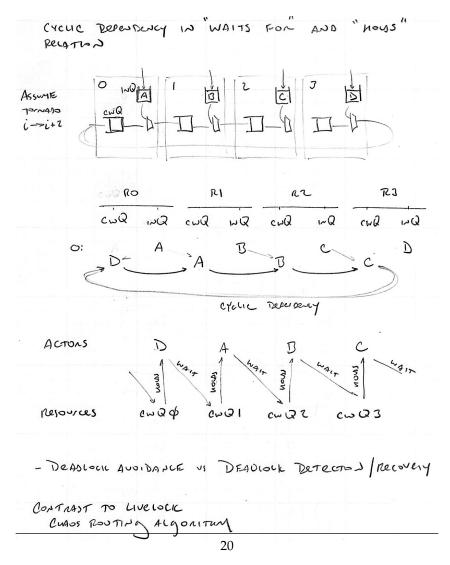

#### 3.4. Deadlock

### 4. Analyzing Network Performance

Similar to analyzing processors and memories, we will use simple first-order equations to help build intuition about throughput and latency trade-offs in networks.

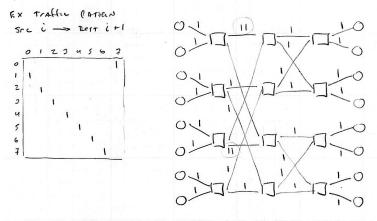

### 4.1. Traffic Patterns

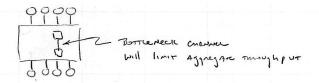

#### 4.2. Ideal Throughput

CHANNEL LOAS (4) IS ADDUT OF TRAFFIC MAT COSSES CHANNEL C. It Each WPJT WJECTS DIE WIT OF TRAFFIC ACCORDING TO GIVEN TRAFFIC PATTERN

CHANNEL LOAS NONGES FROM O-Z MAX CHANNEL LOAS (MMAY) IS Z. THESE ARE THE BOTTLE NECK CHANNEL, THAT WILL LIMIT THROUGH PUT

ALTENATIVE WAY TO THINK ABOUT M.

CHANNEL LOAD IS RATIO OF BU DEMANTED FROM CHANNEL

More goverally for UNFORM RANDOM TRAFFIC

- ON AVERAGE WITH UNIFOR RANDOM TRAFFIC, WALF THE

TRAFFIC COSSUS THE DISECTION

- N TOTAL UNITS OF TRAFFIC, N/2 COSSI TILECTON

- ITERC RONTING WIll EVEN H BALANCE GAD ACTOSS TILECTON

CHAMPLES (THIS HAS AN ISSUE IN RIVEY EXAMPLE)

- MMAX =

$$\frac{N/2}{T_c} = \frac{N}{ZB_c}$$

$O_{TEM} = \frac{6}{N/2B_c} = \frac{26B_c}{N} = \frac{2B_c}{N}$

$O_{TET} = N \frac{2B_c}{N} = 2T_{TS}$

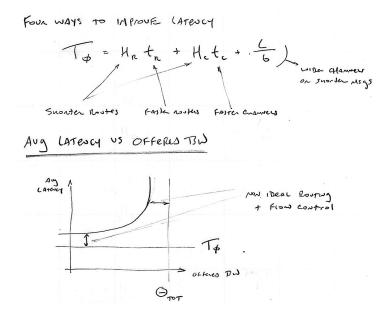

#### 4.3. Zero-Load Latency

### 4.4. Comparing Topologies

ASSUME :

L = 1286  $b_{c} = for mesu is 326 | crcle - reduces answell

<math display="block">b_{c} = 5 + reduces mesurel

barowism Die re

t_{c} = 1$   $h_{c} = 1$   $h_{c} = 1$

WHICH TOPOLOGY CAN ACHIEVE HIGHER IDEAL THROUGHPOT WOOR WIFORM RANDOM TRAHLE?

(a)  $\Theta_{\text{Term, Mein}} > \Theta_{\text{Term, Swein}}$ (b)  $\Theta_{\text{Term, Misn}} < \Theta_{\text{Term, Swein}}$ (c)  $\Theta_{\text{Term, Mein}} == \Theta_{\text{Term, Swein}}$

CALCULATE ZELO LOAD LATENCE UNDER UNIFORM RANDOM TRAFFIC

#### 4.5. Comparing Routing Algorithms

Do NOT CHANGE DIRECTION AFTER WITHE CHOICE

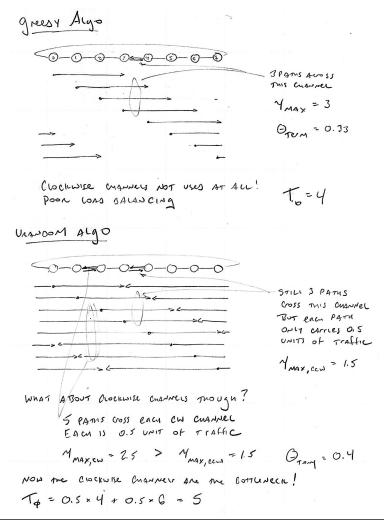

- Evaluate tornado traffic pattern on the 8-node ring

- Recall that in tornado, node *i* sends to  $i + ((N-1)/2) \mod N$

Weightes Asunon Alyo SAME NUMBER OF PARTS CROSS CW AND CCW ENANNELS AS BEFORE EXCEPT NOW WIM DIFFERENT AMOUNTS OF Traffic pa PATU. 5/8 3/8 3 PAMS Each WITH 5/B Traffic Mmax .... = 3. = 1.875 5 parus egen wirm 3/B traffic MMAX. C. = 5. B = 1.875 MMAX, CW = MMAX, CLW BALANCED! Qrem = 1 1825 = 0.53  $T_0 = \frac{5}{2} \times 4 + \frac{3}{6} = 2.5 + 2.25 = 4.75$

#### ADAPTIVE

MUMAL LATCHY AT LIGHT LOAD MAX THROUGH PUT AT LIGH LOAD Let's fill in the following table to summarize the performance of the four routing algorithms on the 8-node given the tornado and uniform random traffic patterns.

|                 | Tornado         |       | Uniform         | Random |

|-----------------|-----------------|-------|-----------------|--------|

| Routing Algo    | $\Theta_{term}$ | $T_0$ | $\Theta_{term}$ | $T_0$  |

| Greedy          |                 |       | 1.00            | 3.0    |

| Uniform Random  |                 |       | 0.57            | 4.5    |

| Weighted Random |                 |       | 0.76            | 3.1    |

| Adaptive        |                 |       | 1.00            | 3.0    |

**Tornado Traffic Pattern** Bandwidth vs. Latency **Uniform Random Traffic Pattern** Bandwidth vs. Latency

### Activity: Routing on butterfly with extra stage

Consider two routing algorithms for a 2-ary 2-fly with an extra stage:

- Destination Tag Routing: use destination to choose middle router

- Random Middle Router: randomly choose middle router

Compare these two routing algorithms in terms of ideal terminal throughput ( $\Theta_{term}$ ) and zero-load latency ( $T_0$ ) for the following permutation traffic pattern.

- $\operatorname{src} 0 \to \operatorname{dest} 1$

- src  $1 \rightarrow \text{ dest } 0$

- $\bullet \ src \ 2 \rightarrow \ dest \ 3$

- $\bullet \ src \, 3 \rightarrow \ dest \, 2$

*Hint: Use the tick-mark method to calculate the max channel load for each routing algorithm.*

### **Destination-Tag Routing**

#### **Random Middle Routing**