#### ECE 2300 Digital Logic & Computer Organization Spring 2025

**Timing Analysis**

#### Announcements

- Prelim 1 graded

- Mean: 39.2 (out of 50); Median: 40; High: 50

- Lab 3 teaming starts soon; complete it by next Wed to earn a bonus!

- Instructor OH today cancelled today

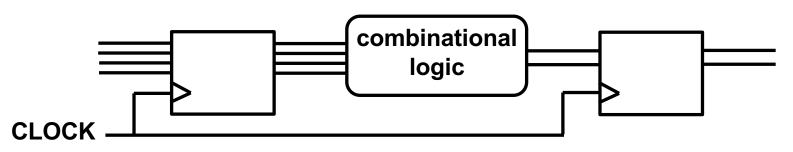

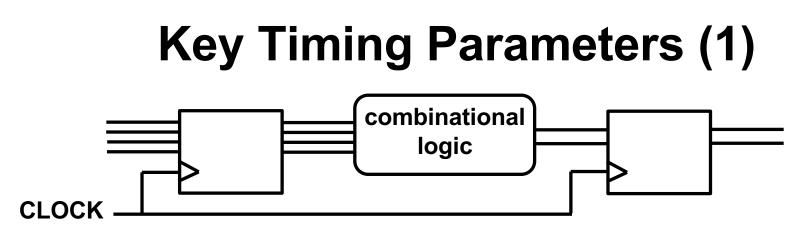

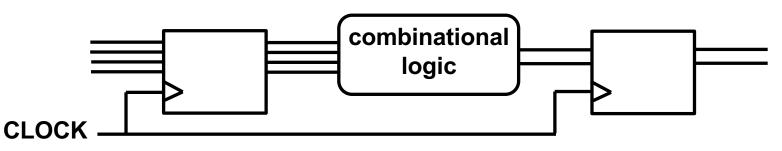

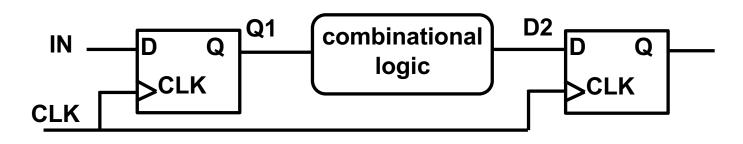

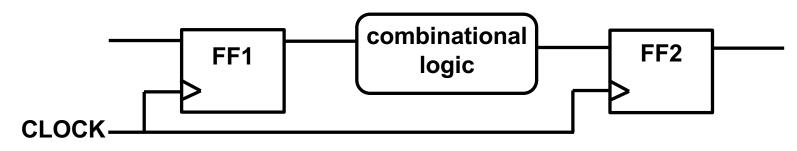

### **Synchronous Circuits**

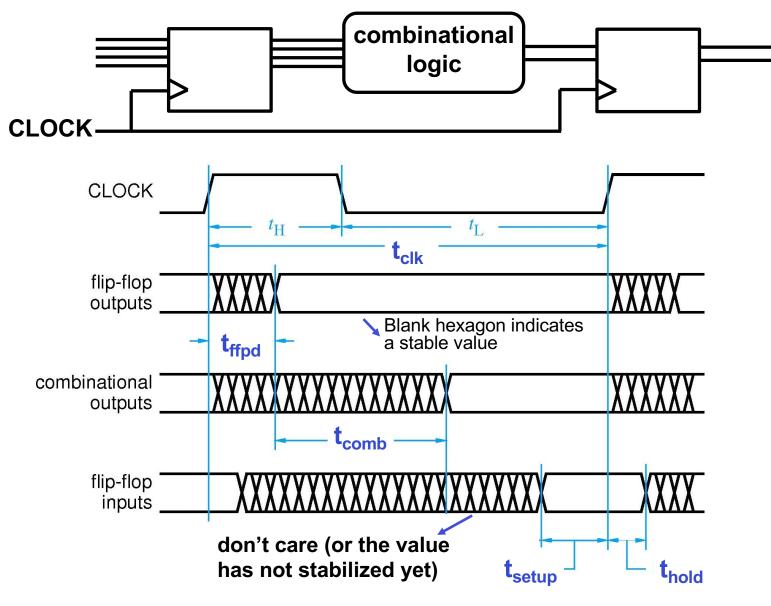

- The changes in the state of the memory elements are synchronized by a clock signal

- All flip-flops (FFs) are synchronized to capture the inputs *simultaneously* on the clock tick

- Must ensure the output of the combinational logic has settled before the next clock tick

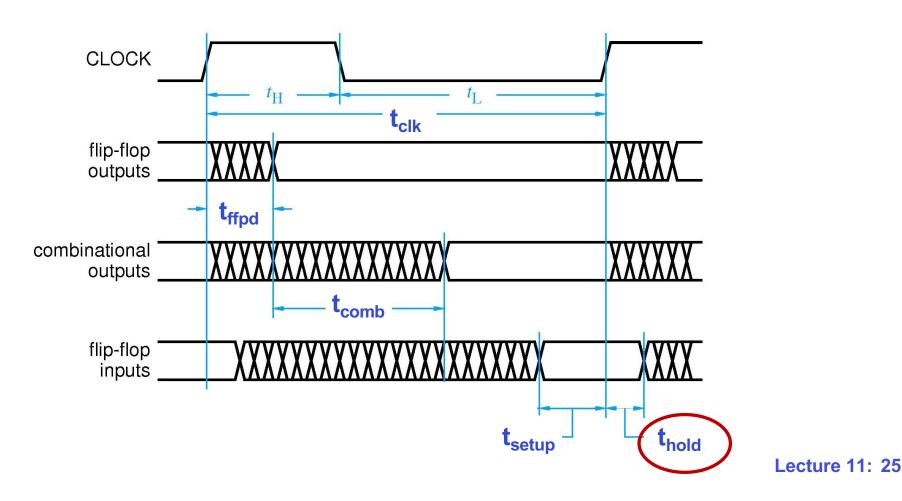

- Clock cycle time (t<sub>clk</sub>): also known as the clock period or the clock pulse width

- Combinational logic propagation delay (t<sub>comb</sub>): the time it takes for a signal to travel through a combinational logic block from input to output.

#### These are typically design specific

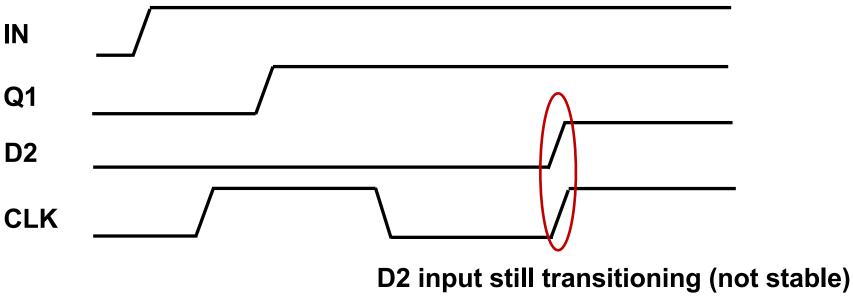

# **Key Timing Parameters (2)**

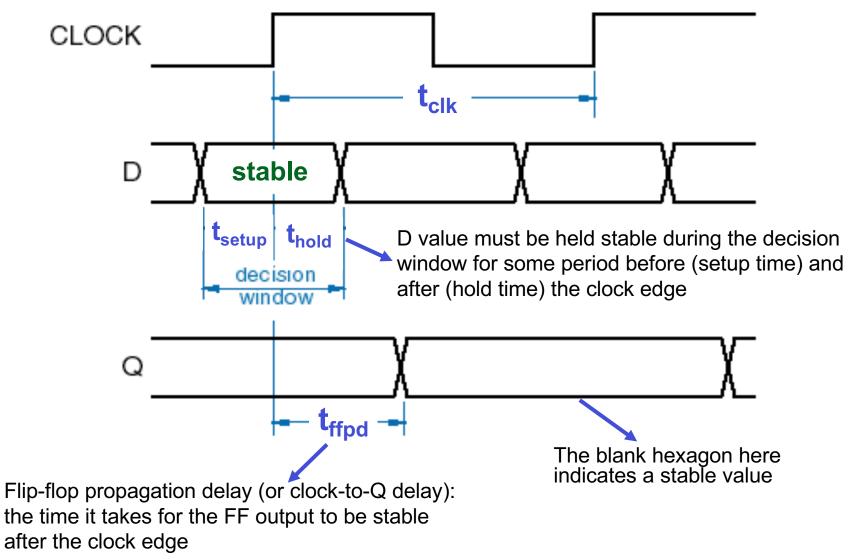

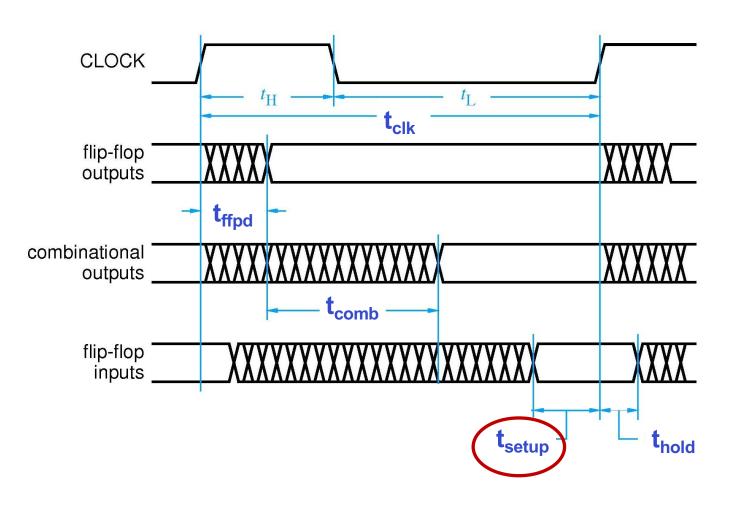

- Setup time (t<sub>setup</sub>): The minimum time <u>before</u> the (triggering) clock edge that the data input must be stable

- Hold time (t<sub>hold</sub>): The minimum time <u>after</u> the clock edge that the data input must remain stable

- Flip-flop propagation delay (t<sub>ffpd</sub>): the time it takes for the FF output to be stable after the clock edge

The above parameters are typically specified in datasheets by the manufacturer

#### **Stable FF Situation**

#### What if This Happens?

FF may capture neither 0 nor 1

#### **Metastable State**

# **Avoiding Timing Failure**

- Possible causes of metastability and wrong value capture

- Clock pulse that is too narrow

- Input changes too soon before a clock edge

- Input changes too soon after a clock edge

- Require timing analysis to ensure the design meets setup time, hold time, and minimum clock pulse width specifications

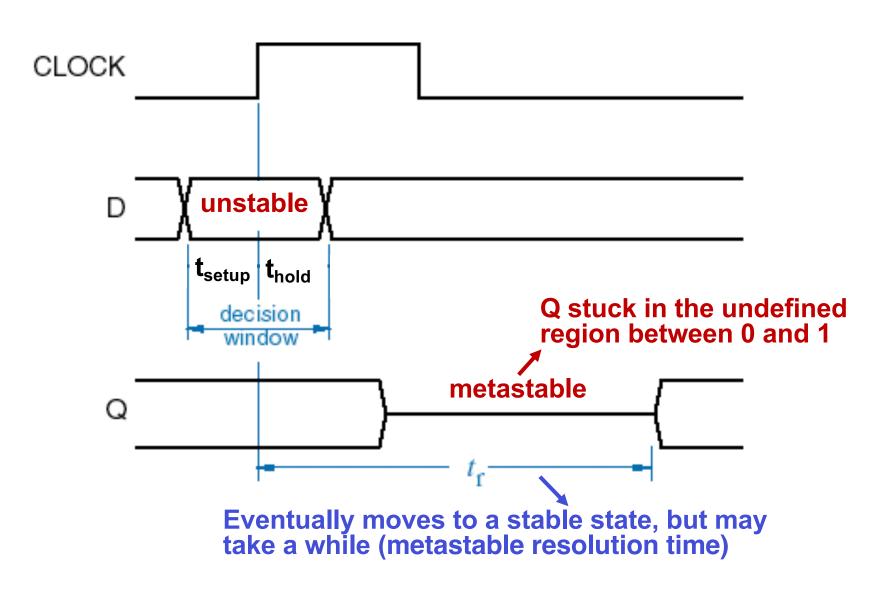

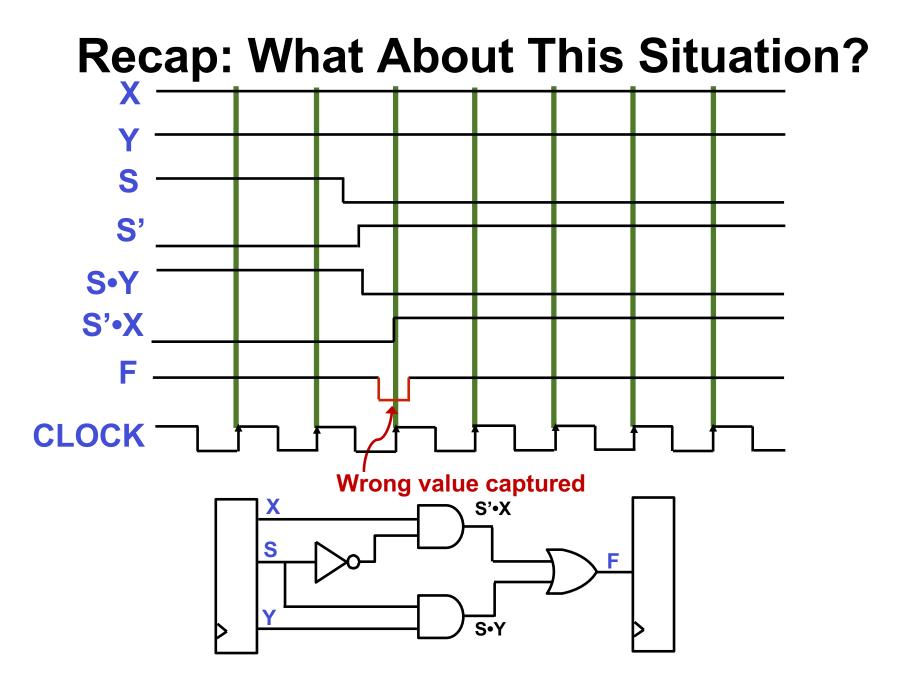

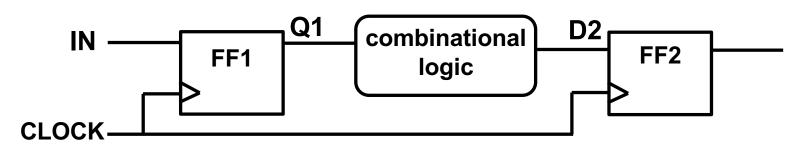

## **Sequential Circuit Timing Analysis**

- Timing analysis involves calculating the time delays between all FF pairs within the circuit

- To determine the maximum operating frequency and ensure that <u>setup time requirements</u> are met

The clock cannot be too fast

- To ensure that <u>hold time requirements</u> are met

- The minimum propagation delay of the combinational logic (contamination delay) cannot be too small

- Independent of clock cycle time

## **Important Timing Parameters**

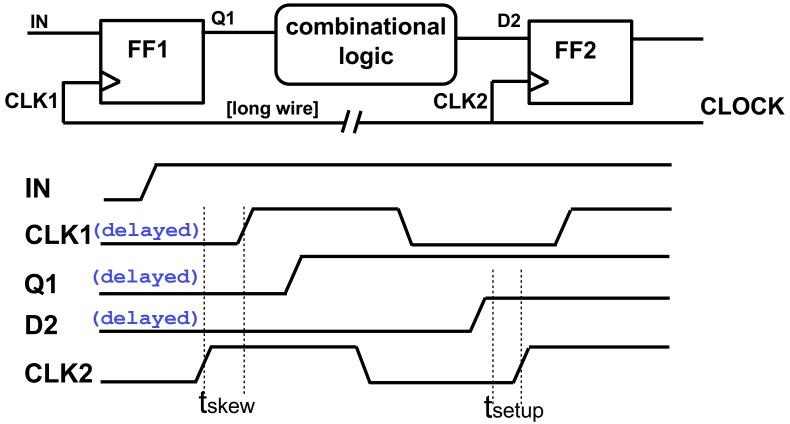

## **Setup Time Constraint**

t<sub>setup</sub> is the minimum amount of time <u>before</u> the triggering edge during which FF input must be stable

Lecture 11: 13

#### Meeting Setup Time Constraint **Q1 D2** combinational IN FF2 FF1 logic **CLOCK** t<sub>clk</sub> IN **CLK C**ffpd **Q1** t<sub>comb</sub> **D2** setup D2 must stabilize <u>before</u> the $t_{setup}$ window $t_{clk} - t_{setup} \ge t_{ffpd(max)} + t_{comb(max)}$

We use the maximum delay here because it represents the worst-case scenario for meeting setup time. If the maximum propagation delay satisfies the inequality, the minimum delay case automatically holds, since  $t_{ffpd(max)} + t_{comb(max)} \ge t_{ffpd(min)} + t_{comb(min)}$

## **Determining Clock Cycle Time**

- t<sub>clk</sub> ≥ t<sub>ffpd(max)</sub> + t<sub>comb(max)</sub> + t<sub>setup</sub>

Every circuit path between every pair of FFs must satisfy the above equation to run the circuit at a frequency of 1/t<sub>clk</sub>

- Consider <u>maximum propagation delays</u> (the longest timing path) to determine the maximum clock frequency

- Worst case temperature and voltage

- Worst case manufacturing variations

## **Example: Cycle Time Calculation**

|      | Prop Delay (ns) |     | Setup        | Hold         |

|------|-----------------|-----|--------------|--------------|

|      | min             | max | Time<br>(ns) | Time<br>(ns) |

| FF   | 1               | 2   | 3            | 1            |

| Comb | 3               | 7   | -            | -            |

#### What's the best achievable cycle time?

### **Example: Cycle Time Calculation**

|      | Prop Delay (ns) |     | Setup        | Hold         |

|------|-----------------|-----|--------------|--------------|

|      | min             | max | Time<br>(ns) | Time<br>(ns) |

| FF   | 1               | 2   | 3            | 1            |

| Comb | 3               | 7   | -            | -            |

$t_{clk} \ge t_{ffpd(max)} + t_{comb(max)} + t_{setup} = 2 + 7 + 3 = 12ns$

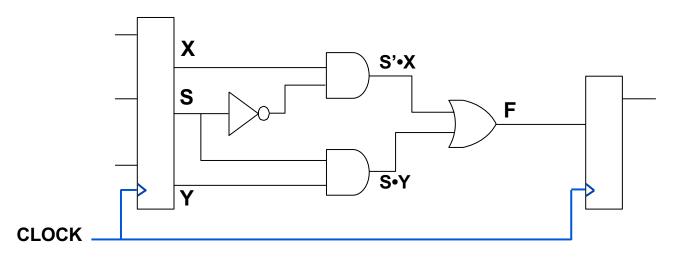

#### **Exercise: Cycle Time Analysis**

**Assumptions:**

- (1) FF propagation delay = 1ns

- (2) Uniform gate delay = 1ns

- (3) Setup time = 2ns, hold time = 2ns

What's the best achievable cycle time?

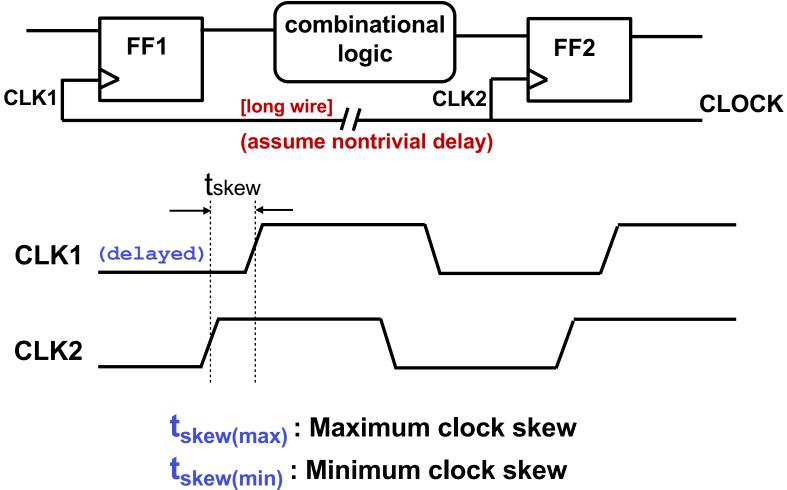

#### Clock Skew Complicates Matters Further

Clock may not reach all flip-flops simultaneously

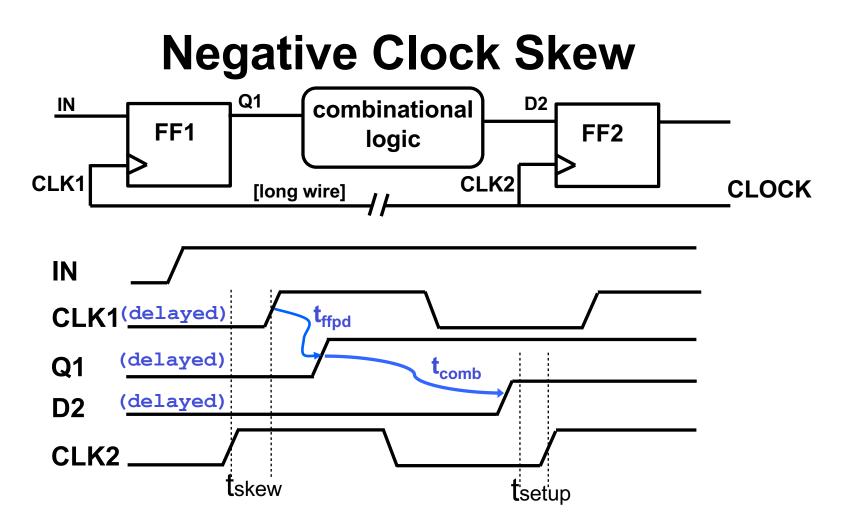

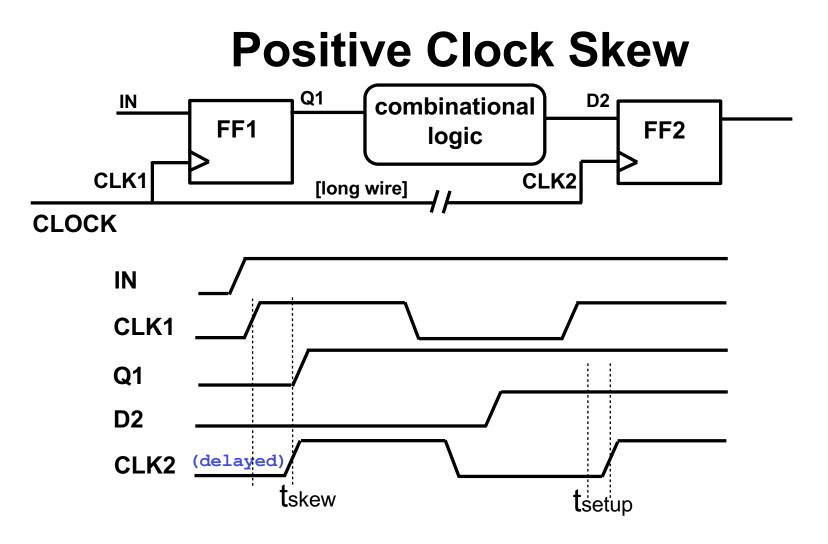

## Setup Time Analysis With Clock Skew

Sending FF receives clock later than receiving FF  $t_{ffpd(max)} + t_{comb(max)} + t_{setup} \le t_{clk} - t_{skew(max)}$

Harmful skew for meeting setup time constraint

Sending FF receives clock sooner than receiving FF  $t_{ffpd(max)} + t_{comb(max)} + t_{setup} \le t_{clk} + t_{skew(min)}$

Beneficial skew for meeting setup time constraint

#### **Example: Setup Analysis with Clock Skew**

#### Clock arrives at FF1 at least 4ns earlier than FF2

|      | Prop Delay (ns) |     |               | Hold Time |

|------|-----------------|-----|---------------|-----------|

|      | min             | max | Time (ns) (ns | (ns)      |

| FF   | 1               | 2   | 3             | 1         |

| Comb | 3               | 7   | -             | -         |

• What's the best achievable cycle time?

#### **Example: Setup Analysis with Clock Skew**

#### Clock arrives at FF1 at least 4ns earlier than FF2

|      | Prop Delay (ns) |     |               | Hold Time |

|------|-----------------|-----|---------------|-----------|

|      | min             | max | Time (ns) (ns | (ns)      |

| FF   | 1               | 2   | 3             | 1         |

| Comb | 3               | 7   | -             | -         |

What's the best achievable cycle time?

$$\begin{split} t_{\rm ffpd(max)} + t_{\rm comb(max)} + t_{\rm setup} &<= t_{\rm clk} + t_{\rm skew(min)} \\ t_{\rm clk} &>= 2 + 7 + 3 - 4 = 8 \text{ns} \end{split}$$

## **Hold Time Constraint**

t<sub>hold</sub> is the minimum amount of time <u>after</u> the triggering edge during which FF input must remain stable

- FF input must remain stable after the triggering edge by at least t<sub>hold</sub> amount of time

- Otherwise, the receiving flip-flop may be contaminated with an unexpected value

- Need to <u>consider minimum propagation delays</u> (the shortest timing path) for hold time calculations

**CLOCK**

#### **Next Class**

### More Timing Analysis Binary Arithmetic (H&H 1.4)