## ECE 2300 Digital Logic & Computer Organization Spring 2025

#### **CMOS Logic**

#### Announcements

• Links to lecture recordings & previous quiz questions are in the pinned post on Ed

# A Little Bit of History

#### Transistors

- Invented by John Bardeen, Walter Brattain, and William Shockley at Bell Labs in 1947

- Integrated circuits (IC)

- Independently developed by Jack Kilby (at TI) and Robert Noyce (at Fairchild) in the 1950s

- Robert Noyce and Gordon Moore founded Intel in 1968

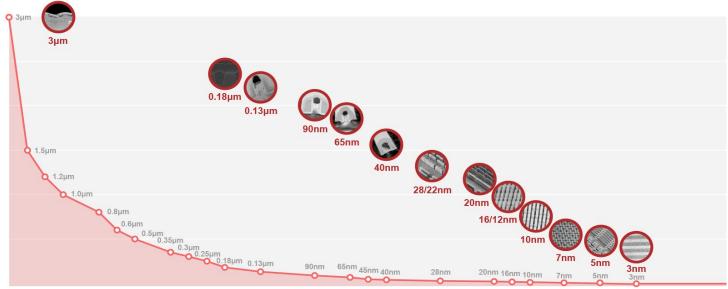

#### **Technology scaling of CMOS transistors**

https://www.tsmc.com/english/dedicatedFoundry/technology/logic

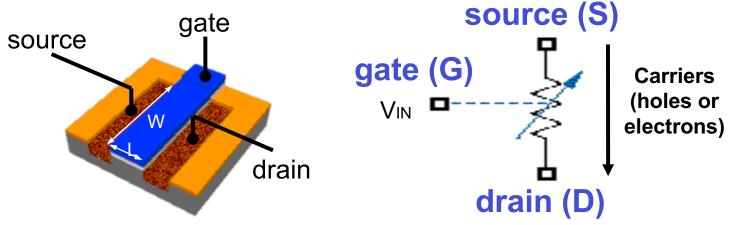

#### **MOS Transistors**

- Metal-Oxide Semiconductor Field-Effect Transistors (MOSFETs)

- MOS for short

A 3-terminal device that changes its conductance (or resistance) based on the voltage applied to the gate terminal

Extreme changes in resistance (0 to ∞) make transistors act like switches

#### MOSFET

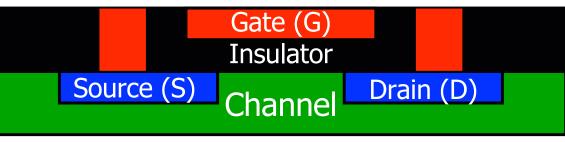

#### (cross-section view of a MOSFET)

#### **MOS: three materials needed to make a transistor**

- <u>Metal</u>: strong conductor of current

- Oxide: insulator (does not conduct)

- <u>Semiconductor</u>: conduction can be controlled

#### **FET: Field Effect Transistor**

- <u>Acts as a voltage-controlled switch</u>: gate voltage creates electric field that turns on/off connection between source and drain

- Two types of switches: active low and active high (active = connection is on)

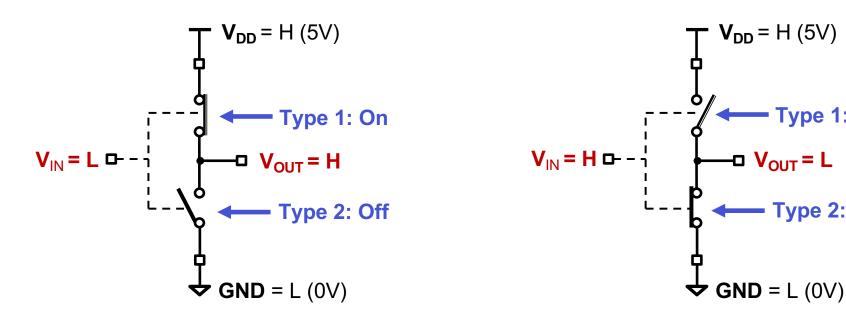

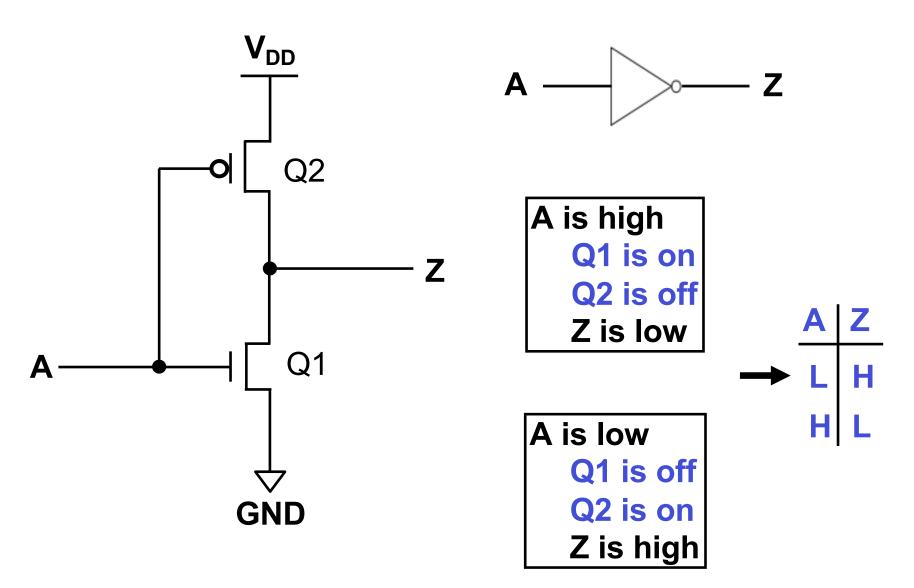

#### **NOT Gate Using Switches**

- Can build an inverter using two types of complementary switches

- **Type 1 (active low):** ON when input = 0, OFF when input = 1

- Type 2 (active high): ON when input = 1, OFF when input = 0

When input voltage is low, output is connected to voltage supply (V<sub>DD</sub>)

When input voltage is high, output is connected to ground (GND)

Type 1: Off

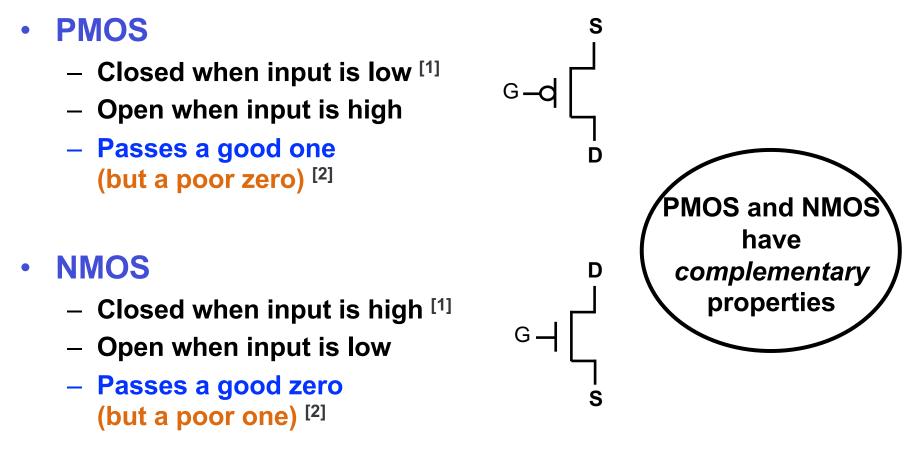

## **Two Types of MOS Transistors**

- <u>PMOS</u>: Type 1 switch; <u>NMOS</u>: Type 2 switch

- Current flows when ON (conducting)

- No current flows when OFF (not conducting)

O Bubble indicates active low

# Two Types of MOS Transistors

[1] In both cases, the voltage difference between gate and source must exceed a certain threshold voltage before the transistor starts having any effect.

[2] Optional reading: vlsimsee.blogspot.com/2013/05/why-cant-nmos-pass-1-and-pmos-pass-0.html

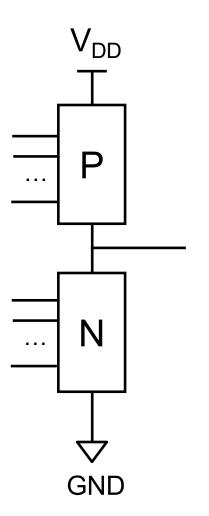

# **CMOS Logic Gates**

- Complementary MOS (CMOS)

- CMOS dominates the digital IC market

- Uses both NMOS and PMOS devices such that there is no direct supply-ground path

- Dissipates little power when the inputs don't change

- Our focus: Static CMOS gates

- Other types exist as well (pseudo-NMOS, domino, ...)

#### **CMOS** Inverter

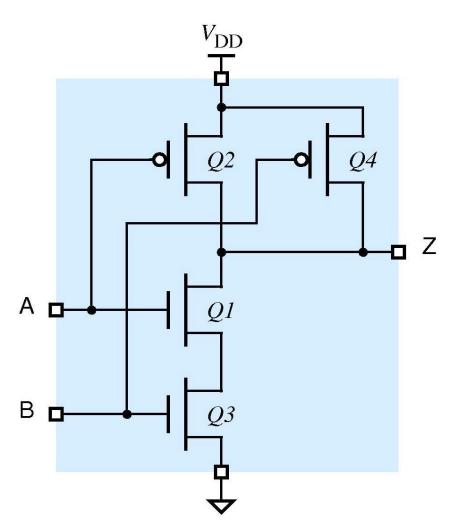

#### **CMOS NAND Gate**

| A B | Q1                     | Q2        | Q3        | Q4  | Z |

|-----|------------------------|-----------|-----------|-----|---|

| LΗ  | off<br>off<br>on<br>on | on<br>off | on<br>off | off |   |

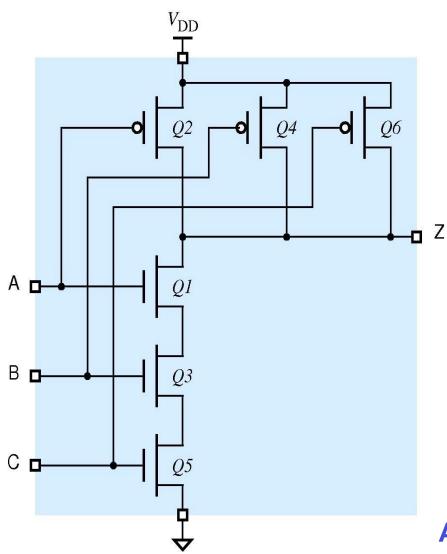

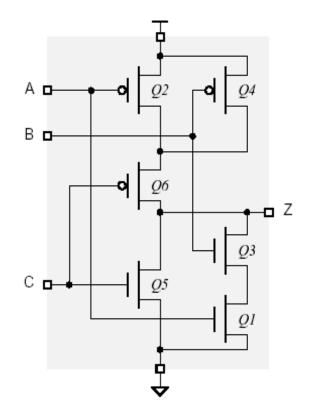

#### **3 Input CMOS NAND Gate**

| А | В | С | Q1  | Q2  | Q3  | Q4  | Q5  | Q6  | Z |

|---|---|---|-----|-----|-----|-----|-----|-----|---|

| L | L | L | off | on  | off | on  | off | on  | Н |

| L | L | Н | off | on  | off | on  | on  | off | Н |

| L | Н | L | off | on  | on  | off | off | on  | Н |

| L | Н | Н | off | on  | on  | off | on  | off | Н |

| Н | L | L | on  | off | off | on  | off | on  | Н |

| Н | L | Н | on  | off | off | on  | on  | Off | Н |

| Н | Н | L | on  | off | on  | off | off | on  | Н |

| Н | Η | Η | on  | off | on  | off | on  | Off | L |

#### An *n*-input NAND uses 2*n* transistors

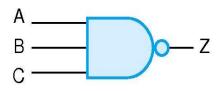

#### Another "Mystery" Gate

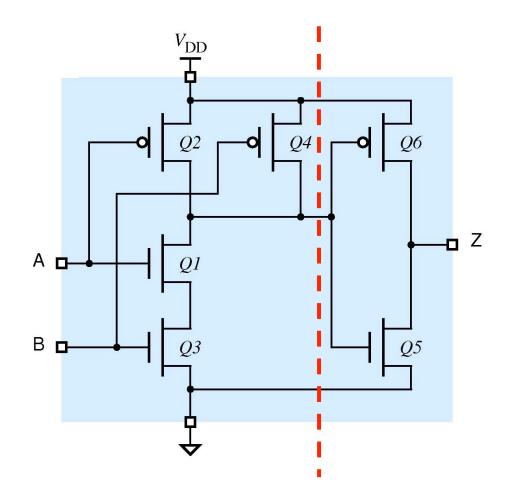

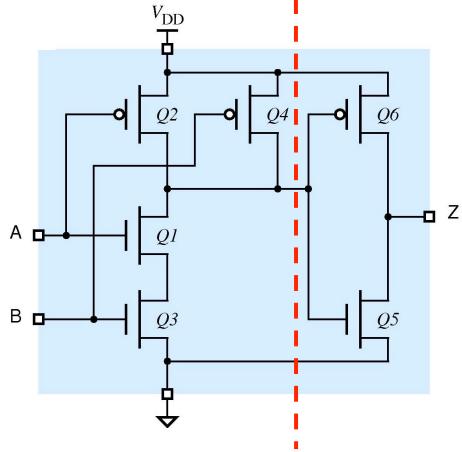

## 2-Input AND Gate in CMOS

- CMOS gates produce inherent inversion

- Need to invert to the output of NAND to implement an AND gate

| A B                      | Q1        | Q2        | Q3        | Q4        | Q5       | Q6         | Z      |

|--------------------------|-----------|-----------|-----------|-----------|----------|------------|--------|

| L L<br>L H<br>H L<br>H H | off<br>on | on<br>off | on<br>off | off<br>on | on<br>on | off<br>off | L<br>L |

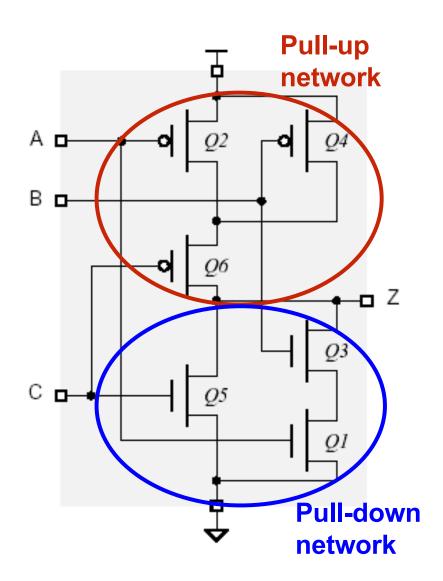

# **Structure of Transistor Networks**

- Two complementary networks

- A <u>pull-up network</u> composed of PMOS, with sources tied to voltage supply

- A <u>pull-down network</u> composed of NMOS, with sources tied to ground

- Equal number of NMOS and PMOS transistors

## **Structure of Transistor Networks**

- The pull-up and pull-down

networks are always duals

- To construct the dual of a network:

- Exchange NMOS for PMOS (and vice versa)

- Exchange series subnets for parallel subnets (and vice versa)

- This transformation applies to hierarchical structures

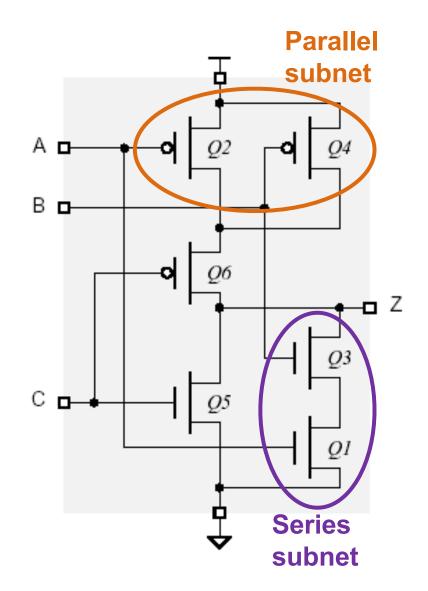

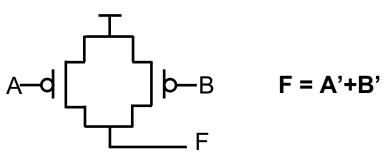

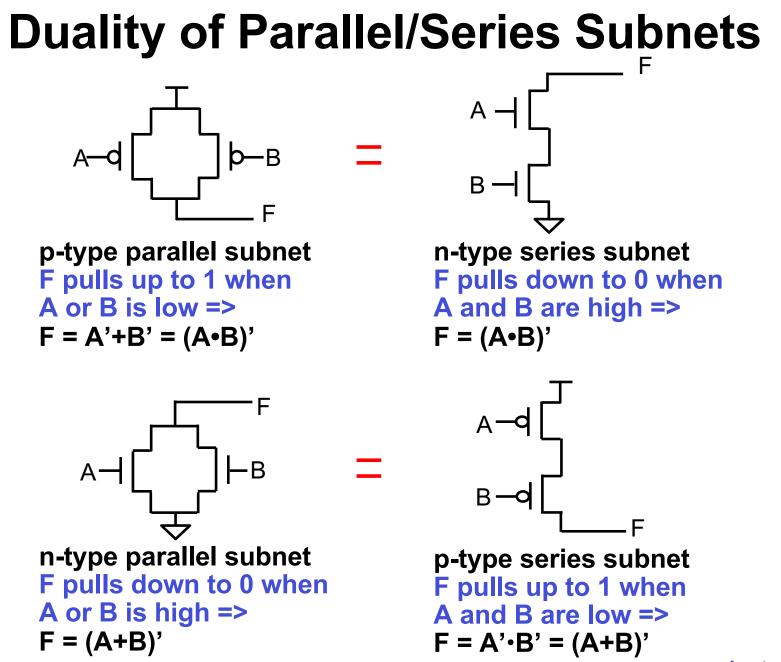

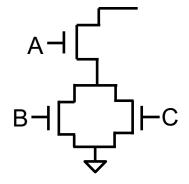

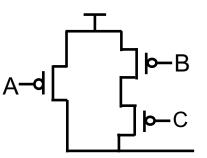

#### **Series and Parallel Subnets**

#### Parallel

At least one input must be 0 (p-type) or 1 (n-type) to make the connection

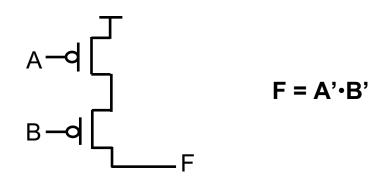

- Series

- All inputs must be 0 (p-type) or 1 (n-type) to make the connection

#### **Analysis of Transistor Networks**

#### Transistor states

- Determine all possible input combinations

- Figure out the state of each transistor

- Determine final output

- or by inspection

- Figure out what input combinations cause a 1 (or a 0) output

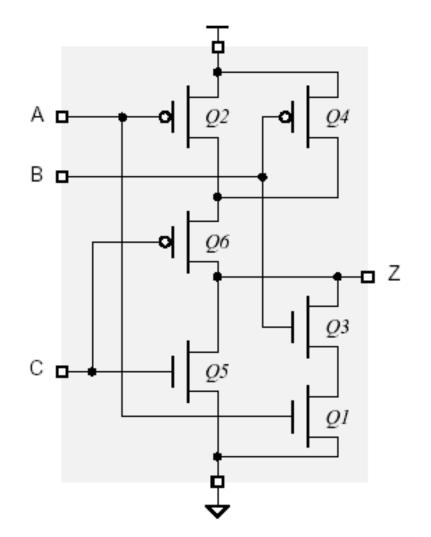

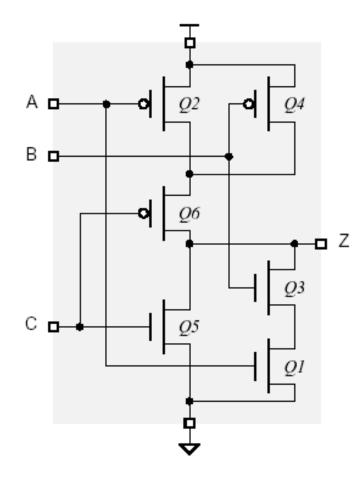

## **Analysis of Transistor Networks**

#### By inspection

- Inspect *either* pull-up (PMOS)

*or* pull-down (NMOS) network

- Translate the series (parallel) subnets into product (sum) terms

- For pull-down network, negate the combined expression

Pull-up: (A'+B')C' || Pull-down: (A•B + C)'

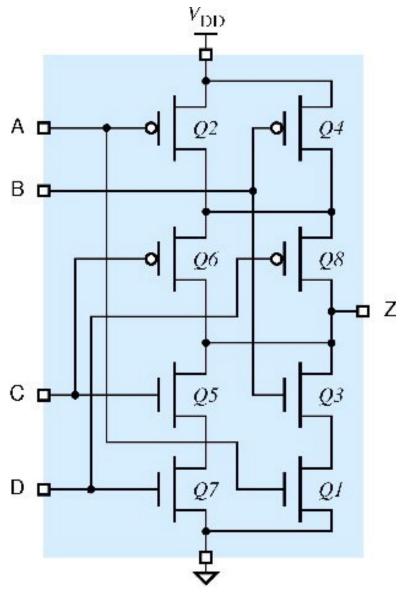

### **A More Complicated Circuit**

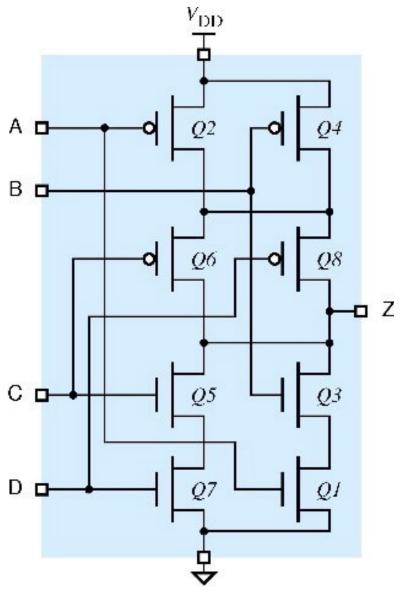

## **A More Complicated Circuit**

Pull-up: (A'+B')•(C'+D')

Pull-down: (A•B + C•D)'

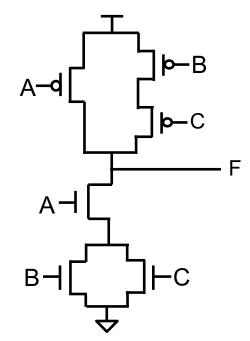

#### Constructing CMOS Gate from Boolean Expression

#### Example: F = (A•(B+C))'

**Step 1.** Figure out pulldown network that does what you want (e.g., what combination of inputs generates a low output)

**Step 3.** Combine PMOS pull-up network (from Step 2) with NMOS pull-down network (from Step 1) to form a fullycomplementary CMOS gate

**Step 2.** Walk the hierarchy replacing NMOS with PMOS, series subnets with parallel subnets, and parallel subnets with series subnets

# **CMOS Sanity Checks**

- Equal number of NMOS and PMOS

- NMOS sources tied to ground or to drain of another NMOS

- PMOS sources tied to Vdd or drain of another PMOS

- Inputs tied to pairs of PMOS and NMOS transistors

#### **Next Class**

#### Sequential Logic: Clocks, Latches, Flip-Flops (H&H 3.1-3.2)