Iterative MIMO Decoding: Algorithms and VLSI Implementation Aspects

Christoph Studer

# Iterative MIMO Decoding: Algorithms and VLSI Implementation Aspects

Hartung-Gorre Verlag Konstanz 2009

Reprint of Diss. ETH No. 18512

#### SERIES IN MICROELECTRONICS

#### VOLUME 202

edited by Wolfgang Fichtner Qiuting Huang Heinz Jäckel Hans Melchior George S. Moschytz Gerhard Tröster Bernd Witzigmann

#### Bibliographic Information published by Die Deutsche Nationalbibliothek

Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data is available in the internet at: http://dnb.d-nb.de.

Copyright © 2009 by Christoph Studer

First edition 2009

HARTUNG-GORRE VERLAG KONSTANZ http://www.hartung-gorre.de

ISSN 0936-5362 ISBN-10: 3-86628-288-5 ISBN-13: 978-3-86628-288-9 To Séverine  $\heartsuit$

# Acknowledgments

First, I would like to thank my advisors Prof. Dr. W. Fichtner and Prof. Dr. H. Bölcskei for their support, for giving me the opportunity to pursue my Ph.D. Thesis on such interesting research topics, and for providing very stimulating research environments at the Integrated Systems Laboratory (IIS) and the Communication Theory Group (CTG). It is also my pleasure to express my thanks to Prof. Dr. E. Viterbo who kindly agreed to act as an external co-examiner of my Ph.D. Thesis. My very special thanks go to Prof. Dr. A. Burg and Dr. D. Seethaler for the fruitful discussions on MIMO detection and corresponding implementation aspects, their invaluable support during my Ph.D. studies, and for continuously providing me with creative ideas. Furthermore, I would like to thank the staff members of the IIS and the Design Zentrum (DZ) N. Felber, H. Kaeslin, as well as all my colleagues from the IIS and the DZ who contributed in many ways to this work, namely, C. Benkeser, F. Bürgin, M. Brändli, S. Eberli, F. Gürkaynak, S. Häne, P. Lüthi, D. Perels, C. Senning, J. Treichler, M. Wegmüller, and M. Wenk. I also want to express my thanks to my colleagues M. Borgmann, M. Gärtner, and U. Schuster from the CTG, who sparked my interest for communication theory. I finally appreciate all contributions to my Ph.D. Thesis of the following students: S. Belfanti, S. Fateh, N. Preyss, D. Riha, C. Roth, and S. Schläpfer.

# Abstract

The use of multiple antennas at both ends of the wireless link is known as multiple-input multiple-output (MIMO) wireless technology and enables to transmit multiple data streams concurrently and within the same frequency band. This method is known as spatial multiplexing (SM) and improves the spectral efficiency and link reliability of wireless communication systems without requiring additional transmit power. Channel coding can be deployed to further improve the reliability of SM, which is one of the most promising technologies to meet the demands of future wireless communication systems for higher data-rates and improved quality of service.

Joint MIMO detection and channel decoding (JDD) is the optimum method for data detection (in terms of error-rate performance) in systems employing channel coding and SM. The (often) prohibitive computational complexity associated with JDD inhibits practical implementation. Iterative MIMO decoding requires significantly less computational complexity (compared to that of JDD) and was shown by Hochwald and ten Brink, *IEEE Trans. Comm.*, 2003, to enable near-optimum detection performance. The main idea underlying this approach is to separate MIMO detection from channel decoding and to iteratively exchange reliability information (i.e., soft-information) between a soft-input soft-output (SISO) detector for MIMO systems and a SISO channel decoder. So far, not much is known about the very-large-scale integration (VLSI) implementation complexity associated with iterative MIMO decoding.

In this thesis, we design and optimize algorithms for iterative MIMO decoding and investigate the associated performance and VLSI implementation aspects.

First, we optimize the detection algorithm developed by Wang and Poor, *IEEE Trans. Comm.*, 1999, for low-complexity soft-input softoutput MIMO detection. To this end, we propose a novel method that substantially reduces the computational complexity, without sacrificing performance. We design a corresponding high-throughput VLSI architecture and provide application-specific integrated circuit (ASIC) implementation results. This reference design demonstrates that SISO detection for iterative MIMO decoding is feasible in practice.

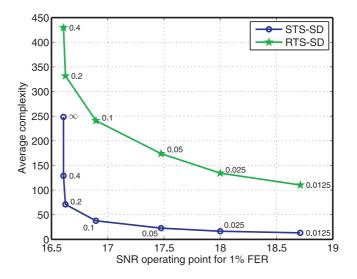

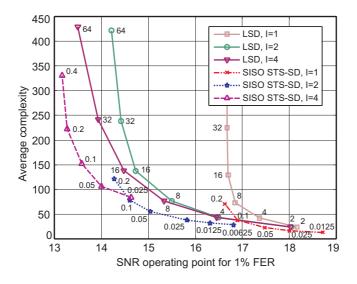

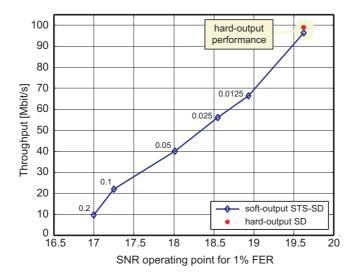

Secondly, we present a low-complexity SISO detection algorithm based on the principles of sphere decoding (SD), initially developed by Pohst, *ACM SIGSAM*, 1981. Our algorithm resorts to the single treesearch (STS) paradigm and incorporates clipping of soft-information into the tree-search, which results in significant complexity savings and allows to cover a large performance/complexity tradeoff region. In order to further reduce the complexity and to improve the performance of SISO STS-SD, we deploy a variety of techniques. The resulting algorithm clearly outperforms state-of-the-art SISO detection schemes for iterative MIMO decoding. Moreover, reference VLSI implementation results of soft-output STS-SD show that the proposed algorithm is well-suited for high-performance MIMO detection in practical systems.

Finally, we study the performance and VLSI implementation complexity associated with SISO channel decoding. To this end, we develop high-performance VLSI architectures for SISO decoding of convolutional codes, quasi-cyclic low density parity-check codes, and turbo codes. Corresponding ASIC implementation results demonstrate that high-throughput SISO channel decoding is feasible in practical systems.

Based on the results obtained throughout this thesis, we show that iterative MIMO decoding is feasible in practical systems and provide estimates of the silicon-complexity required for iterative MIMO decoding. In particular, we demonstrate that the silicon area of iterative MIMO decoding grows approximately linear in the number of iterations, while even a very small number of iterations is sufficient to approach the fundamental performance limits of MIMO wireless communication systems.

# Zusammenfassung

Die MIMO (multiple-input multiple-output)-Technologie verwendet mehrere Antennen an beiden Seiten einer drahtlosen Verbindung und ermöglicht es, mehrere Datenströme gleichzeitig und im selben Frequenzband zu übertragen. Diese Technik—bekannt als räumliches Multiplexen— verbessert die spektrale Effizienz sowie die Zuverlässigkeit der Übertragung ohne die Sendeleistung zu erhöhen. Zusätzlich kann Kanalcodierung verwendet werden, um die Zuverlässigkeit der Übertragung weiter zu steigern. Räumliches Multiplexen im Verbund mit Kanalcodierung ist eine der wichtigsten Technologien, um den Ansprüchen von zukünftigen drahtlosen Kommunikationsystemen auf höheren Durchsatz und bessere Übertragungsqualität gerecht zu werden.

MIMO-Detektion mit gleichzeitiger Kanaldecodierung ist die optimale Methode um die Fehlerrate in solchen Systemen zu minimieren. Die benötigte Rechenleistung erlaubt es jedoch nicht, diese Methode in praktischen Systemen zu verwenden. Methoden, welche auf iterativer MIMO-Decodierung basieren, benötigen signifikant weniger Rechenleistung und erreichen dabei, wie Hochwald und ten Brink, *IEEE Trans. Comm.*, 2003, gezeigt haben, fast gleichwertige Fehlerraten. Die Kernidee dieser Verfahren besteht darin, MIMO-Detektion und Kanaldecodierung zu trennen und Zuverlässigkeitsinformation (softinformation) zwischen den beiden Komponenten auf iterative Weise auszutauschen; dies benötigt einen sogenannten SISO (soft-input softoutput)-MIMO-Detektor sowie einen SISO-Kanaldecoder. Bis Heute ist jedoch nicht viel über die Komplexität von VLSI (very-large scale integration)-Schaltungen für iterative MIMO-Decodierung bekannt. Im Rahmen dieser Arbeit werden Algorithmen für iterative MIMO-Decodierung entwickelt und optimiert, sowie deren Leistungsfähigkeit und VLSI-Implementationskomplexität analysiert.

Zuerst wird der Detektionsalgorithmus von Wang und Poor, *IEEE Trans. Comm.*, 1999 untersucht und für bessere Effizienz optimiert. Dabei wird eine neue Methode angewendet, welche es ermöglicht die Komplexität des Algorithmus signifikant zu reduzieren ohne die Leistungsfähigkeit zu verringern. Basierend auf den in dieser Arbeit optimierten Algorithmus wurde eine VLSI-Schaltung implementiert, welche sehr hohe Effizienz erreicht und damit beweist, dass SISO-Detektion für iterative MIMO-Decodierung tatsächlich in die Praxis umgesetzt werden kann.

Als zweiten Beitrag dieser Arbeit präsentieren wir einen neuen SISO-Detektionsalgorithmus für MIMO-Systeme, welcher auf dem Prinzip von Sphere-Decoding (SD)—entwickelt von Pohst, *ACM SIGSAM*, 1981—aufbaut. Dieser Algorithmus benutzt das STS (single tree-search) Verfahren und bezieht das Limitieren von Zuverlässigkeitsinformation in die Baumsuche mit ein. Diese Technik führt zu einer massiven Komplexitätsreduktion und ermöglicht einen umfassenden Abtausch zwischen Leistungsfähigkeit und Komplexität. Ausserdem zeigt der resultierende Algorithmus bessere Leistungsfähigkeit und geringere Komplexität als bestehende SISO-Detektionsalgorithmen für iterative MIMO-Decodierung. Weiterhin zeigen wir VLSI-Implementationsresultate einer soft-output-Variante vom STS-SD Algorithmus und demonstrieren damit, dass diese Methode optimale Leistungsfähigkeit in praktischen Systemen erreichen kann.

Zuletzt wird der VLSI-Schaltungsaufwand und die Leistungsfähigkeit von verschiedenen (state-of-the-art) SISO-Kanaldecodern analysiert. Zu diesem Zweck wurden dedizierte VLSI-Implementationen für die SISO-Decodierung von Faltungscodes, LDPC (low-density parity check)-Codes, sowie Turbocodes entwickelt, welche einen hohen Durchsatz erreichen. Die daraus resultierenden Implementationsresultate zeigen, dass effiziente SISO-Decodierung für alle drei Codierungsverfahren in der Praxis möglich ist.

Basierend auf den Resultaten, die in dieser Arbeit erhalten wurden, zeigen wir, dass iterative MIMO-Decodierung in praktische Systeme umgesetzt werden kann. Zudem schätzen wir den entsprechenden Flächenverbrauch ab und zeigen, dass die benötigte Schaltungsfläche ungefähr linear mit der Anzahl Iterationen ansteigt, wobei jedoch nur eine sehr geringe Zahl von Iterationen benötig wird, um die optimale Leistungsfähigkeit von drahtlosen MIMO-Kommunikationssystemen näherungsweise zu erreichen.

# Contents

| 1 | Inti | roduction                                   | 1  |

|---|------|---------------------------------------------|----|

|   | 1.1  | MIMO Wireless Technology                    | 2  |

|   |      | 1.1.1 MIMO Gains                            | 2  |

|   |      | 1.1.2 The Role of MIMO Decoding             | 4  |

|   | 1.2  | Contributions of this Work                  | 8  |

|   | 1.3  | Notation                                    | 12 |

|   | 1.4  | Thesis Outline                              | 13 |

| 2 | Iter | ative MIMO Decoding                         | 15 |

|   | 2.1  | System Model                                | 16 |

|   |      | 2.1.1 Transmitter                           | 16 |

|   |      | 2.1.2 MIMO Channel                          | 18 |

|   |      | 2.1.3 Iterative MIMO Decoder                | 19 |

|   | 2.2  | The Basics of MIMO Detection                | 20 |

|   |      | 2.2.1 Hard-Output MIMO Detection            | 20 |

|   |      | 2.2.2 Soft-Input Soft-Output MIMO Detection | 31 |

| 3 | SIS  | O MMSE Parallel Interference Cancellation   | 39 |

|   | 3.1  | Algorithm                                   | 39 |

|   |      | 3.1.1 The SISO MMSE PIC Algorithm           | 40 |

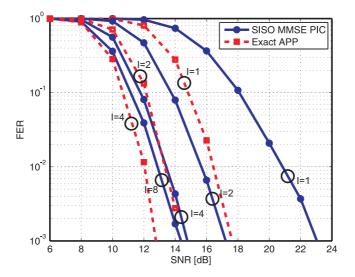

|   |      | 3.1.2 Simulation Results                    | 45 |

|   | 3.2  |                                             | 47 |

|   |      | 3.2.1 Reduction of Algorithmic Complexity   | 48 |

|   |      | 3.2.2 Efficient Matrix Inversion            | 59 |

|   | 3.3  | VLSI Implementation                         | 62 |

|   |      | 3.3.1 VLSI Architecture                     | 62 |

| CONTENTS |  |

|----------|--|

| CONTENTS |  |

|   |      | 3.3.2  | Implementation Results                           | 72  |

|---|------|--------|--------------------------------------------------|-----|

| 4 | Soft | -Input | t Soft-Output Sphere Decoding                    | 77  |

|   | 4.1  | SISO   | Sphere Decoding                                  | 77  |

|   |      | 4.1.1  | The Basics of Sphere Decoding                    | 78  |

|   |      | 4.1.2  | List Sphere Decoding                             | 83  |

|   |      | 4.1.3  | Max-Log LLR Computation as a Tree-Search .       | 87  |

|   |      | 4.1.4  | Tightening of the Tree-Pruning Criterion         | 91  |

|   | 4.2  | Single | Tree-Search Sphere Decoding                      | 95  |

|   |      | 4.2.1  | List Administration                              | 97  |

|   |      | 4.2.2  | Extrinsic LLR Clipping                           | 97  |

|   |      | 4.2.3  | The Tree-Pruning Criterion                       | 98  |

|   | 4.3  | Chann  | nel Matrix Preprocessing                         | 99  |

|   |      | 4.3.1  | Column-Sorting and Regularization of the Chan-   |     |

|   |      |        | nel Matrix                                       | 99  |

|   |      | 4.3.2  | Compensation of Self-Interference                | 101 |

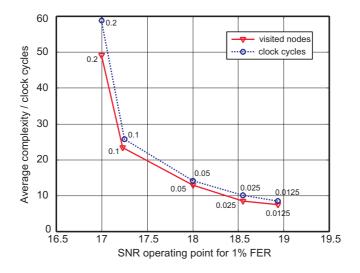

|   | 4.4  | Run-T  | Time Constraints                                 | 104 |

|   |      | 4.4.1  | Issues with SD Complexity                        | 104 |

|   |      | 4.4.2  | Early-Termination and Scheduling                 | 105 |

|   | 4.5  | LLR (  | Correction                                       | 108 |

|   |      | 4.5.1  | The Basic Idea                                   | 108 |

|   |      | 4.5.2  | Computation of LLR Correction Functions          | 110 |

|   |      | 4.5.3  | An Example                                       | 111 |

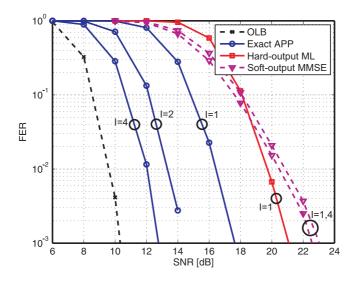

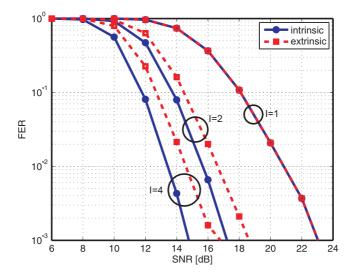

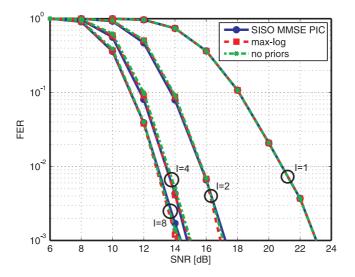

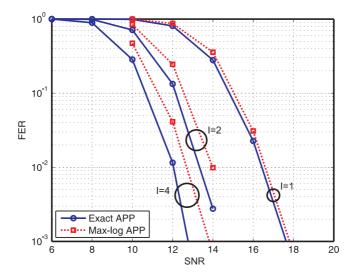

|   | 4.6  |        | ation Results                                    | 112 |

|   |      | 4.6.1  | Impact of the Max-Log Approximation              | 112 |

|   |      | 4.6.2  | Tightening of the Tree-Pruning Criterion         | 113 |

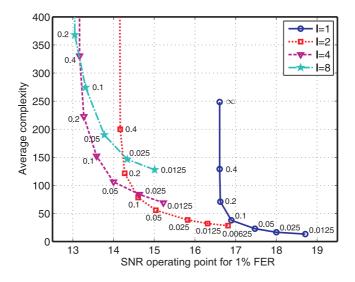

|   |      | 4.6.3  | Performance/Complexity Tradeoffs                 | 115 |

|   |      | 4.6.4  | Comparison with RTS and LSD                      | 117 |

|   |      | 4.6.5  | Impact of LLR Correction                         | 120 |

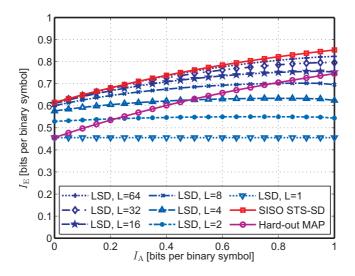

|   |      | 4.6.6  | Information Transfer Characteristics             | 125 |

|   |      | 4.6.7  | Approaching Outage-Capacity with                 |     |

|   |      |        | SISO STS Sphere Decoding                         | 128 |

|   | 4.7  |        | Implementation of Soft-Output Single Tree-Search | 100 |

|   |      | -      | e Decoding                                       | 129 |

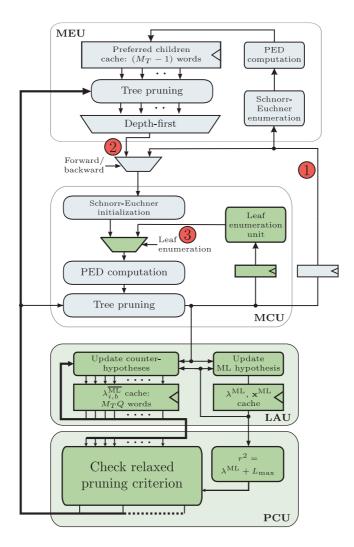

|   |      | 4.7.1  | VLSI Architecture                                | 130 |

|   |      | 4.7.2  | Implementation Results                           | 135 |

| <b>5</b>     | Soft                             | t-Input Soft-Output Channel Decoding           | 141        |

|--------------|----------------------------------|------------------------------------------------|------------|

|              | 5.1                              | Convolutional Codes                            | 142        |

|              |                                  | 5.1.1 The BCJR Algorithm                       | 144        |

|              |                                  | 5.1.2 VLSI Architecture                        | 149        |

|              |                                  | 5.1.3 Implementation Results                   | 153        |

|              | 5.2                              | Low-Density Parity Check Codes                 | 157        |

|              |                                  | 5.2.1 Quasi-Cyclic LDPC Codes and Decoding     | 158        |

|              |                                  | 5.2.2 VLSI Architecture                        | 162        |

|              |                                  | 5.2.3 Implementation Results                   | 169        |

|              | 5.3                              | Turbo Codes                                    | 171        |

|              |                                  | 5.3.1 Decoding of Turbo Codes                  | 173        |

|              |                                  | 5.3.2 VLSI Architecture                        | 178        |

|              |                                  | 5.3.3 Implementation Results                   | 182        |

|              | 5.4                              | Performance/Complexity Tradeoff                |            |

|              |                                  | for SISO Channel Decoding                      | 186        |

|              |                                  | 5.4.1 Performance and Complexity Measures      | 186        |

|              |                                  | 5.4.2 Tradeoff Comparison and Conclusions      | 188        |

| 6            | Performance/Complexity Tradeoffs |                                                |            |

|              | 6.1                              | Performance and Complexity Measures            | 191        |

|              |                                  | 6.1.1 Performance Measure                      | 192        |

|              |                                  | 6.1.2 Throughput and Area Measures             | 192        |

|              |                                  | 6.1.3 Efficiency and Complexity Measures       | 193        |

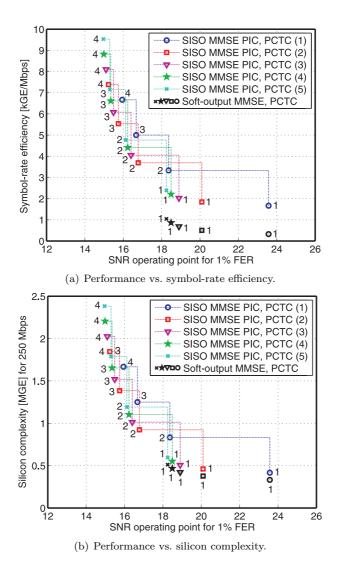

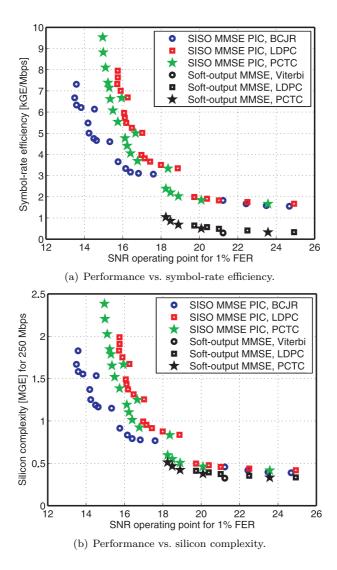

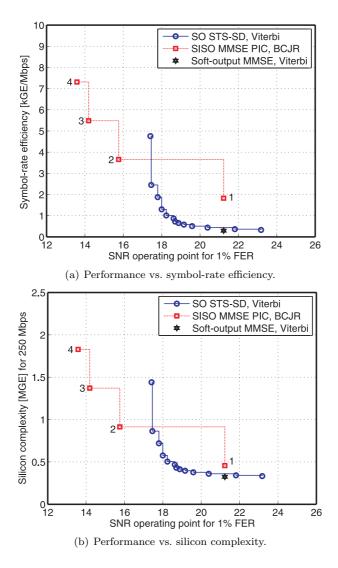

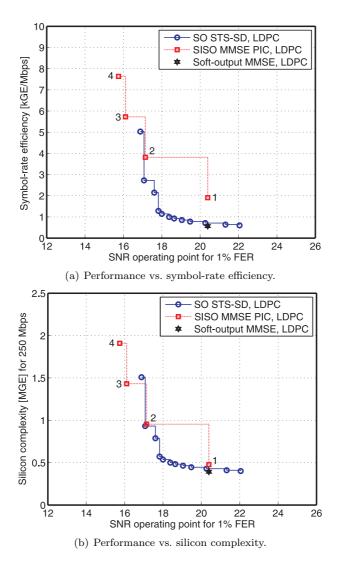

|              | 6.2                              | Performance/Complexity Tradeoffs               | 196        |

|              |                                  | 6.2.1 Impact of Channel Codes to               |            |

|              |                                  | Performance/Complexity Tradeoff                | 197        |

|              |                                  | 6.2.2 SISO MMSE PIC vs. Soft-Output STS-SD     | 204        |

| 7            | Sun                              | nmary, Conclusion, and Outlook                 | <b>211</b> |

|              | 7.1                              | Summary                                        | 211        |

|              | 7.2                              | Conclusion                                     | 216        |

|              | 7.3                              | Outlook                                        | 217        |

| $\mathbf{A}$ | Mat                              | thematical Derivations for SISO MMSE PIC       | 219        |

| _            | A.1                              |                                                | 219        |

|              | A.2                              | Efficient MMSE Filter Computation              | 220        |

|              |                                  | A.2.1 Single Matrix Inversion                  | 220        |

|              |                                  | A.2.2 Further Methods for Complexity Reduction | 223        |

| A.3 Efficient NPI-Variance Computation | 225 |  |

|----------------------------------------|-----|--|

| List of Acronyms, Figures, and Tables  | 227 |  |

| Bibliography                           |     |  |

| Curriculum Vitae                       | 253 |  |

# Chapter 1 Introduction

During the last decade, many wired communication systems are being replaced by corresponding wireless services. With the increasing availability of portable computers and personal digital assistants, for example, wireless services have shifted from voice-based to multimediaoriented applications. Such services often tend to require even higher data rates. The trend towards throughput-intensive applications is summarized by Edholm's Law, which states that data rates of wired and wireless communication systems double every 18 months [1]. Novel technologies, the evolution of wireless communication standards, and corresponding low-cost devices, are key to follow this trend, achieving better quality of service (QoS) and supporting a large amount of users that communicate simultaneously. The recent development of the IEEE 802.11n wireless local area network (WLAN) standard [2], for example, indicates that future wireless systems will be able to support peak data rates in the range of several hundred megabits up to gigabits per second, while offering the same reliability and data rates as their corresponding wired counterparts.

Simply allocating more bandwidth or increasing the transmit power are *not* viable solutions to keep up with the growing demand for higher data rates and a large number of users, while meeting stringent QoS requirements (such as link reliability, coverage, and range). As bandwidth has become an extremely scarce (and hence expensive) resource, simply increasing the bandwidth is neither feasible nor economic. Increasing the transmit power is not practicable as well, since the maximum transmit power is regulated in most of the available frequency bands, e.g., in order to prevent health hazards. In addition, a high transmit power would significantly reduce the battery lifetime of portable devices and cause interference to other users communicating nearby, which reduces the potential of re-using of frequency bands.

In order to meet the contradictory requirements for higher data rates, better QoS, and a large number of users, while maintaining the transmit power and bandwidth, novel technologies need to be considered. Multiple-input multiple-output (MIMO) wireless communication is believed to be the key technology to meet these demands, because it improves both, the data rate for a given bandwidth (which is also known as spectral efficiency) and the QoS of wireless communication systems.

# 1.1 MIMO Wireless Technology

Wireless channels suffer from signal fading, caused by destructive interference of multi-path propagation, and from interference caused by other services sharing the same frequency band. The use of multiple antennas at the transmitter and/or the receiver enables significant improvements in terms of link reliability, range, and spectral efficiency compared to that of single-antenna systems. However, fully exploiting these gains comes, in general, at the cost of significantly increased signal-processing complexity, especially in the receiver.<sup>1</sup>

## 1.1.1 MIMO Gains

Employing multiple antennas only at the transmitter or the receiver, is known as multiple-input single-output (MISO) and single-input multiple-output (SIMO), respectively. Communication with multiple antennas at *both* sides of the wireless link is known as multiple-input multiple-output (MIMO) technology. The gains enabled by multiantenna technologies can be categorized as follows (see, e.g., [3–5]).

$<sup>^1\</sup>rm Note that it is not always feasible to obtain all gains at once. The performance improvements of multi-antenna technology rather depends on the underlying signaling schemes.$

**Diversity Gain** The main idea underlying diversity corresponds to transmitting the same signal over independently fading links (also known as diversity branches). Since not all links fade concurrently with high probability, combining all versions of the transmit signal in the receiver mitigates fading effects. Note that the concept of diversity is strongly related to link reliability: For a higher number of independently fading diversity branches, fading becomes less likely.

There are three main sources of diversity that can be exploited in single-user wireless systems: i) temporal diversity, which is caused by the delay spread of the signal, ii) frequency diversity, which is caused by the Doppler spread, and iii) spatial diversity (also known as antenna diversity). While single-antenna systems offer temporal and frequency diversity (i.e., signals can be transmitted at different time instances or over different frequencies), multiple antennas at the transmitter and/or the receiver enables spatial diversity, i.e., the signal can be transmitted over different paths in space. This technique has become popular in wireless communication systems since it improves link reliability—in contrast to time or frequency diversity—without reducing the data rate or increasing the bandwidth. In MIMO systems, the maximum amount of spatial diversity corresponds to the number of transmit antennas times the number of receive antennas (if all paths fade independently). Thus, MIMO technology is able to significantly reduce fading effects and it offers to improve the QoS of wireless communication systems.

For portable low-complexity and battery-powered wireless devices it is often not feasible to employ multiple antennas, due to stringent space and power limitations. For such systems, multiple antennas are often employed only at the base-station (where power consumption and space is not an issue) and space-time coding is employed; this technique enables to obtain transmit diversity and it, therefore, improves link reliability without the need for channel-state information at the transmitter. In particular, space-time block codes (STBCs) [6,7], such as the Alamouti scheme [8], have emerged as promising means to offer transmit diversity in practical systems.

**Array Gain** refers to an increase in average receive signal-to-noise ratio (SNR) by the coherent combination (i.e., by alignment of the

phases using channel knowledge at the receiver) of all signals picked up at multiple receive antennas.<sup>2</sup> The increase in terms of average SNR grows proportionally to the number of receive antennas; simply speaking: "more receive antennas pick up more signal energy." Hence, array gain as well improves the QoS of wireless communication systems.

Multiplexing Gain Array gain and spatial diversity can be obtained through multiple antennas at the transmitter or at the receiver. Employing multiple antennas at *both ends* of the wireless link (i.e., MIMO technology) permits the concurrent transmission of multiple data streams within the same frequency band. This technique is known as spatial multiplexing (SM) and it is able to yield a linear increase (in the minimum number of transmit or receive antennas) in terms of system capacity [9]. It is important to note that the SM gain improves the spectral efficiency and comes at no expense of increased transmit power. Since no additional transmit power is necessary, the potential for bandwidth re-using by users communicating nearby is improved as well. Hence, SM is key to achieve high data rates, which is the main reason for the adoption of this technology by many modern wireless communication standards, such as IEEE 802.11n [2], IEEE 802.16e [10], and the third-generation partnership project (3GPP) consortium long-term evolution (LTE) standard [11].

## 1.1.2 The Role of MIMO Decoding

The physical layer of a receiver for MIMO wireless systems consist of several parts, such as radio frequency (RF) components, synchronization circuitry, channel estimation, and the MIMO decoder. The MIMO decoder consists of a MIMO detector to separate the spatially multiplexed data streams and a channel decoder, which computes estimates of the transmitted information bits. The performance of MIMO systems is heavily affected by the performance of the MIMO decoder. In order to fully exploit the gains offered by MIMO technology, it

$<sup>^{2}</sup>$ Note that the array gain can also be obtained by employing multiple antennas at the transmitter, which requires transmit-side channel knowledge.

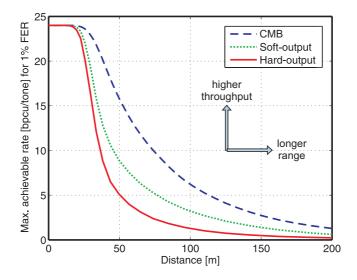

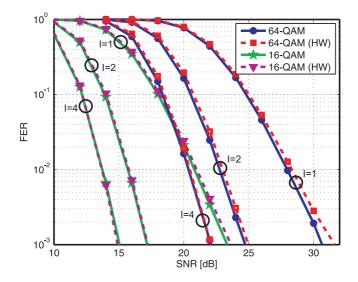

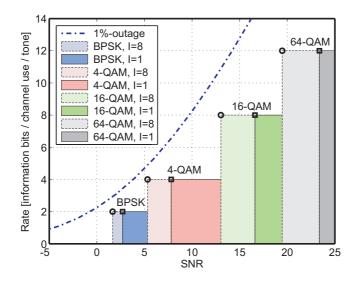

Figure 1.1: Distance (between transmitter and receiver) versus maximum achievable rates for 64-QAM data transmission in a 4-stream MIMO-OFDM system.

is essential to employ high-performance MIMO decoding algorithms. However, such algorithms often entail an extremely high amount of signal processing complexity. The tradeoff between performance and complexity inherently present in MIMO decoding is briefly illustrated below.

## Performance/Complexity Tradeoff

**Performance** Figure 1.1 shows maximum achievable rates at a given distance (between transmitter and receiver) for two different MIMO detection algorithms (i.e., optimum hard-output detection and max-log optimal soft-output detection) as well as the theoretical limit of the considered system, referred to as coded-modulation bound (CMB).<sup>3</sup> We can see that hard-output MIMO detection re-

<sup>&</sup>lt;sup>3</sup>This simulation shows the maximum achievable rate in bits per channel use (bpcu) per OFDM tone for a target frame error-rate (FER) of 1%. We consider an

sults in worse performance (in terms of achievable rates and range) than soft-output MIMO detection. It is important to note that soft-output MIMO detection requires, in general, more sophisticated (and hence, more complex) algorithms compared to hard-output MIMO detection (see Section 2.2). Hence, more sophisticated MIMO detection schemes allow an increased achievable rate at a given distance to the transmitter, or an increased range (i.e., the maximum distance where a given target rate is supported). We emphasize that there is still a substantial gap between soft-output MIMO detection and the theoretical performance limit. Hence, employing even more sophisticated MIMO detection schemes might further approach the CMB.

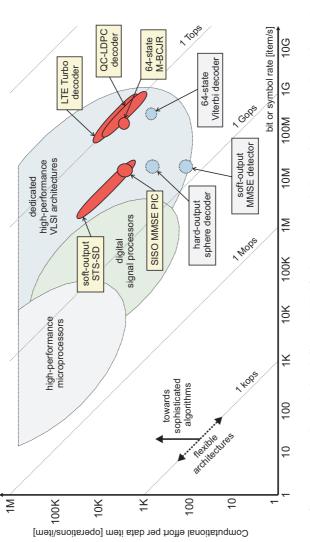

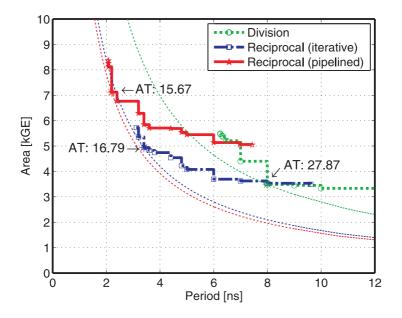

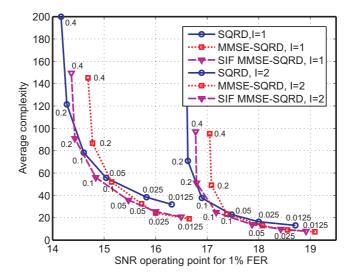

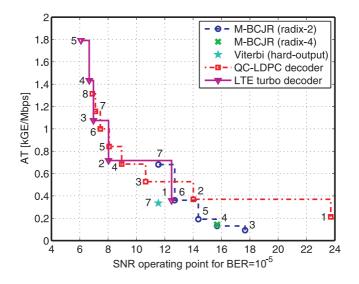

**Complexity** Figure 1.2 illustrates the computational complexity associated with various algorithms employed in MIMO decoders.<sup>4</sup> The algorithms and implementations provided in this thesis have been highlighted in this figure; they are able to approach the theoretical optimum (i.e., the CMB). We can see that more sophisticated algorithms (such as soft-output sphere decoding or SISO MMSE PIC) require higher computational complexity compared to that of low-complexity algorithms for MIMO decoding (e.g., soft-output MMSE detection or hard-output MIMO detection using the sphere decoder). Hence, we conclude that employing MIMO decoding schemes that are able to approach the theoretical performance limit, entail—as it

<sup>4</sup>Figure 1.2 has been adapted from [14, Fig. 2.2] and [15, Fig. 1.1] using results of [16]. The algorithms and implementation results described in this thesis have been highlighted. The computational complexity is in operations per second (ops).

IEEE 802.11n-like [2] MIMO-OFDM system, with four transmit and four receive antennas, 64 OFDM tones, 64-QAM modulation with Gray mapping. The distance is measured in meters and has been computed from the average receive SNR according to the TGn type C path-loss model (for 20 MHz bandwidth and 2.4 GHz carrier frequency) [12]. We consider an implementation loss of 4 dB SNR to obtain more realistic results, i.e., the average receive SNR has been reduced by 4 dB. The curves associated with "hard-output" and "soft-output" correspond to that of hard-output maximum-likelihood (ML) detection and max-log-optimal soft-output a posteriori probability (APP) performance, respectively. The corresponding rates are obtained through Monte-Carlo simulations of the mutual information between the transmitted bits and the log-likelihood ratios or the hard-outputs computed by the MIMO detectors. The curve associated with the CMB refers to the maximum achievable rate when using 64-QAM modulation (see [13]), i.e., corresponds to an upper bound on the system performance.

will be shown in the remainder of this thesis—an (often significant) increase in computational complexity.

Furthermore, we can see from Figure 1.2 that the algorithms considered in this thesis require dedicated high-performance very-largescale integration (VLSI) architectures to meet the computational requirements. As it was shown in [15], MIMO decoding contributes substantially to the VLSI implementation complexity of the total receiver and strongly affects the corresponding costs. The ultimate MIMO receiver must, therefore, achieve best decoding performance at lowest possible VLSI implementation complexity. This goal can only be achieved by jointly considering algorithm and VLSI implementation aspects and by performing careful investigations of the underlying performance/complexity tradeoffs.

### The State-of-the-Art in MIMO Decoding

Almost all recent MIMO receiver designs that can be found in the open literature employ linear MIMO detection schemes, see e.g., [16–18]. Note that linear detection offers acceptable error-rate performance while requiring low computational complexity (cf. Figure 1.2). Hence, most of the currently available implementations lie on the low-complexity low-performance end of the performance/complexity tradeoff.

On the algorithmic side, state-of-the-art MIMO decoders employ non-linear MIMO detection schemes based on sphere decoding (SD). Moreover, such decoders often perform iterative MIMO detection and channel decoding, which is known as *iterative MIMO decoding* in the literature [19]. This approach is believed to be a key technology to achieve near-optimum performance in MIMO wireless systems. However, the associated computational complexity is significant and —up to now— not much is known about the performance and complexity of corresponding VLSI implementations.

# 1.2 Contributions of this Work

The goal of this thesis is to design and optimize algorithms for iterative MIMO decoding and to investigate the associated performance and VLSI implementation aspects. To this end, we analyze and improve soft-input soft-output MIMO detection algorithms for iterative MIMO decoding and present novel low-complexity solutions. In addition, we describe corresponding VLSI architectures and provide reference application-specific integrated circuit (ASIC) implementation results. Moreover, we compare the performance and VLSI implementation complexity associated with SISO channel decoding. Finally, all results obtained throughout this work allow for a detailed analysis of the performance/complexity tradeoffs associated with iterative MIMO decoding. Based on this analysis, we describe best-practices for hardware-efficient iterative MIMO decoding.

In summary, this thesis provides novel high-performance and lowcomplexity solutions for iterative MIMO decoding and an analysis of the associated performance/complexity trade-offs. To the best of the authors knowledge, all presented VLSI implementations are currently ranked among the best performing. The contributions of this thesis are detailed in the following.

#### SISO MMSE Parallel Interference Cancellation

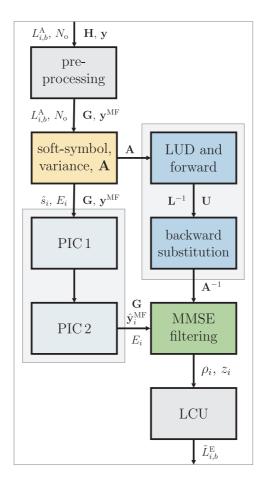

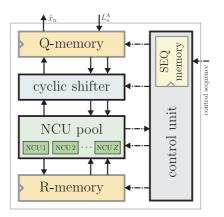

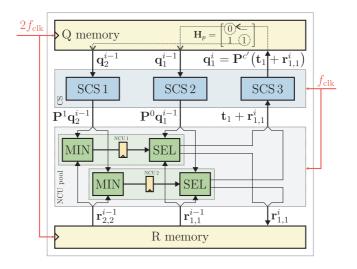

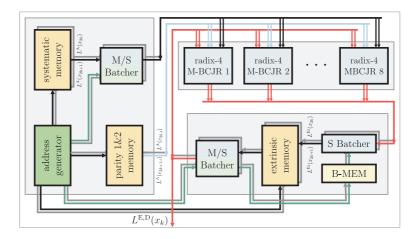

In Chapter 3, we describe the first VLSI implementation of a softinput soft-output (SISO) detector for iterative MIMO decoding. The algorithm underlying our VLSI implementation is known as SISO minimum mean-square error (MMSE) parallel interference cancellation (PIC) and was invented by Wang and Poor [20] for iterative detection in multi-user code division multiple access (CDMA) systems.

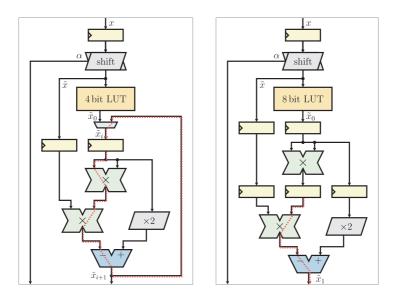

The algorithm in its original form exhibits prohibitive computational complexity due to the requirement of *multiple* matrix inversions at symbol-rate. For economic hardware implementation, we describe a novel method which requires only one matrix inversion at symbolrate, without affecting the algorithm's performance. The (remaining) matrix inversion task is performed by a novel high-performance architecture based on the LU-decomposition. In addition, a variety of tricks on algorithmic and architectural level have been employed in order to attain a low-complexity and high-performance VLSI architecture of the optimized SISO MMSE PIC algorithm.

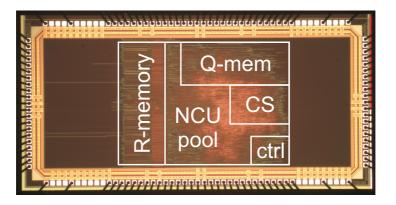

The resulting architecture has been integrated in 90 nm CMOS technology. The ASIC implementation results demonstrate that SISO

detection based on the proposed SISO MMSE PIC algorithm enables high-throughput soft-input soft-output MIMO detection in practice.

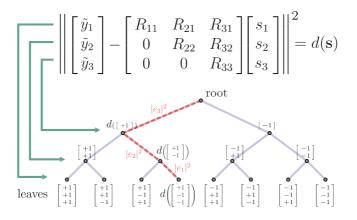

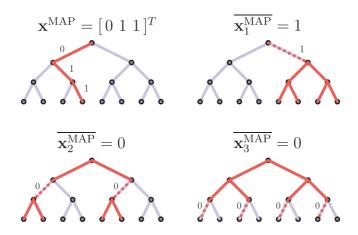

## SISO Single Tree-Search Sphere Decoding

Chapter 4 summarizes and extends our results in [21–27]. We describe a SISO single tree-search (STS) sphere decoding (SD) algorithm that is tunable between max-log optimal SISO and hard-output maximum a posteriori (MAP) detection performance. We develop a max-log optimal a priori information processing method, which significantly reduces the tree-search complexity compared to [28–32] and avoids the computation of transcendental functions. The basic idea for complexity reduction and tunability of the algorithm is to incorporate clipping of the extrinsic log-likelihood ratios (LLRs) into the tree search.

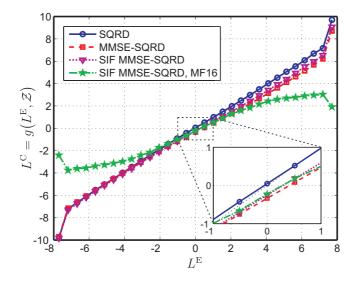

We furthermore propose a method for self-interference compensation in the LLRs —caused by channel-matrix regularization — directly in the tree search. Due to prohibitively high worst-case complexity of SD, we propose early termination based on a novel scheduling technique, which is well-suited for implementation in practical systems, while only slightly degrading the algorithm's performance. In addition, we describe a new method to correct approximate LLRs from sub-optimal detectors, which (often significantly) improves detection performance at low additional computational complexity. Simulation results show that the resulting SISO STS-SD algorithm operates close to outage capacity at remarkably low computational complexity. In addition, the proposed algorithm clearly outperforms state-of-the-art SISO detection schemes for iterative MIMO systems.

We describe the first VLSI implementation of the soft-output (SO) STS-SD algorithm, based on the one-node-per-cycle VLSI implementation for hard-output Schnorr-Euchner SD developed in [33]. Corresponding VLSI implementation results demonstrate that the proposed algorithm is suitable for low-complexity and high-performance MIMO detection in practical systems.

## Soft-Input Soft-Output Channel Decoding

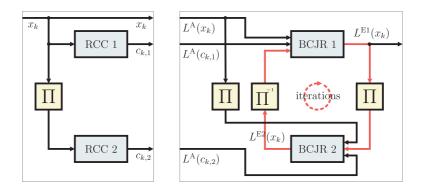

In Chapter 5, we describe three different high-throughput channel decoder implementations for SISO decoding of convolutional codes

(CCs), low-density parity check (LDPC) codes, and turbo codes:

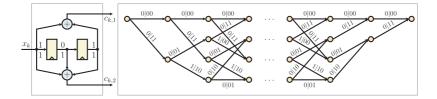

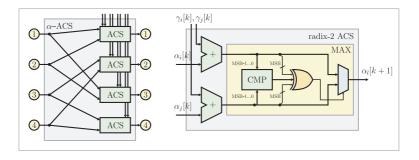

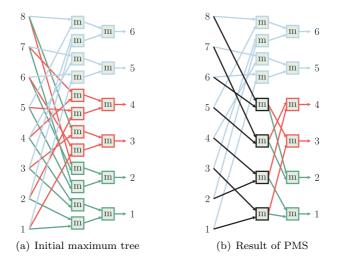

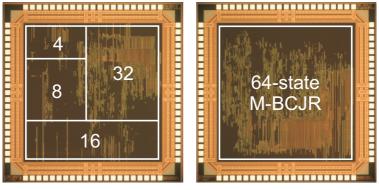

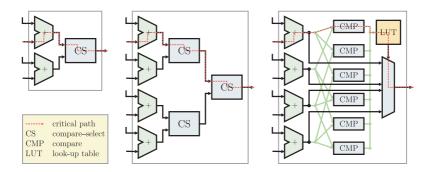

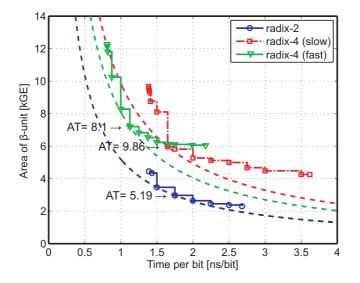

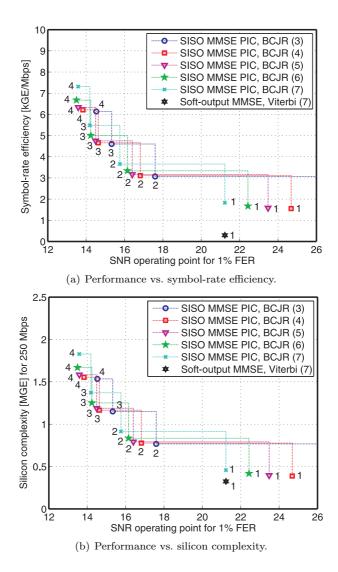

- For SISO decoding of CCs, we design a high-throughput architecture for the M-BCJR algorithm [34] and we derive corresponding VLSI implementations that support different constraint lengths (ranging from three to seven). Hardware-level optimizations yield significant improvements in circuit area and decoding throughput. The resulting M-BCJR architectures have been implemented in 180 nm CMOS technology. For constraint length seven, the architecture is compliant with IEEE 802.11n [2] and is the first of its kind described in the open literature.

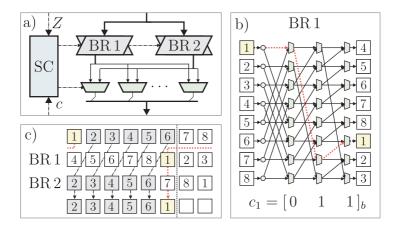

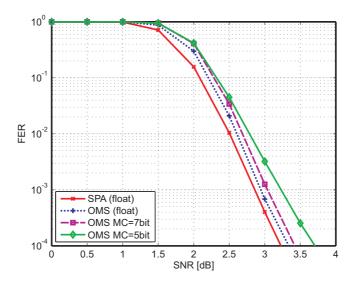

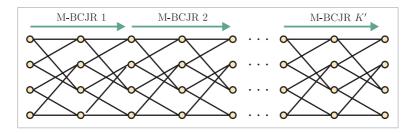

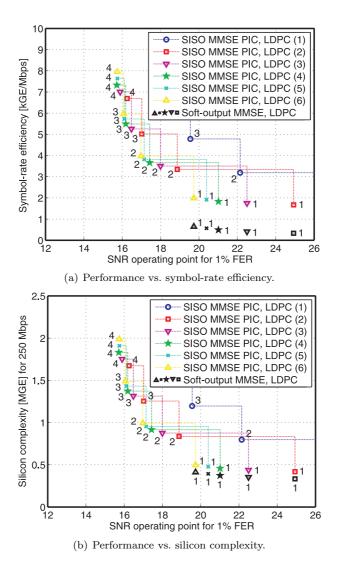

- For SISO decoding of LDPC codes, we summarize our results presented in [35]. We develop a high-throughput architecture that is able to decode quasi-cyclic (QC) LDPC codes. The design of a novel permutation network and a new method to combine control signals with the information contained in the parity-check matrix enable re-configurability of the decoder (at run-time) for virtually all QC-LDPC codes that fit into the allocated memories. Corresponding VLSI implementation results in 180 nm CMOS technology demonstrate that the performance, energy-efficiency, and area are comparable to that of dedicated (i.e., non re-configurable) architectures. The resulting decoder implementation is compliant with the IEEE 802.11n standard.

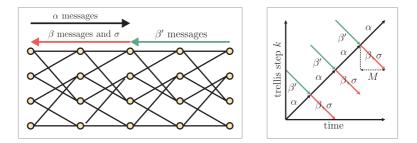

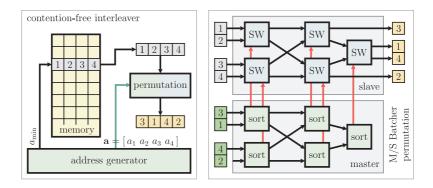

- We describe a turbo decoder for the 3GPP LTE standard [11]. Our architecture has been optimized for high throughput by using an optimized radix-4 M-BCJR architecture in combination with a novel interleaver architecture. Corresponding VLSI implementation results in 130 nm CMOS technology show that the achieved throughput is 15 to 25 times higher than that of reference implementations, e.g., [36, 37], while being more efficient in terms of area per throughput.

Finally, we compare the three SISO decoders in terms of VLSI implementation complexity and error-rate performance and analyze the underlying tradeoffs.

## Performance/Complexity Tradeoff Investigation

Chapter 6 compares the VLSI implementation complexity of iterative MIMO decoding (i.e., of soft-input soft-output MIMO detection and SISO channel decoding) with the associated (error-rate) performance. The performance/complexity evaluation is based on a method called throughput matching, which simplifies the tradeoff analysis and enables to provide an estimate of the silicon complexity required for an iterative MIMO decoder.

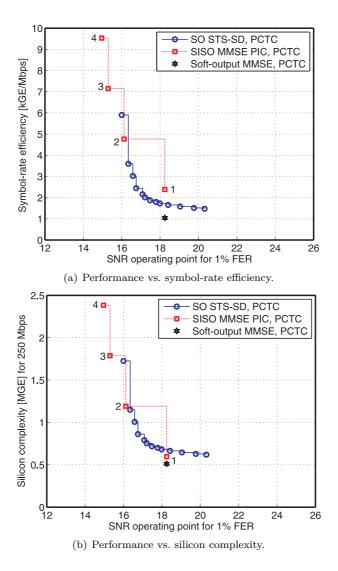

We compare the performance/complexity tradeoffs of linear MIMO detection and SISO MMSE PIC using CCs, LDPC codes, and turbo codes. Moreover, we compare the performance/complexity tradeoff realized by the SISO MMSE PIC to that of the SO STS-SD implementation. Finally, we propose guidelines for the design of hardware-efficient high-performance MIMO decoders.

# 1.3 Notation

Matrices are set in **boldface** capital letters, vectors in **boldface** lowercase letters. The superscripts  $\overline{T}$ , H, and \* stand for transpose, conjugate transpose, and (element-wise) complex conjugation, respectively. We write  $A_{i,j}$  for the entry in the *i*th row and *j*th column of the matrix **A** and  $b_i$  for the *i*th entry of the vector  $\mathbf{b} = [b_1 \cdots b_N]^T$ .  $\mathbf{I}_N$  and  $\mathbf{0}_{M \times N}$  denote the  $N \times N$  identity matrix, and the  $M \times N$ dimensional all-zero matrix, respectively.  $\mathbf{1}_M$  is the all-ones vector of dimension M. Slightly abusing common terminology, we call an  $N \times M$  matrix **A**, where N > M, satisfying  $\mathbf{A}^{H}\mathbf{A} = \mathbf{I}_{M}$ , unitary. The  $\ell^2$ -norm of a vector **b** is denoted by  $\|\mathbf{b}\|$ . The probability of an event  $\mathcal{Z}$  is denoted by  $P[\mathcal{Z}]$ , the probability density function (PDF) of a continuous random variable (RV) z is denoted by p(z).  $\mathbb{E}[Z]$  and Var[Z] stand for the expectation and variance of the RV Z, respectively. The real and imaginary part of  $x \in \mathbb{C}$  is denoted by  $\Re\{x\}$ and  $\Im\{x\}$ , respectively. The binary complement of  $x \in \{+1, -1\}$  is  $\overline{x} = -x$ . The round, ceil, floor, and signum operations of  $x \in \mathbb{R}$  are denoted by  $[x \mid x]$ , |x|, and sign(x), respectively.  $\mathbb{CZ}$  stands for the set of Gaussian integers, i.e.,  $\mathbb{CZ} = \mathbb{Z} + \sqrt{-1}\mathbb{Z}$ , and  $|\mathcal{O}|$  designates the cardinality of the set  $\mathcal{O}$ .

# 1.4 Thesis Outline

The remainder of this thesis is organized as follows. Chapter 2 describes the system model, introduces iterative MIMO decoding, and briefly reviews the basics of hard-output and (soft-input) soft-output MIMO detection. We conclude this chapter by a performance comparison of the reference detector with some of the most prominent sub-optimal low-complexity MIMO detection schemes. In Chapter 3, a SISO detection algorithm for iterative MIMO decoding is optimized for VLSI implementation. Finally, we show corresponding ASIC implementation results of the first SISO detector for iterative MIMO decoding reported in the literature. A novel high-performance lowcomplexity SISO detection algorithm based on SD is described in Chapter 4. A variety of techniques are employed to further reduce its computational complexity. Finally, we propose reference VLSI implementation results of a soft-output variant of the proposed algorithm. Chapter 5 describes VLSI implementations for SISO decoding of convolutional, LDPC, and turbo codes. A detailed tradeoff comparison in terms of performance and complexity concludes this chapter. In Chapter 6, we provide—based on implementation results provided in the previous three chapters—performance/complexity tradeoff results for iterative MIMO decoding (including the MIMO detector and the channel decoder). We conclude in Chapter 7 and outline open research topics.

# Chapter 2

# Iterative MIMO Decoding

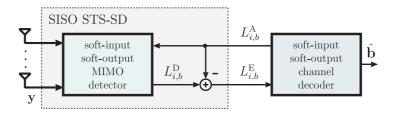

Optimum detection performance in coded MIMO systems in terms of minimizing the error-rate performance, is obtained by joint detection and decoding (JDD). The computational complexity associated with JDD is, in general, prohibitively high, even for short code-blocks (see [38]). *Iterative MIMO decoding* is believed to be the most promising approach for low-complexity and near-optimum data detection in coded MIMO systems. The main idea underlying iterative detection and decoding is the assumed *independence* of MIMO detection and channel decoding. This assumption enables to solve both tasks *separately*, which entails, in general, significantly less computational complexity compared to that of JDD. Since MIMO detection and channel decoding have been separated, reliability information on the coded bits is exchanged between the two components in an iterative fashion. When the iteration process is stopped, the channel decoder produces estimates of the transmitted bits.

Iterative decoding reaches back to 1963, when Gallager proposed an iterative decoding method for LDPC codes in his visionary Ph.D. thesis [39]. Three decades later, iterative decoding has been rediscovered by Berrou *et al.* for decoding of turbo codes [40]. The exceptional performance achieved by iterative decoding of turbo codes, and the additional generalization of iterative decoding of virtually any linear block-code by Hagenauer *et al.* in 1996 [41], sparked tremendous research activities. In 1999, the concept of iterative detection and decoding has been developed by Wang and Poor for data detection in multi-user (MU) CDMA systems [20]. In 2002, the idea has been adapted for detection in inter-symbol interference (ISI) channels by Tüchler *et al.* [42]. In the same year, iterative MIMO decoding has been proposed for MIMO wireless communication systems by Witzke *et al.* [43]. In 2003, Hochwald and ten Brink demonstrated that iterative MIMO decoding is able to achieve near channel-capacity when using a SD-based soft-input soft-output MIMO detection algorithm in combination with turbo codes [19].

In the remainder of this chapter, we introduce the system model and describe the concept of iterative MIMO decoding (Section 2.1). We outline some of the most relevant hard-output and soft-output MIMO detection algorithms in Section 2.2 and conclude with corresponding simulation results that demonstrate the potential of iterative MIMO decoding.

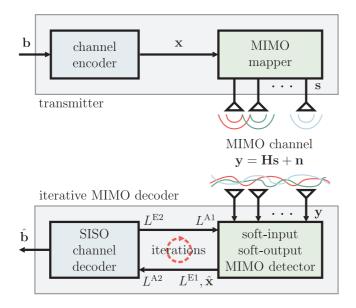

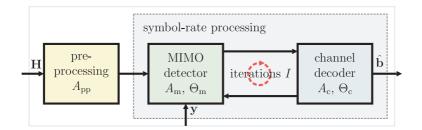

# 2.1 System Model

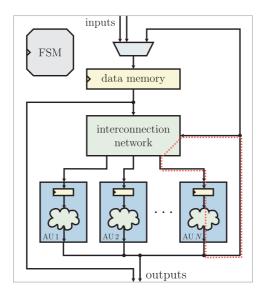

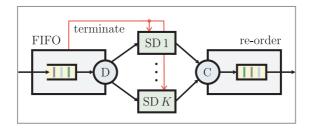

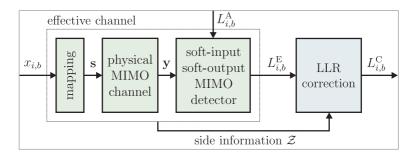

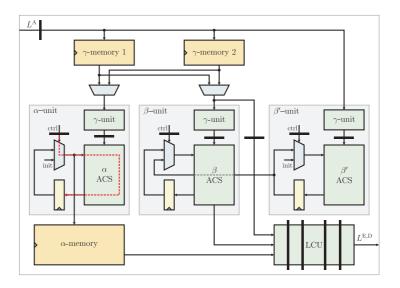

Consider an iterative MIMO system with  $M_{\rm T}$  transmit and  $M_{\rm R}$  receive antennas. In the remainder of this thesis, we assume  $M_{\rm R} \ge M_{\rm T}$ . The MIMO system is depicted in Figure 2.1 and consists of three main components: i) the transmitter, ii) the MIMO channel, and iii) the iterative MIMO decoder; all components are described in the following.

## 2.1.1 Transmitter

The MIMO transmitter obtains a sequence of information bits, denoted by the *B*-dimensional binary-valued vector **b**. This vector is referred to as data frame in the remainder of this thesis. In order to enable reliable transmission, bit-interleaved coded modulation (BICM) is performed [44, 45]. To this end, the channel encoder introduces redundancy in the data frame and performs interleaving of the coded bits. The resulting coded and interleaved bit-stream is denoted by the

Figure 2.1: MIMO wireless communication system employing BICM, spatial multiplexing (SM), and iterative MIMO decoding [19].

binary-valued vector **x** of dimension B/R, where  $0 < R \le 1$  denotes the rate of the employed channel code.<sup>1</sup>

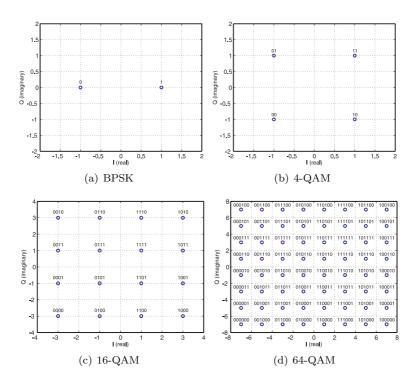

The coded bit-stream is mapped to a sequence of  $M_{\rm T}$ -dimensional symbol vectors  $\mathbf{s}[k] \in \mathcal{O}^{M_{\rm T}}$ , where  $\mathcal{O}$  denotes the underlying complex scalar constellation set with  $|\mathcal{O}| = 2^Q$  and  $k = 1, \ldots, N$ . The index kcorresponds to the kth transmitted symbol vector.<sup>2</sup> Each symbol vector  $\mathbf{s}[k]$  is associated with  $M_{\rm T}Q$  bits, denoted by  $x_{i,b}[k]$  (for i = $1, \ldots, M_{\rm T}$  and  $b = 1, \ldots, Q$ ); the indices i and b refer to the bth bit in the binary label of the ith entry of the symbol vector  $\mathbf{s}[k]$ . The bits are chosen from the set  $\{+1, -1\}$  where the null element (0 in binary logic) of GF(2) corresponds to +1. The bijective mapping between bits  $x_{i,b}[k]$  ( $\forall i, b$ ) and entries of the symbol vector  $\mathbf{s}[k] =$

<sup>&</sup>lt;sup>1</sup>Zero-padding is employed if B is not an integer multiple of 1/R.

<sup>&</sup>lt;sup>2</sup>In orthogonal frequency division multiplexing (OFDM) systems, k stands for the kth OFDM tone and N denotes the maximum number of used tones.

$$[s_1[k] \cdots s_{M_T}[k]]^T$$

is

$s_i[k] = \max(x_{i,b}[k], b = 1, \dots, Q).$  (2.1)

The inverse mapping of (2.1) is denoted by  $[s_i[k]]_b = x_{i,b}[k]$ . The total number of transmitted information bits per data frame corresponds to  $B = RNM_TQ$  bit.

## 2.1.2 MIMO Channel

The symbol vectors  $\mathbf{s}[k]$  ( $\forall k$ ) are transmitted over N MIMO channels. The complex baseband input-output relation of the (frequency-flat) MIMO channel is given by<sup>3</sup>

$$\mathbf{y}[k] = \mathbf{H}[k]\mathbf{s}[k] + \mathbf{n}[k] \tag{2.2}$$

where  $\mathbf{H}[k]$  stands for the kth complex-valued  $M_{\mathrm{R}} \times M_{\mathrm{T}}$  channel matrix,  $\mathbf{y}[k]$  denotes the  $M_{\mathrm{R}}$ -dimensional received signal vector, and  $\mathbf{n}[k]$  is an i.i.d. circularly symmetric complex Gaussian distributed  $M_{\mathrm{R}}$ -dimensional noise vector with variance  $N_{\mathrm{o}}$  per complex entry, i.e.,  $\mathbf{n}[k] \sim \mathcal{CN}(0, N_{\mathrm{o}}\mathbf{I}_{M_{\mathrm{R}}}), \forall k$ . The element  $H_{i,j}[k]$  of the MIMO channel matrix represents the complex-valued transfer function from the *j*th transmit to the *i*th receive antenna. Different transmit powers on the individual transmit antennas are assumed to be absorbed in the channel matrices  $\mathbf{H}[k]$ , which—including the corresponding scaling factors— will be referred to as the physical MIMO channels. In the remainder of this thesis we assume that the transmitter has no channel state information, i.e., the  $\mathbf{H}[k]$  ( $\forall k$ ) and  $N_{\mathrm{o}}$  are perfectly known to the receiver.<sup>4</sup>

The elements of the N channel matrices are usually assumed to be i.i.d. (across space and index k) circularly symmetric complex Gaussian distributed with unit variance (e.g., [9]). This assumption is,

$<sup>^{3}</sup>$ Note that the input-output relation given in (2.2) does not only model MIMO wireless communication using SM, but it can also represent MIMO channels including linear STBCs (e.g., [46]), or other communication channels, such as ISI channels.

<sup>&</sup>lt;sup>4</sup>Pilot symbols are employed in practice to estimate the channel state in the receiver. However, perfect channel state information is not possible, since the so obtained estimates are disturbed by noise [47].

however, optimistic, since real-world wireless channels usually exhibit correlation across space, time, or frequency. To this end, the IEEE 802.11 task group N (TGn) specified typical channel models for WLAN applications [12]. These models enable to obtain simulation results that are more relevant in practice. Unless specified otherwise, the TGn type C channel model—corresponding to a typical residential or small office environment with 30 ns root mean square (RMS) delay spread [12]—is used throughout this thesis.

Transmit symbols are normalized such that  $\mathbb{E}\left[|s_i|^2\right] = E_s (\forall i)$ and the SNR definition used in this thesis refers to the average SNR per receive antenna defined as  $\mathsf{SNR} = M_{\mathrm{T}}E_s/N_{\mathrm{o}}$ . For the sake of simplicity of exposition, the symbol-vector index k is omitted in the remainder of this thesis.

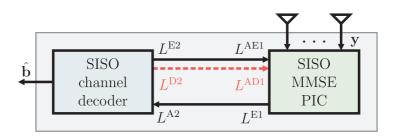

### 2.1.3 Iterative MIMO Decoder

The structure of an iterative MIMO decoder is depicted in Figure 2.1 and consists of a SISO detector for MIMO systems and a SISO channel decoder. The detector and the decoder iteratively exchange reliability information for each coded bit. The iterative detection process is stopped if a maximum number of iterations is reached. Then, the SISO channel decoder produces (binary-valued) estimates of the data bits  $\hat{\mathbf{b}}$ .

### Soft-Input Soft-Output MIMO Detector

The task of the soft-input soft-output MIMO detector is to undo the MIMO mapping and the influence of the MIMO channel, which is accomplished on the basis of the received vector  $\mathbf{y}$ , the channel state information (i.e.,  $\mathbf{H}$  and  $N_{\rm o}$ ), and soft-inputs (i.e., a priori reliability information) in the form of LLRs, denoted by  $L^{\rm A1}$  (see Figure 2.1). The MIMO detector either produces hard decisions for each transmitted bit  $\hat{x}_{i,b}$  ( $\forall i, b$ ) or it computes corresponding a posteriori softoutputs in the form of extrinsic LLRs, denoted by  $L_{i,b}^{\rm E1}$ . The vector containing all a posteriori extrinsic LLR values is denoted by  $L^{\rm E1}$  (see Figure 2.1).

MIMO detectors that compute soft-outputs on the basis of soft-

inputs are referred to as soft-input soft-output (SISO) detectors for MIMO systems. Detectors that compute hard-output estimates (possibly based on a priori information) are referred to as hard-output MIMO detectors. The most prominent hard-output and SISO detection schemes are outlined in Section 2.2.

### Soft-Input Soft-Output Channel Decoder

In iterative MIMO decoding, the SISO channel decoder serves two purposes: i) it computes new a posteriori soft-outputs (in the form of extrinsic LLRs), denoted by  $L^{E2}$ , on the basis of the a priori LLRs  $L^{A2}$  delivered by the MIMO detector (see Figure 2.1) and ii) the SISO channel decoder computes hard-output estimates of the transmitted information bits  $\hat{\mathbf{b}}$  at the end of the iteration process.<sup>5</sup> It is important to note that the a posteriori LLRs of the channel decoder  $L^{E2}$  will get a priori LLRs  $L^{A1}$  of the MIMO detector (i.e.,  $L^{E2} = L^{A1}$ ) and the extrinsic a posteriori LLRs  $L^{E1}$  will be a priori LLR-values  $L^{A2}$  of the channel decoder, i.e.,  $L^{E1} = L^{A2}$  (see Figure 2.1).

Different types of channel codes and corresponding SISO decoding algorithms exist in the literature. The most prominent variants are reviewed in Chapter 5 together with corresponding VLSI implementation results.

## 2.2 The Basics of MIMO Detection

In Section 2.2.1, we review hard-output MIMO detection algorithms. The basics of soft-input soft-output MIMO detection algorithms are described in Section 2.2.2.

### 2.2.1 Hard-Output MIMO Detection

Coherent hard-output MIMO detection algorithms compute estimates of the transmitted symbol vector  $\hat{\mathbf{s}}$ . Estimates of the transmitted bits are obtained by remapping the computed symbol-vector estimate  $\hat{\mathbf{s}}$  to

$<sup>^5\</sup>rm Note that if interleaving is used, the LLRs need to be de-interleaved at the input and interleaved at the output of the channel decoder.$

its corresponding bit-labels according to

$$\hat{x}_{i,b} = [\hat{s}_i]_b, \quad i = 1, \dots, M_{\mathrm{T}}, \quad b = 1, \dots, Q$$

where  $[\hat{s}_i]_b$  stands for the *b*th bit in the label of  $\hat{s}_i$ . In the following, hard-output MIMO detection schemes (ranging from optimum (errorrate) performance to low computational complexity) are reviewed and the associated performance is compared based on numerical simulation results.

### Maximum a Posteriori and Maximum-Likelihood Detection

The optimal hard-output MIMO detector (in terms of minimizing the probability that the computed estimate does not correspond to the transmitted symbol vector  $\mathbf{s}'$ ) is referred to as the maximum a posteriori (MAP) detector and corresponds to

$$\hat{\mathbf{s}}^{\text{MAP}} = \underset{\mathbf{s}\in\mathcal{O}^{M_{\text{T}}}}{\arg\max} P[\mathbf{s}' = \mathbf{s} \,|\, \mathbf{y}, \mathbf{H}]$$

(2.3)

where  $\hat{\mathbf{s}}^{\text{MAP}}$  is referred to as the MAP estimate. Bayes's theorem applied to (2.3) leads to the following equivalent formulation of the MAP detection rule

$$\hat{\mathbf{s}}^{\text{MAP}} = \underset{\mathbf{s}\in\mathcal{O}^{M_{\text{T}}}}{\arg\max} \left\{ p(\mathbf{y} \mid \mathbf{s}' = \mathbf{s}, \mathbf{H}) \frac{P[\mathbf{s}' = \mathbf{s}]}{p(\mathbf{y})} \right\}$$

$$= \underset{\mathbf{s}\in\mathcal{O}^{M_{\text{T}}}}{\arg\max} \left\{ p(\mathbf{y} \mid \mathbf{s}' = \mathbf{s}, \mathbf{H}) P[\mathbf{s}' = \mathbf{s}] \right\}$$

(2.4)

where the second equality results from the fact that  $p(\mathbf{y})$  does not depend on **s**. Due to the assumptions made on the noise statistics (see Section 2.1.2), the PDF  $p(\mathbf{y} | \mathbf{s}' = \mathbf{s}, \mathbf{H})$  in (2.4) corresponds to the joint probability density function of a multi-variate complex Gaussian with i.i.d. circularly symmetric components (each having variance  $N_{\rm o}$ ) with mean  $\mathbb{E}[\mathbf{y}] = \mathbf{Hs}$ , i.e.,

$$p(\mathbf{y} | \mathbf{s}' = \mathbf{s}, \mathbf{H}) = \frac{1}{(\pi N_o)^{M_R}} \exp\bigg(-\frac{\|\mathbf{y} - \mathbf{Hs}\|^2}{N_o}\bigg).$$

Since  $\log(x)$  is monotonically increasing in x, maximizing the logarithm of (2.4) is equivalent; this leads to the well-known MAP detection rule for MIMO systems [28–32, 48]

$$\hat{\mathbf{s}}^{\text{MAP}} = \underset{\mathbf{s}\in\mathcal{O}^{M_{\text{T}}}}{\arg\min} \left\{ \frac{\|\mathbf{y} - \mathbf{Hs}\|^2}{N_{\text{o}}} - \log \mathbf{P}[\mathbf{s}' = \mathbf{s}] \right\}.$$

(2.5)

If all transmit symbol vectors are equally likely, the MAP solution (2.5) coincides with the maximum likelihood (ML) solution of the MIMO detection problem [3–5]

$$\hat{\mathbf{s}}^{\mathrm{ML}} = \underset{\mathbf{s} \in \mathcal{O}^{M_{\mathrm{T}}}}{\arg\min} \|\mathbf{y} - \mathbf{Hs}\|^2$$

(2.6)

which is a closest-vector problem (CVP); solving this problem is known to require high computational complexity [49]. Straightforward MIMO detection according to (2.5) or (2.6), by performing an exhaustive search over all possible transmit vectors, can lead to prohibitively high computational complexity. For example, MAP or ML detection in a MIMO system with  $M_{\rm T} = 4$  and 64-QAM modulation alphabet requires a comparison of  $|\mathcal{O}|^{M_{\rm T}} \approx 16.7 \cdot 10^6$  candidates. In order to avoid the prohibitive computational complexity associated with solving of (2.5) or (2.6), a variety of low-complexity MIMO detection schemes have been proposed in the past.

### Linear MIMO Detection

The most prominent low-complexity algorithms for MIMO detection belong to the class of linear detection (LD) schemes [3]. The main idea underlying LD is to invert the effect of the MIMO channel matrix. To this end, the MIMO detection problem is decomposed into  $M_{\rm T}$ single-antenna detection problems that can be solved with (often significantly) reduced complexity compared to that of MAP or ML detection. However, the decomposition in  $M_{\rm T}$  (independent) detection tasks leads, in general, to a significant performance loss. Corresponding simulation results are shown below.

**Zero-Forcing Detection** One of the simplest approaches to lowcomplexity MIMO detection is zero-forcing (ZF), which corresponds to left-multiplying the Moore-Penrose pseudo-inverse of the channel matrix  $\mathbf{H}^{\dagger} = (\mathbf{H}^{H}\mathbf{H})^{-1}\mathbf{H}^{H}$  to the received vector  $\mathbf{y}$  such that

$$\mathbf{H}^{\dagger}\mathbf{y} = \hat{\mathbf{y}}^{\mathrm{ZF}} = \mathbf{s} + \mathbf{H}^{\dagger}\mathbf{n}.$$

(2.7)

By ignoring the influence of colored noise in (2.7), detection can be performed *separately* for each transmit stream according to

$$\hat{s}_i^{\mathrm{ZF}} = \begin{bmatrix} \hat{y}_i^{\mathrm{ZF}} \end{bmatrix}_{\mathcal{O}}, \quad i = 1, \dots, M_{\mathrm{T}}$$

where  $[y]_{\mathcal{O}}$  denotes mapping of  $y \in \mathbb{C}$  to the nearest constellation point in  $\mathcal{O}$ , i.e.,

$$[y]_{\mathcal{O}} = \operatorname*{arg\,min}_{s \in \mathcal{O}} |y - s|.$$

Computing the pseudo-inverse and slicing are both of polynomial complexity (in  $M_{\rm T}$ ) and hence, ZF is a polynomial-time algorithm for MIMO detection. Note that in (2.7), interference from other streams is perfectly removed, i.e., ZF decomposes the MIMO detection problem in  $M_{\rm T}$  parallel single-stream problems. However, if the channel matrix is ill-conditioned, ZF leads to noise enhancement since the equalized noise  $\mathbf{H}^{\dagger}\mathbf{n}$  in (2.7) can get arbitrarily large [3]; this is the main cause of the poor error-rate performance realized by ZF detection.

**MMSE Detection** LD based on the MMSE criterion is a solution to trade noise enhancement for interference suppression. Instead of using the pseudo-inverse of the channel matrix, an  $M_{\rm T} \times M_{\rm R}$  estimator matrix **M** that fulfills the MMSE criterion

$$\mathbf{M} = \underset{\widetilde{\mathbf{M}} \in \mathbb{C}^{M_{\mathrm{T}} \times M_{\mathrm{R}}}}{\operatorname{arg\,min}} \mathbb{E} \Big[ \| \widetilde{\mathbf{M}} \mathbf{y} - \mathbf{s} \|^2 \Big]$$

(2.8)

is used for equalization. Note that expectation in (2.8) is over the noise and the symbol vectors. The solution of (2.8) corresponds to the well-known MMSE estimator matrix [3]

$$\mathbf{M} = \left(\mathbf{H}^{H}\mathbf{H} + \frac{M_{\mathrm{T}}}{\mathsf{SNR}}\mathbf{I}_{M_{\mathrm{T}}}\right)^{-1}\mathbf{H}^{H}.$$

(2.9)

Equalization of the MIMO input-output relation with (2.9) leads to

$$My = Hs + Mn$$

with  $\widetilde{\mathbf{H}} = \mathbf{M}\mathbf{H}$ . As noted in [50], the MMSE estimator in (2.9) is biased, i.e., the entries on the main-diagonal of  $\widetilde{\mathbf{H}}$  are, in general, not equal to one. An unbiased MMSE estimator can be obtained by extraction of the main-diagonal entries of  $\widetilde{\mathbf{H}}$  into a  $M_{\mathrm{T}} \times M_{\mathrm{T}}$  diagonal matrix

$$\mathbf{D} = \operatorname{diag}(\tilde{H}_{1,1}, \dots, \tilde{H}_{M_{\mathrm{T}},M_{\mathrm{T}}})$$

and by using the *unbiased* MMSE estimator matrix  $\widetilde{\mathbf{M}} = \mathbf{D}^{-1}\mathbf{M}$  instead of (2.9).

Analogous to ZF, linear (and unbiased) MMSE detection corresponds to the application of the unbiased MMSE estimator matrix  $\widetilde{\mathbf{M}}$  to the received vector  $\mathbf{y}$  according to

$$\widetilde{\mathbf{M}}\mathbf{y} = \hat{\mathbf{y}}^{\mathrm{MMSE}} = \mathbf{s} + \tilde{\mathbf{n}}$$

(2.10)

and detection is carried out by slicing  $\hat{y}_i^{\text{MMSE}}$  to the nearest constellation point in  $\mathcal{O}$  for  $i = 1, \ldots, M_{\text{T}}$ . The vector  $\tilde{\mathbf{n}}$  in (2.10) corresponds to the effective noise-plus-(self)-interference (NPI)

$$\tilde{\mathbf{n}} = \left(\mathbf{M}\mathbf{H} - \mathbf{I}_{M_{\mathrm{T}}}\right)\mathbf{s} + \mathbf{M}\mathbf{n}.$$

(2.11)

It is important to note that the NPI-term in (2.11) now contains self-interference, but suffers less from noise enhancement than ZF detection. The reason for reduced noise enhancement is due to the fact that the inversion in (2.9) is based on a regularized version of the Gram matrix  $\mathbf{H}^{H}\mathbf{H}$ , which is usually better conditioned than computation of the pseudo-inverse (as required for ZF). Thus, LD based on the MMSE criterion achieves, in general, better performance than ZF, while requiring a similar amount of computational complexity.

### Successive Interference Cancellation

Similar to LD, successive interference cancellation (SIC) decomposes the MIMO detection problem into  $M_{\rm T}$  single-stream detection problems. The key difference is that SIC performs detection in a sequential manner, i.e., one stream is detected after another while the result of the previously detected stream is used to cancel out interference in the subsequent detection steps. The detection process can be described conveniently using the QR-decomposition (QRD) of the MIMO channel matrix. In the sequel, the general case of SIC, i.e., including layer sorting and regularization, is described.

SIC starts by performing a column-sorted QRD of a regularized version of the channel matrix

$$\begin{bmatrix} \mathbf{H} \\ \alpha \mathbf{I}_{M_{\mathrm{T}}} \end{bmatrix} \mathbf{P} = \mathbf{Q} \mathbf{R}$$

(2.12)

where  $\alpha$  is a suitably chosen regularization parameter,  $\mathbf{P}$  is a  $M_{\mathrm{T}} \times M_{\mathrm{T}}$ permutation matrix,  $\mathbf{Q}$  is a unitary  $(M_{\mathrm{R}} + M_{\mathrm{T}}) \times M_{\mathrm{T}}$  matrix and  $\mathbf{R}$  is of dimension  $M_{\mathrm{T}} \times M_{\mathrm{T}}$  and upper-triangular with non-negative realvalued entries on the main diagonal. Partitioning  $\mathbf{Q}$  according to  $\mathbf{Q} = \begin{bmatrix} \mathbf{Q}_{a}^{T} & \mathbf{Q}_{b}^{T} \end{bmatrix}^{T}$ , where  $\mathbf{Q}_{a}$  is of dimension  $M_{\mathrm{R}} \times M_{\mathrm{T}}$  and  $\mathbf{Q}_{b}$  is of dimension  $M_{\mathrm{T}} \times M_{\mathrm{T}}$ , and left multiplication of the received vector by  $\mathbf{Q}_{a}^{H}$ , leads to the input-output relation

$$\mathbf{Q}_{a}^{H}\mathbf{y} = \hat{\mathbf{y}}^{\mathrm{SIC}} = \mathbf{R}\tilde{\mathbf{s}} + \tilde{\mathbf{n}}$$

(2.13)

where  $\mathbf{P}\tilde{\mathbf{s}} = \mathbf{s}$  and the effective NPI vector is

$$\tilde{\mathbf{n}} = -\alpha \mathbf{Q}_b^H \mathbf{s} + \mathbf{Q}_a^H \mathbf{n}.$$

Note that  $\mathbf{Q}$  is unitary, but  $\mathbf{Q}_a$  and  $\mathbf{Q}_b$  will, in general, not be unitary. Hence, the effective NPI vector is no longer i.i.d. circularly symmetric complex Gaussian distributed with variance  $N_o$  per complex entry. In addition, since  $\mathbf{Q}_b$  is not an all-zero matrix if  $\alpha \neq 0$ , the NPI vector contains self-interference.

MIMO detection based on SIC now amounts to detect the  $M_{\rm T}$ th stream according to

$$\hat{s}_{M_{\mathrm{T}}}^{\mathrm{SIC}} = \left\lceil \frac{\hat{y}_{M_{\mathrm{T}}}^{\mathrm{SIC}}}{R_{M_{\mathrm{T}},M_{\mathrm{T}}}} \right\rfloor_{\mathcal{C}}$$

followed by successively detecting the remaining streams

$$\hat{s}_{i}^{\text{SIC}} = \left| \frac{1}{R_{i,i}} \left( \hat{y}_{i}^{\text{SIC}} - \sum_{j=i+1}^{M_{\text{T}}} R_{i,j} \hat{s}_{j}^{\text{SIC}} \right) \right|_{\mathcal{O}}, \quad i = M_{\text{T}} - 1, \dots, 1.$$

The procedure described above resembles the solution of linear equations using back-substitution, with the key difference that the substituted variables are being sliced to the nearest constellation symbols.

Various flavors of SIC have been proposed in the literature. The (error-rate) performance mainly depends on the choice of the regularization parameter  $\alpha$  and the column-sorting strategy. The bestperforming variant is the vertical Bell Laboratories layered spacetime (V-BLAST) algorithm [51,52], which originally employs multiple matrix inversions instead of a QRD. The original V-BLAST algorithm [51] does not use any regularization (i.e.,  $\alpha = 0$ ) and it performs column sorting such that the layer with largest post-equalization SNR is detected first. An improved algorithm (in terms of performance and complexity) was proposed in [53] and employs regularization according to the MMSE criterion, i.e.,  $\alpha = \sqrt{M_{\rm T}/{\rm SNR}}$ , and it processes spatial streams with highest post-equalization signal-to-noiseand-interference ratio (SINR) first.

A low-complexity alternative that approximates V-BLAST layer sorting is based on the sorted QR-decomposition (SQRD) algorithm as described in [54]. The performance of this algorithm can be improved by using regularization [55] as well. Note that SQRD-based SIC requires lower computational complexity compared to inversionbased V-BLAST algorithms (see, e.g., [56]).

### Lattice-Reduction-Aided MIMO Detection

A promising approach for high-performance and low-complexity hardoutput MIMO detection is based on a mathematical tool known as lattice reduction (LR). The general idea of LR-aided MIMO detection is to relax the ML detection problem to a CVP on the infinite lattice. Then, a CVP is solved on a "more orthogonal" lattice basis, which leads to performance improvements in combination with lowcomplexity detection methods, such as LD or SIC. The basic idea of LR-aided MIMO detection is summarized below.

**Transformation to Lattices** In order employ techniques from lattice theory to MIMO detection, we start by mapping the elements  $s \in \mathcal{O}$  to elements  $x \in \mathbb{CZ}$  using the transformation x = as + c. The constants  $a \in \mathbb{R}$  and  $c \in \mathbb{C}$  with a > 0 are independent of s and chosen such that  $x \in \mathcal{X} \subset \mathbb{CZ}$  with  $|\mathcal{X}| = |\mathcal{O}|$  and

$$\mathcal{X} = \left\{ x \in \mathbb{CZ} \, | \, (k_{\min} \le \Re\{x\} \le k_{\max}) \\ \wedge \, (k_{\min} \le \Im\{x\} \le k_{\max}) \right\}$$

(2.14)

where  $k_{\min}, k_{\max} \in \mathbb{Z}$ . Note that (2.14) can be used to check whether  $x' \in \mathbb{CZ}$  is in  $\mathcal{X}$  by performing separate boundary checks for the real and imaginary part of  $x'^{.6}$ . The transmit vectors  $\mathbf{s} \in \mathcal{O}^{M_{\mathrm{T}}}$  can be mapped to vectors  $\mathbf{x} \in \mathcal{X}^{M_{\mathrm{T}}} \subset (\mathbb{CZ})^{M_{\mathrm{T}}}$  according to

$$\mathbf{x} = a\mathbf{s} + \mathbf{c} \tag{2.15}$$

where  $\mathbf{c} = c \mathbf{1}_{M_{\mathrm{T}}}$ . The inverse transformation associated with (2.15) is given by  $\mathbf{s} = a^{-1}(\mathbf{x} - \mathbf{c})$ . The input-output relation in (2.2) can now be transformed into

$$\mathbf{r} = \mathbf{G}\mathbf{x} + \mathbf{n} \tag{2.16}$$

where  $\mathbf{G} = a^{-1}\mathbf{H}$  and  $\mathbf{r} = \mathbf{y} + \mathbf{G}\mathbf{c}$  is a translated version of the received vector  $\mathbf{y}$ . The essence of the transformation of (2.2) into (2.16) is that now the received vector  $\mathbf{r}$  can be interpreted as a lattice point  $\mathbf{u} \in \mathcal{L}(\mathbf{G})$  that has been translated by the additive Gaussian noise vector  $\mathbf{n}$ . Here,

$$\mathcal{L}(\mathbf{G}) \triangleq \left\{ \mathbf{G} \mathbf{x} \, | \, \mathbf{x} \in \mathcal{X}^{M_{\mathrm{T}}} \right\}$$

(2.17)

denotes the finite lattice generated by **G**.

**Relaxation and Lattice Reduction** After carrying out the transformation to the lattice  $\mathcal{L}(\mathbf{G})$ , ML-detection (MLD) for (2.16) corresponds to

$$\hat{\mathbf{u}}^{\mathrm{ML}} = \operatorname*{arg\,min}_{\mathbf{u}\in\mathcal{L}(\mathbf{G})} \|\mathbf{r} - \mathbf{u}\|^2 \tag{2.18}$$

which amounts to solving a CVP in the finite lattice  $\mathcal{L}(\mathbf{G})$ . Since each lattice point in  $\mathcal{L}(\mathbf{G})$  is associated with a transmit vector in  $\mathcal{X}^{M_{\mathrm{T}}}$

$<sup>^{6}\</sup>mathrm{In}$  the case of non-square QAM constellations the boundary checks take a slightly more complicated form.

according to the relation  $\mathbf{u} = \mathbf{G}\mathbf{x}$ , the ML-estimate  $\hat{\mathbf{u}}^{\text{ML}}$  obtained by solving (2.18) can be transformed into<sup>7</sup>  $\hat{\mathbf{x}}^{\text{ML}} = \mathbf{G}^{\dagger} \hat{\mathbf{u}}^{\text{ML}}$ , which upon inversion of (2.15) yields the ML-estimate  $\hat{\mathbf{s}}^{\text{ML}}$  in (2.6).

The key requirement to employ LR for detection is to relax the finite lattice in (2.17) to the *infinite* lattice<sup>8</sup>

$$\underline{\mathcal{L}}(\mathbf{G}) \triangleq \left\{ \mathbf{G}\underline{\mathbf{x}} \,|\, \underline{\mathbf{x}} \in (\mathbb{CZ})^{M_{\mathrm{T}}} \right\}$$

(2.19)

and to compute an equivalent and "more orthogonal" basis for the lattice  $\underline{\mathcal{L}}(\mathbf{G})$  with the generator matrix  $\mathbf{B} = \mathbf{GT}$ , where  $\mathbf{T}$  is an  $M_{\mathrm{T}} \times M_{\mathrm{T}}$ unimodular matrix, i.e.,  $|\det(\mathbf{T})| = 1$  with  $T_{i,j} \in \mathbb{CZ} \ (\forall i, j)$ . Thanks to the unimodularity of  $\mathbf{T}$ , we have  $\underline{\mathcal{L}}(\mathbf{B}) = \underline{\mathcal{L}}(\mathbf{G})$ . It is important to note that this equivalence only holds for infinite lattices, in contrast to finite lattices where, in general,  $\mathcal{L}(\mathbf{B}) \neq \mathcal{L}(\mathbf{G})$ .

**LR-Aided MIMO Detection** LR-aided MIMO detection is then performed on the relaxed and reduced lattice  $\underline{\mathcal{L}}(\mathbf{B})$  by computing

$$\underline{\hat{\mathbf{u}}}^{\mathrm{ML}} = \arg\min_{\underline{\mathbf{u}}\in\underline{\mathcal{L}}(\mathbf{B})} \|\mathbf{r} - \underline{\mathbf{u}}\|^2$$

(2.20)

followed by compensating the transformation caused by the unimodular matrix according to  $\mathbf{T}\underline{\hat{\mathbf{u}}}^{\mathrm{ML}} = \underline{\hat{\mathbf{x}}}^{\mathrm{ML}}$ . Since the resulting estimate  $\underline{\hat{\mathbf{x}}}^{\mathrm{ML}}$  is not necessarily in  $\mathcal{X}^{M_{\mathrm{T}}}$ , remapping onto  $\mathcal{X}^{M_{\mathrm{T}}}$  is required whenever  $\underline{\hat{\mathbf{x}}}^{\mathrm{ML}} \notin \mathcal{X}^{M_{\mathrm{T}}}$ . Quantization of  $\underline{\hat{x}}_{i}^{\mathrm{ML}}$  to the nearest constellation point in  $\mathcal{X}$  ( $\forall i$ ) is the "common" approach for remapping used in the literature [57, 58].

Approximating (2.20) using low-complexity detection algorithms, such as LD or SIC, results in often significant performance improvements compared to LD or SIC without relaxation and LR [57, 59]. Unfortunately, remapping of  $\hat{\mathbf{x}}^{\text{ML}}$  onto  $\mathcal{X}^{M_{\text{T}}}$  if  $\hat{\mathbf{x}}^{\text{ML}} \notin \mathcal{X}^{M_{\text{T}}}$  entails, in general, a significant performance loss (in terms of an SNR gap) compared to ML performance. Regularization of the channel matrix can reduce this performance gap up to a certain extent [58]. However, the only way to mitigate the performance loss associated with relaxation

<sup>&</sup>lt;sup>7</sup>Note that  $\mathbf{G}^{\dagger}$  does not have to be computed explicitly as  $\mathbf{u}$  in (2.18) can be replaced by  $\mathbf{G}\mathbf{x}$  and the minimization can be performed over  $\mathbf{x} \in \mathcal{X}^{M_{\mathrm{T}}}$ .

$<sup>^{8}\</sup>mathrm{In}$  the remainder of this section, underlined quantities refer to the infinite-lattice case.

is to solve a finite-lattice CVP [25]; this again results in high computational complexity. Generally speaking, LR-aided MIMO detection seems to be better suited for use in combination with low-complexity hard-output detectors, such as LD or SIC, with overall sub-optimal performance.

### Performance of Hard-Output MIMO Detection

**Diversity Gain** A fundamental performance measure of MIMO detection algorithms is the *diversity gain d*, which refers to the asymptotic slope of the error probability as the SNR goes to infinity, i.e., [5]

$$d \triangleq -\lim_{\mathsf{SNR}\to\infty} \frac{\log\left(\mathsf{P}_{\mathsf{e}}(\mathsf{SNR})\right)}{\log(\mathsf{SNR})} \tag{2.21}$$

where  $P_e(SNR)$  denotes the average (over noise and channel realizations) error probability of the considered MIMO detector. A large diversity gain is desirable since it ensures that the error rate decreases faster for increasing SNR values than it would for a detector with a low diversity gain.

For MIMO systems employing spatial multiplexing in i.i.d. (across space) Rayleigh fading channels, the optimum diversity gain is attained by MLD (2.6) and it corresponds to  $d = M_{\rm R}$  [60, 61]. The diversity gain of ZF- and MMSE-based linear detection was shown to be  $d = M_{\rm R} - M_{\rm T} + 1$ , which is worse compared to that of MLD [61]. SIC yields, in general, better performance than linear detection schemes, but it achieves the *same* diversity gain as LD, irrespective of the employed column-ordering strategy and regularization [62]. Hence, the diversity gain for LD and SIC can only be improved by using more receive than transmit antennas.

The performance of LR-aided hard-output MIMO detection fundamentally differs from LD or SIC. In [63] it was shown that LR through the Lenstra, Lenstra, and Lovász (LLL) algorithm [64] followed by LD achieves the same diversity gain as MLD. Naive lattice decoding<sup>9</sup> was shown to achieve the same diversity gain as MLD, while leading to an unbounded SNR gap (growing logarithmically in SNR)

<sup>&</sup>lt;sup>9</sup>Naive lattice decoding [65] refers to ML decoding on the infinite lattice and to declaring an error whenever the relaxed estimate  $\hat{\mathbf{x}}$  does not belong to  $\mathcal{X}^{M_{\mathrm{T}}}$ .

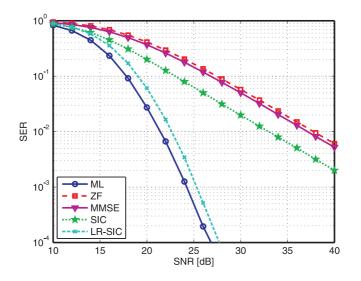

Figure 2.2: Symbol error rate (SER) performance of various MIMO detection schemes.

for  $M_{\rm R} = M_{\rm T}$  [65]. We finally note that the true performance of LR-aided detection strongly depends on the remapping strategy [25].

Numerical Performance Since the diversity gain only characterizes the asymptotic performance behavior of MIMO detection schemes, numerical performance results using symbol (vector) error rate (SER) are shown in Figure 2.2. The simulation results are for an *uncoded*  $M_{\rm T} = M_{\rm R} = 4$  MIMO system with 16-QAM symbol constellation. The entries of **H** are i.i.d. circularly symmetric complex Gaussian distributed with unit variance. For the LR-aided SIC detector (LR-SIC), lattice reduction has been carried out with a complex-valued version of the LLL algorithm [66] with  $\delta = 3/4$  using regularized (MMSE) SQRD preprocessing [55] and remapping to the finite lattice is done by using quantization [25, 55].

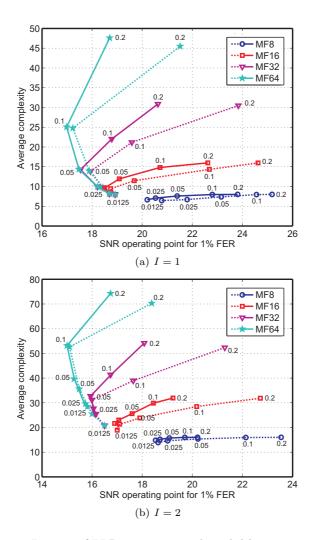

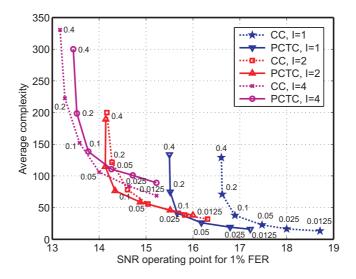

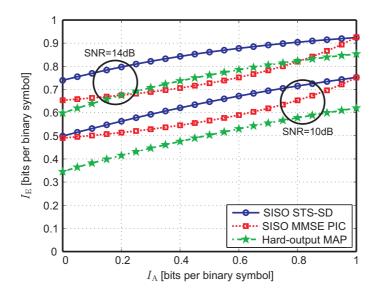

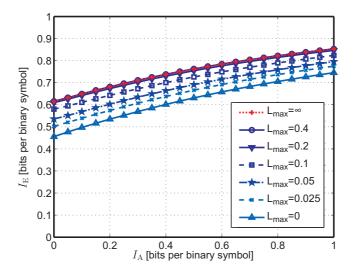

In Figure 2.2, the diversity gain of all MIMO detectors can be identified in the high-SNR regime. ML detection and LR-aided SIC yield the same 4th order diversity gain, whereas LR-aided SIC loses approximately 1.2 dB SNR (at SER= $10^{-2}$ ) to MLD. LD using ZF or MMSE show almost the same SER performance (and achieve only first order diversity), whereas regularized SIC using SQRD [55] yields approximately 4 dB SNR gain compared to MMSE-based LD. We conclude that it is essential to employ detection schemes that realize the maximum diversity gain, particularly in uncoded (or near rate-one coded) MIMO systems.