# **Experiences Using a Novel Python-Based Hardware Modeling Framework** for Computer Architecture Test Chips

### Abstract

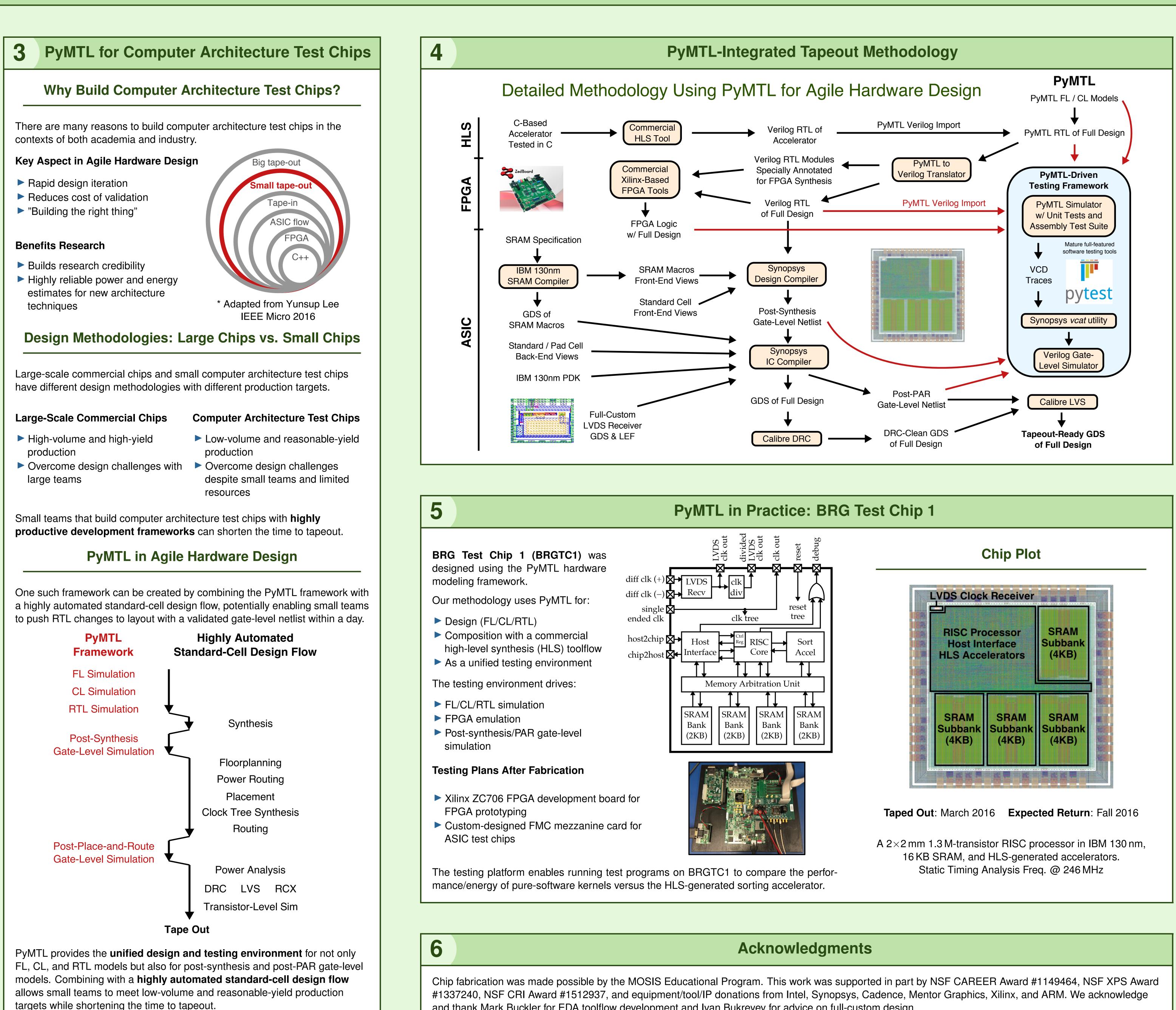

This poster will describe a taped-out  $2 \times 2 \text{ mm}$  1.3 M-transistor test chip in IBM 130 nm designed using our new Python-based hardware modeling framework. The goal of our tapeout was to demonstrate the ability of this framework to enable Agile hardware design flows.

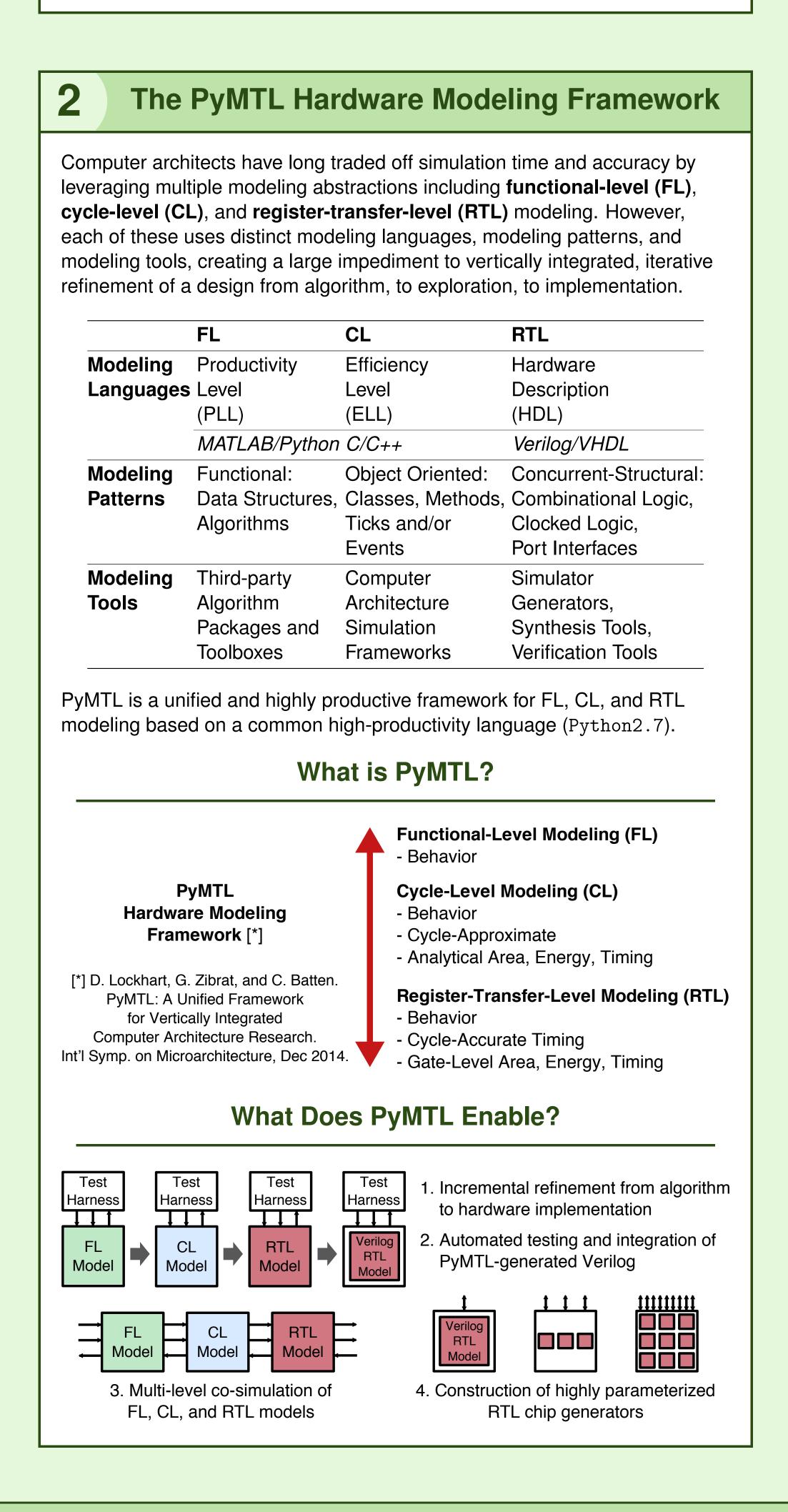

Specifically, our approach has two pieces:

**Unify** all simulation (behavioral, cycle-level timing, RTL, and gate-level) within a single-language development framework

Integrate this framework with highly automated standard-cell design flows For small teams working on small computer architecture test chips for research or as part of an Agile hardware design flow, such an approach can enable rapid design iteration from RTL to layout, shortening the time to tapeout despite limited manpower.

## Christopher Torng, Moyang Wang, Bharath Sudheendra, Nagaraj Murali, Suren Jayasuriya, Shreesha Srinath, Taylor Pritchard, Robin Ying, and Christopher Batten School of Electrical and Computer Engineering

**Cornell University**

and thank Mark Buckler for EDA toolflow development and Ivan Bukreyev for advice on full-custom design.